关于高电压界面的ESD解决方案的分析和介绍

描述

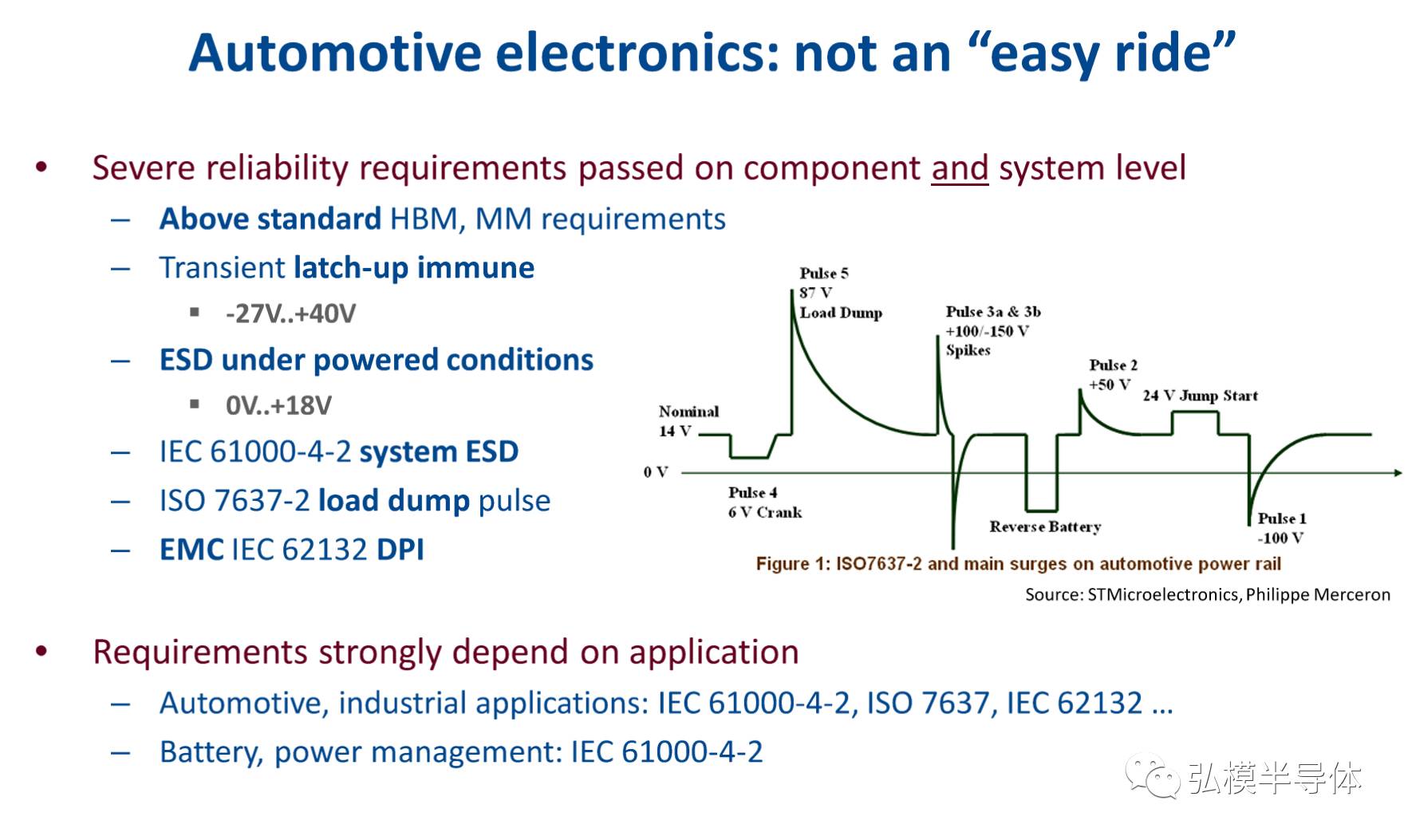

作为国内风起云涌的汽车产业, 由于其ZERO DEFECT和LONG LIFE的要求,尤其在苛刻的EMI/EOS工作特殊环境中,对ESD的方案变得更加挑剔。

同时, 更严格的芯片级别和系级别的测试接踵而至,当然这些要求也远远高于普通的HBM和IEC61000-4-2 ,另外其他的要求,比如ISO,EMC,Transient Latchup 等。

目前, 对于汽车电子这块,工艺主要集中在下面的半导体厂中,当然,根据客户的要求,ESD IP FAB TRANSFER也是完全可行的,而且TIME-TO-MARKET,性能,COST等方面,都会对客户原先方案有所提升。

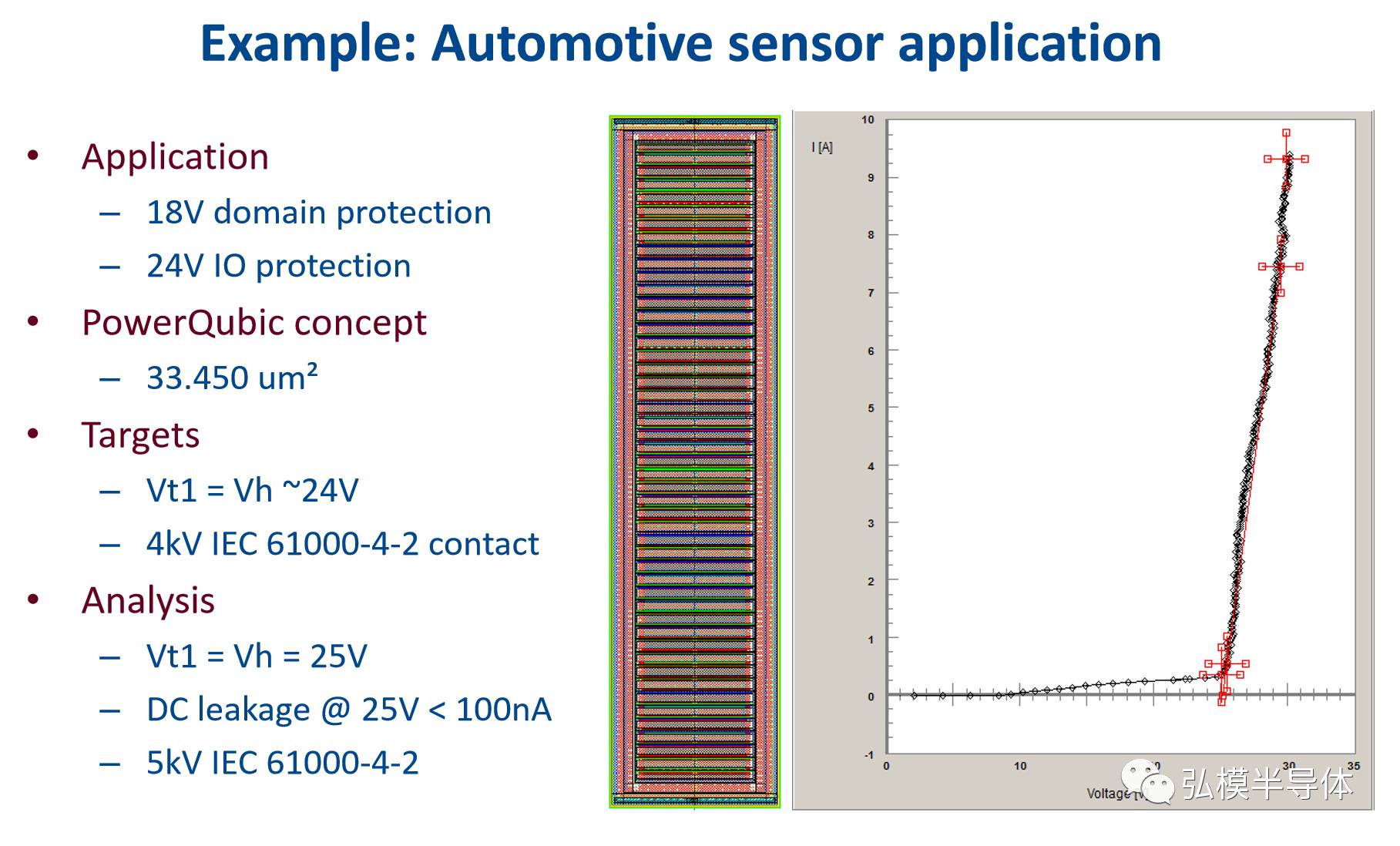

接下来, 我们来参考一下给不同客户的解决方案和测试结果:

对于很多客户来讲, 有些产品在系统级对IEC61000-4-2有要求, 一般大家都在OFF CHIP 上增加TVS器件, 同时,芯片级别也要求比较高的HBM SPEC。为了减少成本和良率,一方面可以尝试通过on-chip ESD来替代低级别的IEC61000-4-2的要求(比如小于3-4KV), 如果对IEC61000-4-2 有很高要求, 公司也可以进行私人定制,通过on-chip ESD的解决方案和验证来帮助客户。下面是一些案例和面积供大家参考。

Example: TSMC 180nm BCD – 24V interface

IEC 61000-4-2 contact discharge 8kV

Area: 37000 um²

Example: TSMC 130nm CMOS – 3.3V interface

Designed for 8kV HBM – Area: 2850 um²

Scaled to IEC 61000-4-2 contact discharge 15kV – Area: 18000 um²

Example: TSMC 55nm CMOS – 1.2V interface

Designed for 8kV IEC 61000-4-2

Area: 15000 um²

-

君耀电子的ESD防护解决方案2012-05-14 0

-

解读ESD静电抑制器2013-12-11 0

-

NFC天线的ESD解决方案2014-10-14 0

-

USB Type-C™:您的 ESD 解决方案是否保护端口?2017-01-04 0

-

计算宽输入电压解决方案的价值2018-08-29 0

-

高通道数JESD204B菊链可扩展时钟解决方案2018-12-28 0

-

I/O接口ESD静电防护解决方案2020-10-29 0

-

基于全新隔离技术的高电压系统解决方案2022-11-03 0

-

高灵活、八通道 ESD 解决方案(TI)2008-08-08 707

-

S08PT并且集成可配置恒流源及硬件式触感界面的触感式交钥匙解决方案2017-09-16 567

-

人机界面简单编程实例介绍2018-04-02 23071

-

关于On-chip ESD 资源的介绍和分析2019-09-08 3456

-

关于人工智能最佳交互界面的分析介绍2019-09-27 2210

-

液晶屏ESD防护解决方案2021-10-29 2138

全部0条评论

快来发表一下你的评论吧 !