关于非线性器件的建模与测试的分析和应用

描述

在快速发展、竞争激烈的非线性设计领域,能够用最短的时间将新器件技术转变为最终产品的能力是公司取得成功的关键。近来发展最好的方法是使用行为模型。此方法与相关测试测量方案的优点相结合,可以极大地缩短产品设计周期。本文将阐述一种专门的测量/建模解决方案,无论是简单的50欧姆系统级测试,还是需要波形工程的针对任意负载阻抗的全谐波特性描述,都可以进行表征。

测量基于多谐波失真 (PHD) 模型

近几年,随着大量成形的商用解决方案的发布,例如 Mesuro 的 Cardiff Model 系列,使得非线性器件的行为建模受到了极大的关注。

人们对此类模型的期望很高,但是,要想从这些模型中获得最大的帮助并准确地模拟器件的性能,就必须充分理解模型的工作原理和适用的条件。

三阶 PHD 模型,Cardiff Model Lite:

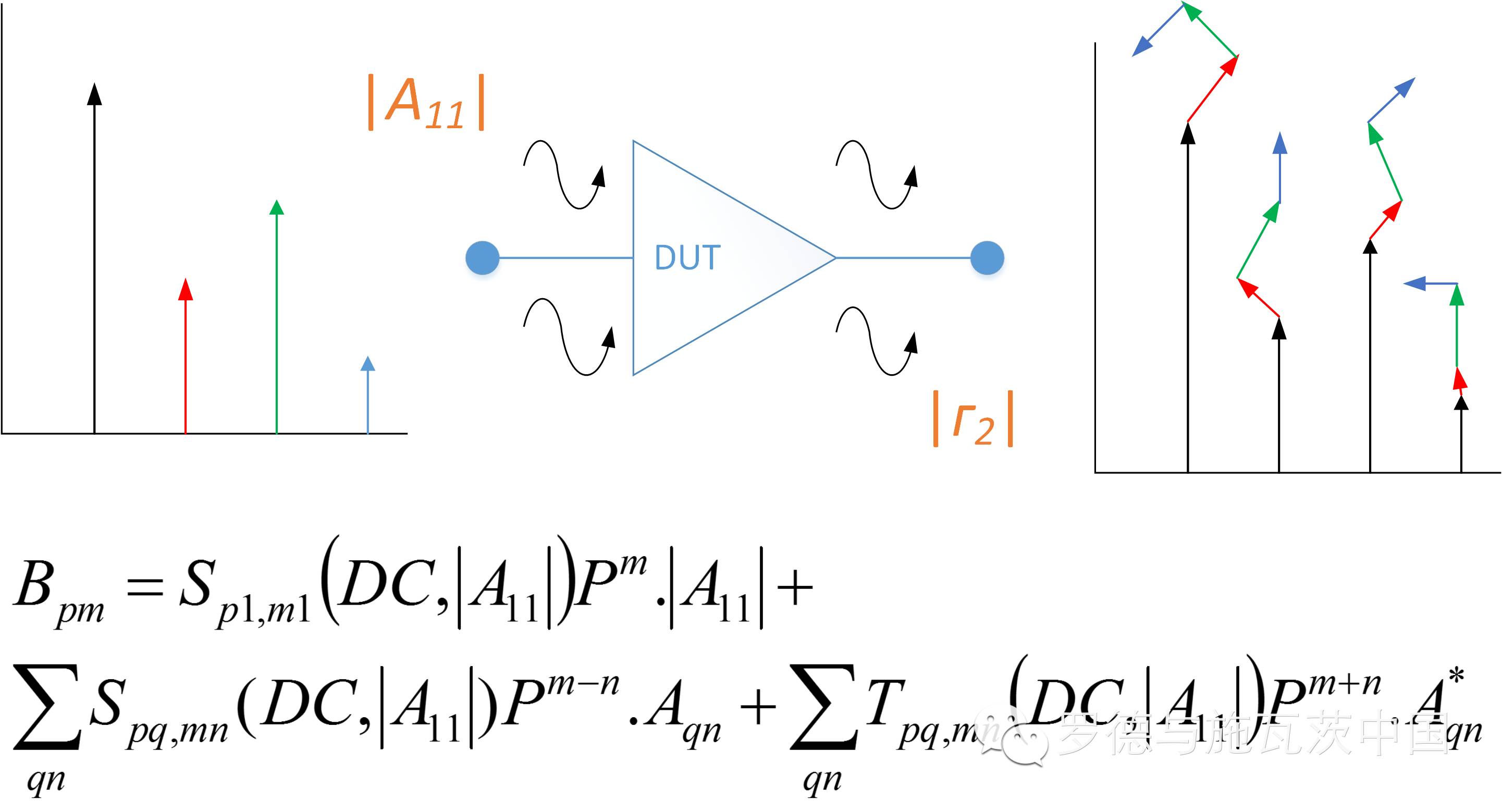

“Cardiff Model Lite”基于三阶多项式模型,允许在大信号情况下扩展 S 参数。它采用多谐波失真 (PHD) 行为模型公式 [1],如图 1 所示。它基于谐波叠加原理,此原理可以描述为激励“A”波 (Aqn) ,围绕大信号操作点 (LSOP) 进行线性映射,实现线性化的大信号“B”波 (Bpm) 响应。

图 1:PHD 模型多项式

DUT 首先由基波驱动,在本例中为 A11。在每个基波输入功率 (A11) 下,也会同时在各谐波频率下加入一个小信号对器件进行扰动(Aqn – 其中 q 表示端口序号,n 表示谐波阶数)。这可以通过网络分析仪中的第二个源实现。此信号源的相位通过至少 6 个不同的相位点进行扫描,以使模型正确地预测器件性能。使用 Mesuro CML 单元内提供的威廉希尔官方网站 ,可在器件两端完成此扰动处理。因此,对于每一个谐波分量,通过最小二乘拟合算法应用于测量数据,可以获得相应的模型参数 S 和 T。

所有三阶行为模型均为局部模型,仅适用于特定的操作条件如阻抗、偏差、温度等。只有正确地进行测量,模型才能在测量范围内高度准确的预测器件的性能,并作出正确的外推。请注意,必须谨慎对待外推,如果过度偏离测量的操作条件,此类模型会返回模棱两可的结果。最好是在 I-V 空间中考虑此外推过程(采用非数学方法!)。PHD 模型的提取过程需要在器件的输入和输出端激励基波和谐波的小信号,并且还要能够改变相位。

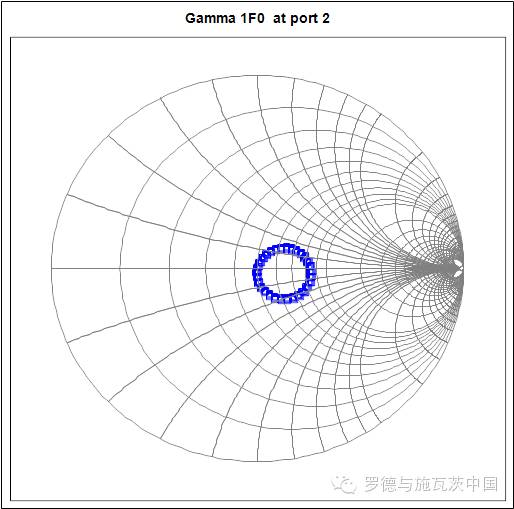

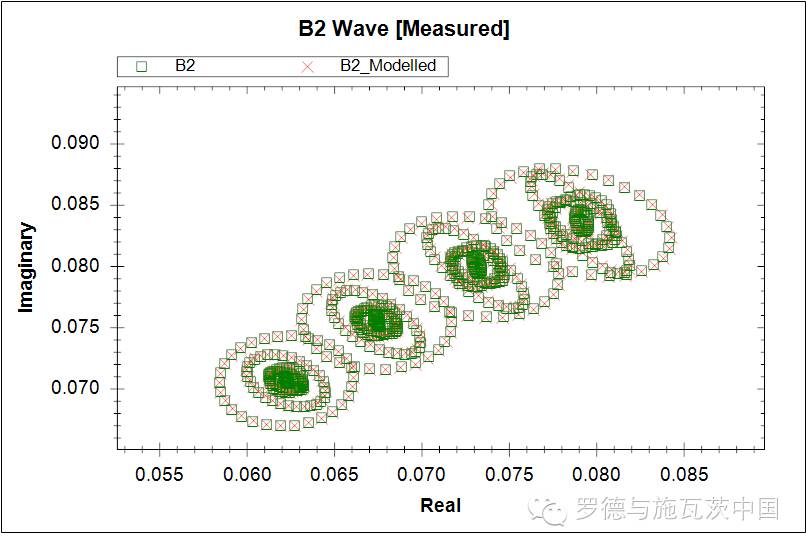

图 2: F0 扰动下的典型阻抗扫描

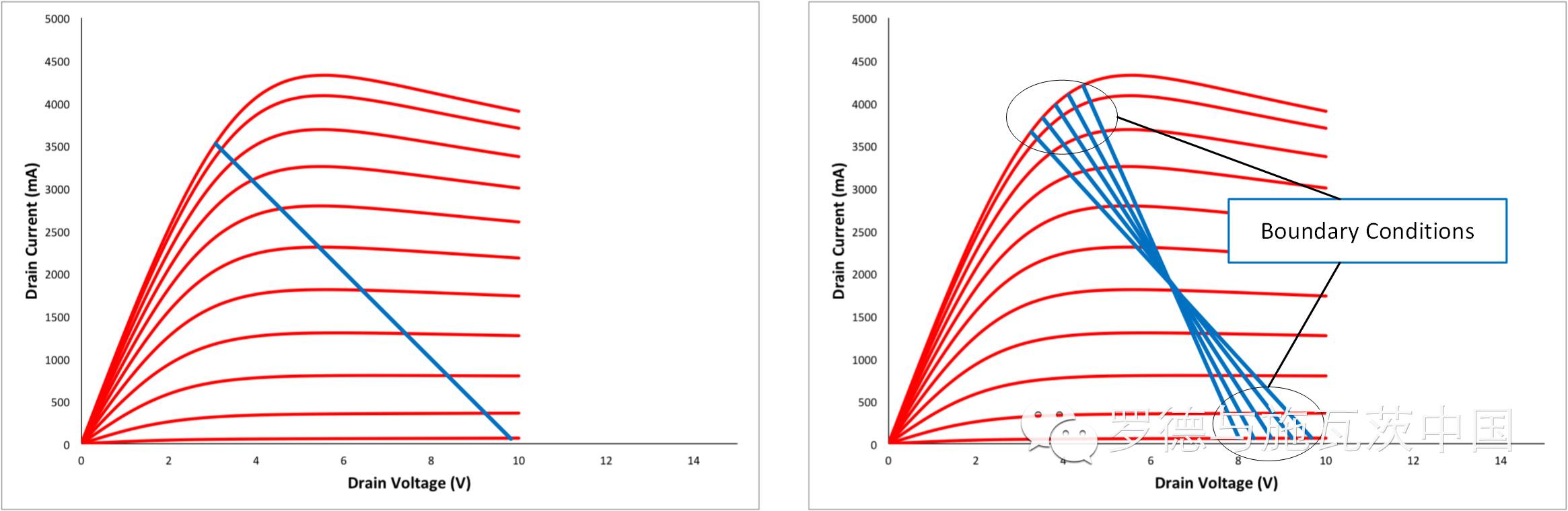

为简单起见,我们以基波为例,注入信号会导致阻抗发生变化,测量负载变化或 “负载牵引”的示例如图 2 所示。同时,利用图 3 所示的晶体管 I-V 曲线和 RF 负载线,就可以推测出图 3 左侧所示的系统阻抗下的压缩特性(标称阻抗 50 欧姆)。此时,改变负载,负载线就会上下移动,从而有效地“映射”如右图所示的器件边界特性。

图 3 - 阻抗为 50 欧姆和阻抗扫描时的负载线

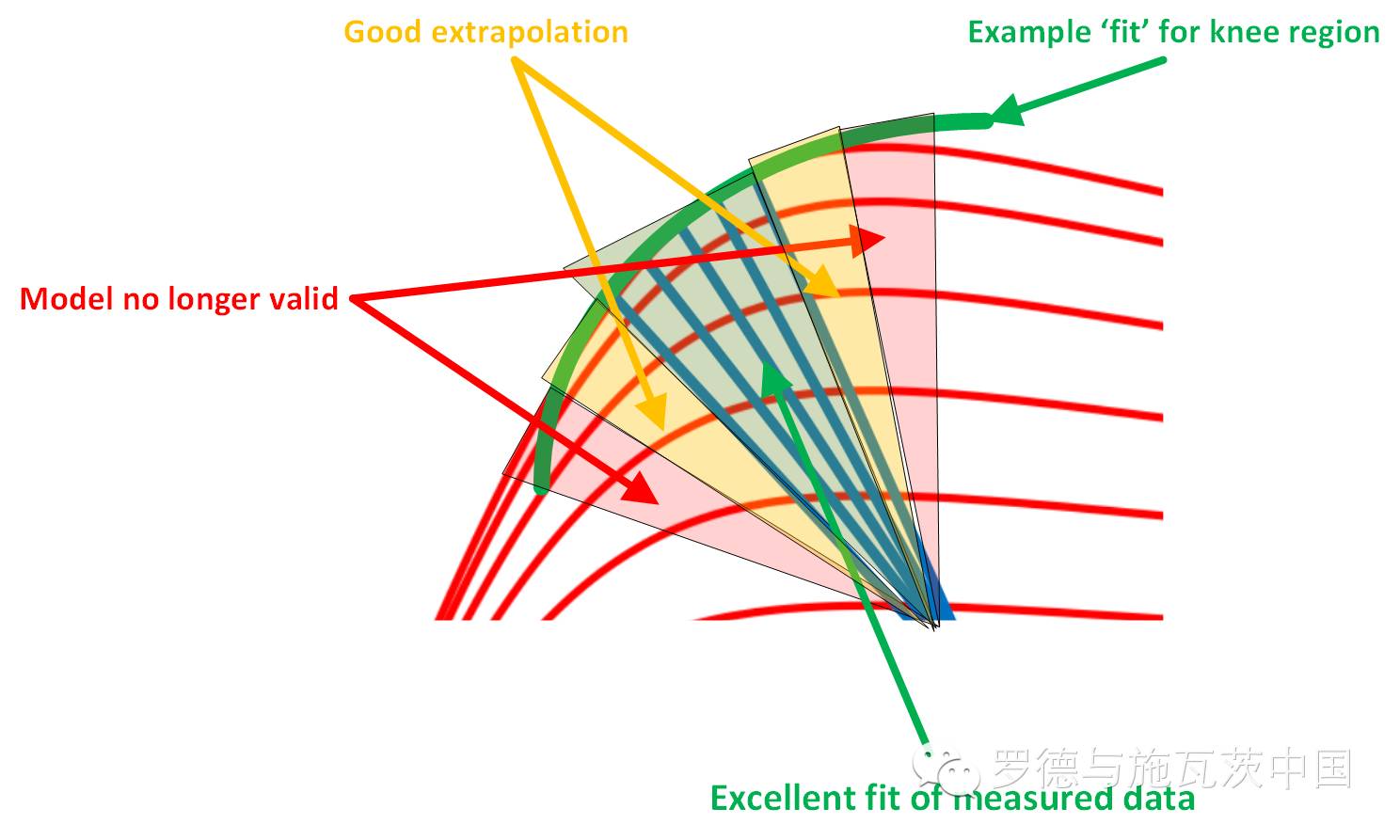

如果我们关注膝点区域,使用测量数据施加曲线拟合,就可以准确地对测量数据进行建模。少量外推会产生比较好的效果,但是,过多的外推会导致模型失效,如图 4 所示。

很明显,如果正确使用此模型,将会是模拟器获得非线性数据的卓越方法,同时应采用与 S 参数模型类似的方法来考虑此模型。采用与 S 参数类似的方法时,如果将细密网格用于频率和偏差,则模拟器的内推将产生良好的效果。典型应用是在系统级仿真时,对大量的“50 欧姆”器件进行串联,并分析它们的基波和谐波特性。类似技术也可用于负载阻抗,例如对功率晶体管建模来设计放大器;此内容将在“Cardiff Model+”部分详细探讨。

图 4 – 模型失效的膝区“拟合”示例

试验布置和测量

第一阶段是将只能进行线性测量的 VNA 转变为能够测量谐波相位关系的非线性 VNA。然后,将其用于重建时域波形。此时需要相位基准在扫描 VNA 频率时跟踪相位关系。Mesuro/Rohde & Schwarz 方法采用经调整处理的非线性设备,在基本频率下进行压缩测量。此设备与使用梳状谐波发生器(基于阶跃恢复二极管或非线性传输线)的其他商业产品不同,可以在较高频率下驱动。由于大部分能量集中在测量频率处,该方法可以改善谐波分量的表征,并且在参考器件的初始表征以及进行非线性测量时提供更大的动态范围。

对于谐波模型提取,需要额外的硬件发送和组合信号,以实现在器件的输入和输出端进行所需的扰动测量。Mesuro CML 单元(如图 5 所示)将相位基准和信号调节硬件集于一体,可以与任何 4 端口 R&S ZVA 矢网一起使用,并且可覆盖的频率范围可达 67GHz。

图 5 - Mesuro CML 硬件

Mesuro CML 发生器的软件套件(请参见图 6 和图 7)可以进行非常方便的设置和灵活测量,从而得到最佳模型。特色功能包括:

器件预表征测量,让用户更好的了解提取的关键参数。

相位点数的灵活性。

独立控制扰动信号的幅度大小 - 对各谐波进行源功率校准。

后期分析工具可以显示实际的负载扰动和根据测量的数据集验证模型拟合的关键能力。

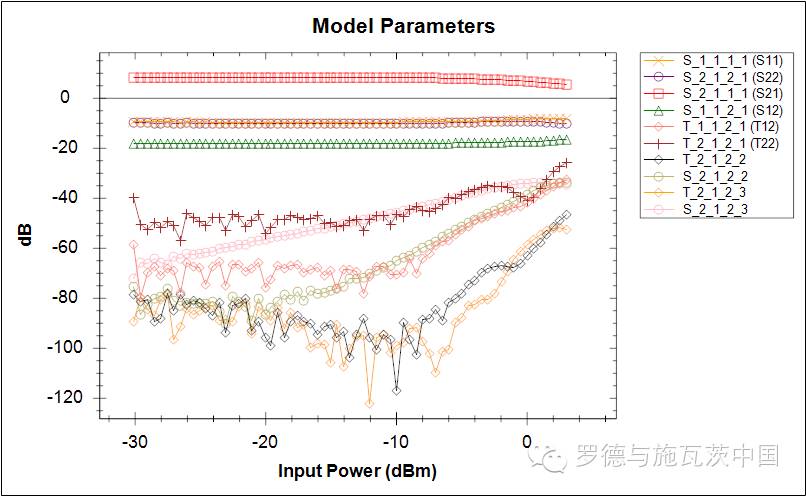

图 6:测量性能和建模性能之间的对比

图 7:提取的模型参数

负载牵引、波形工程和 Cardiff Model+

基于 VNA 的有源负载牵引架构

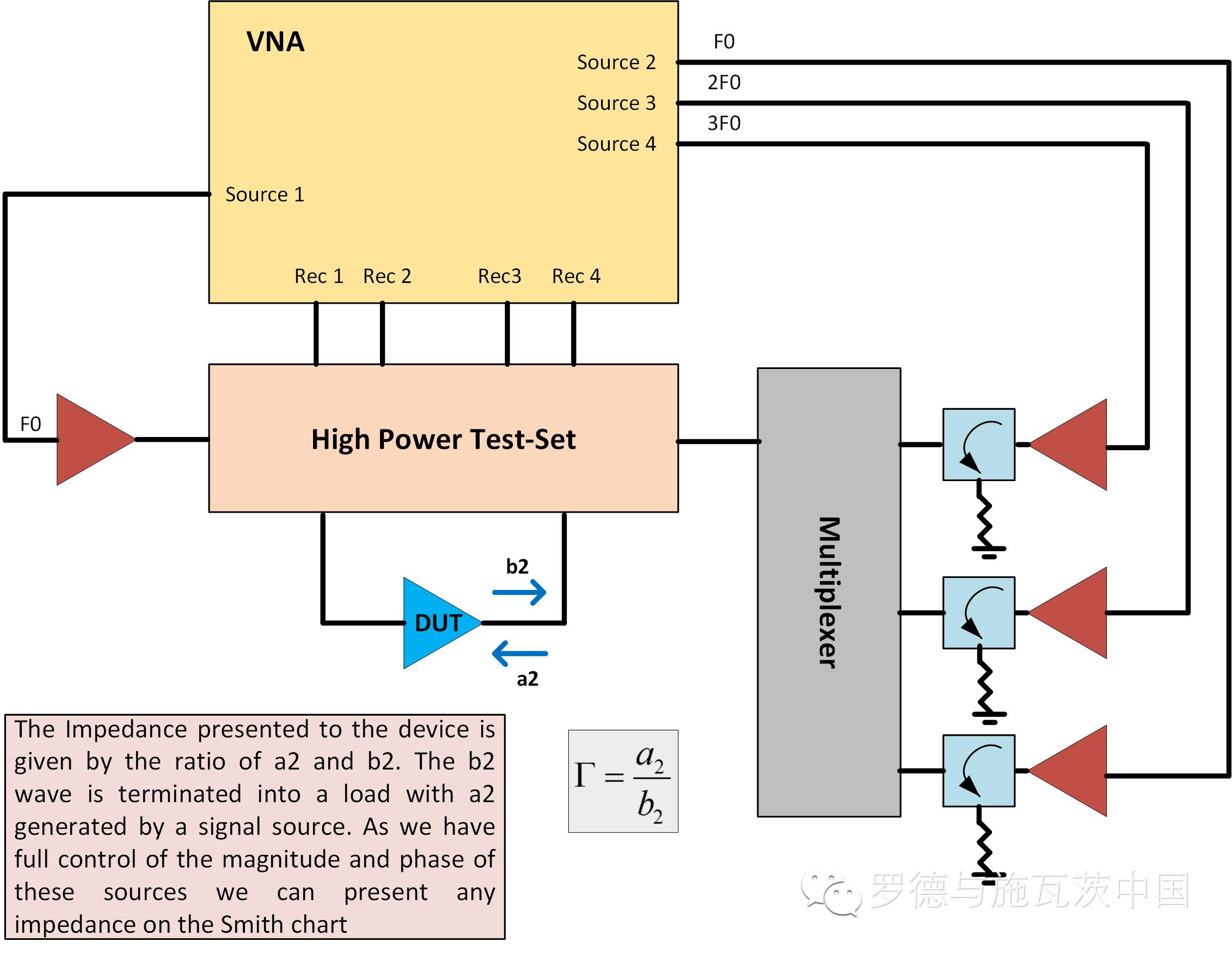

非线性器件不能总是只基于 50 欧姆的阻抗环境,而且与线性 S 参数不同,它无法将一个阻抗下测量的数据转换为另一阻抗下测量的数据。因此,为了获取必要的设计信息,需要对器件在不同阻抗下的特性全部进行测试,这导致测量集合显著增加。幸运的是上述 Cardiff Model Lite 系统中的相同“模型单元”可再次使用来实现功能更强的系统。通过添加额外的信号源和合路器,就可以使新系统能够在基波和谐波频率下进行阻抗控制。然后,通过偏置和阻抗变化,就可以利用得到的波形深入了解 DUT 特性或优化性能(波形工程)。开环有源谐波负载牵引系统的示意图如图 8 所示。

开环有源负载牵引 [2](如图 8 所示)是无源负载牵引技术 [3] 的替代选择, “a2”由相位同步信号源取代,反射信号的幅度和相位也可以综合改变。值得注意的是,每个谐波的控制需要单独的源。

图 8 - 开环谐波负载牵引示意图

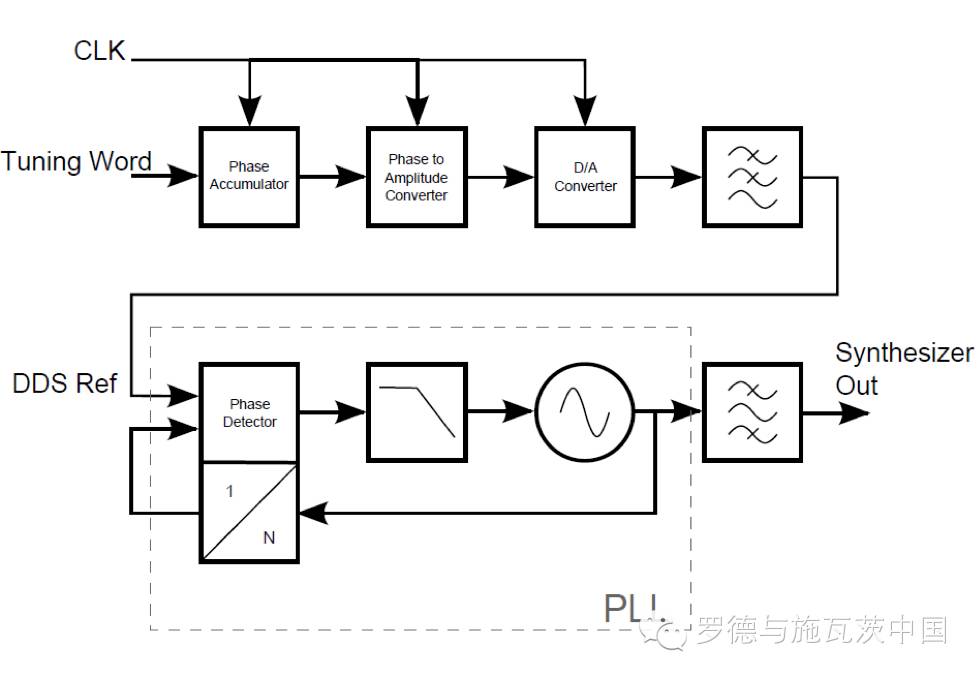

罗德与施瓦茨公司最新的矢量 网络分析仪能够完美地用于此方法,全新的ZVA 具有4个基于“直接数字合成 (DDS)”的源。这在许多方面都可以带来很大的好处。首先,在同时执行基次、二次和三次谐波负载牵引时,可以提供足够的源来驱动器件。此外,多个 DDS 源之间不会随着时间出现相位的相对漂移。

在图 9所示的 DDS 合成器中,调谐控制字定义相位变化的梯度以及 DDS 的频率。正弦波查找表将相位值重新转换为数字幅度值,例如,对于 16 位控制字,可以从 0 到 65536。再由 D/A 转换器得到正弦波;然后使用抗混叠低通滤波器滤波。此正弦波被用作鉴相器的参考信号。然后,PLL(锁相环)将 VCO(压控振荡器)的相位与参考信号锁定起来。这样就可以通过 DDS 信号设置 VCO 频率。

图 9 - 基于 DDS 的信号源

与采用模拟的 PLL 设计相比,此类源具有许多优势,包括改善相位噪声,提高频率捷变速度以及精确控制输出相位和频率等。由于用于下变频的本地振荡器和所有内部源均由 R&S ZVA 的同一个数字时钟驱动,因此,测量信号几乎没有漂移现象。

文献[4] 对此在 24 小时周期内进行了测试和验证展示。这个主要有两个好处。第一,它允许以更高的频率进行有源负载牵引,使用模拟 PLL 的源之间会产生漂移从而使有源负载牵引方法变得不可行。在基于 R&S ZVA 的方案中,Mesuro 已实现频率高达 60GHz的精确有源负载牵引。第二,由于 LO 也与信号发生器锁定在一起,可以实现不同扫描之间非常稳定的相位关系,从而使重构出来的波形不随时间发生变化。这意味着只需要在校准期间对相位基准进行确认,就允许在有源谐波负载牵引时使用ZVA所有的源。

有源负载牵引和波形工程的好处

上述有源负载牵引方法有很多好处,包括能够在史密斯圆图内外控制阻抗,减少系统占用面积以及最重要的提高测试速度。最近发表的论文 [5] 表明,使用相同的测量仪器和设置时,可将 100 点负载网格的测试速度减少7倍,即从 4.5 分钟缩短到只有 41 秒。该论文还展示了获得专利的准闭环架构,其在测量速度极其重要的情况下大有帮助,例如在生产环境中。此架构保持了开环方法的系统稳定性,同时进一步提高速度,相同的负载牵引测试时间缩短为只有 18.5 秒。

对于希望不仅仅改善负载牵引性能的人士来说,该系统也可用于测量和设计器件的时域电压和电流波形。此方法可以为设计师提供非常有价值的器件特性视角。波形工程主要有两个应用方向 [6],第一个应用是工艺开发方面,波形工程可用于确定工艺问题的根源 [7]。第二个应用是优化器件特性,无需迭代就能实现最好的设计[8-9]。

案例一 – 器件特性退化

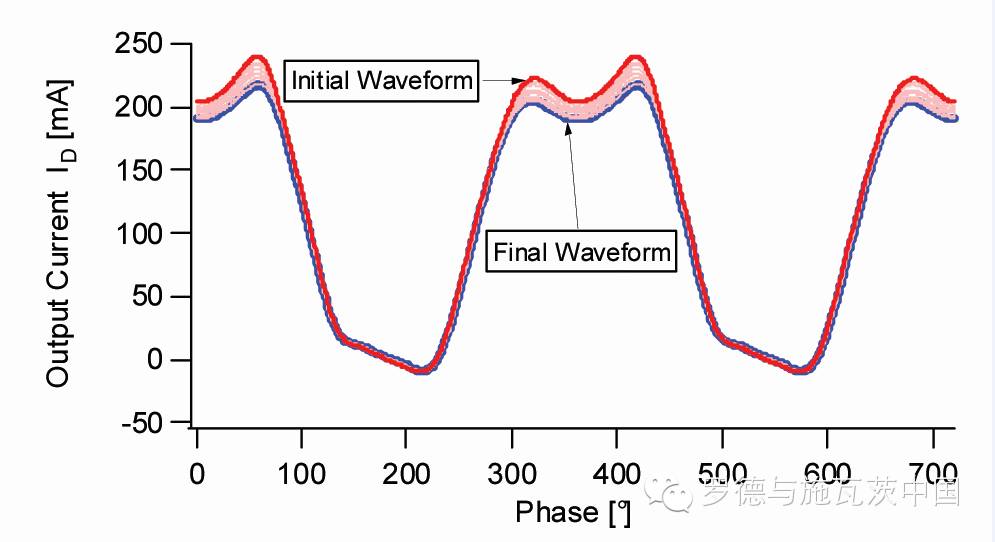

此案例[7] 将说明使用波形工程来分析出现特性退化的 GaN HFET 器件,通过结合 RF 和 DC 测量来分析问题的根本原因。图 10 所示为通过输出电流波形(叠加 100 个波形)观察到的退化现象,原始波形显示为红色,最终波形显示为蓝色。

图 10 – 显示退化的输出电流波形

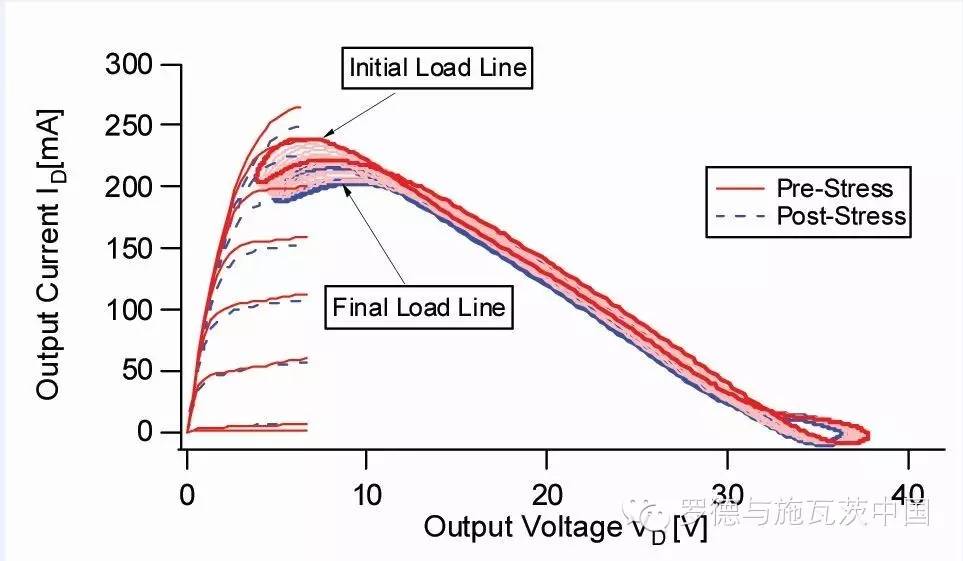

峰值电流明显减小,导致输出功率和效率降低。接下来进行应力测试,要完成此测试,首先在加电开启时进行 DC 和 RF 测量,然后在 90 分钟后再次进行 DC 和 RF 测量。图 11 所示为叠加 RF 负载线(通过根据输出电流绘制输出电压而形成)的 DCIV曲线,红色是初始时的测试值,应力测试后,在 RF 负载线和 DCIV 曲线中均可看出退化。

图 11 - RF 负载线和 DCIV 曲线预应力和后应力分析

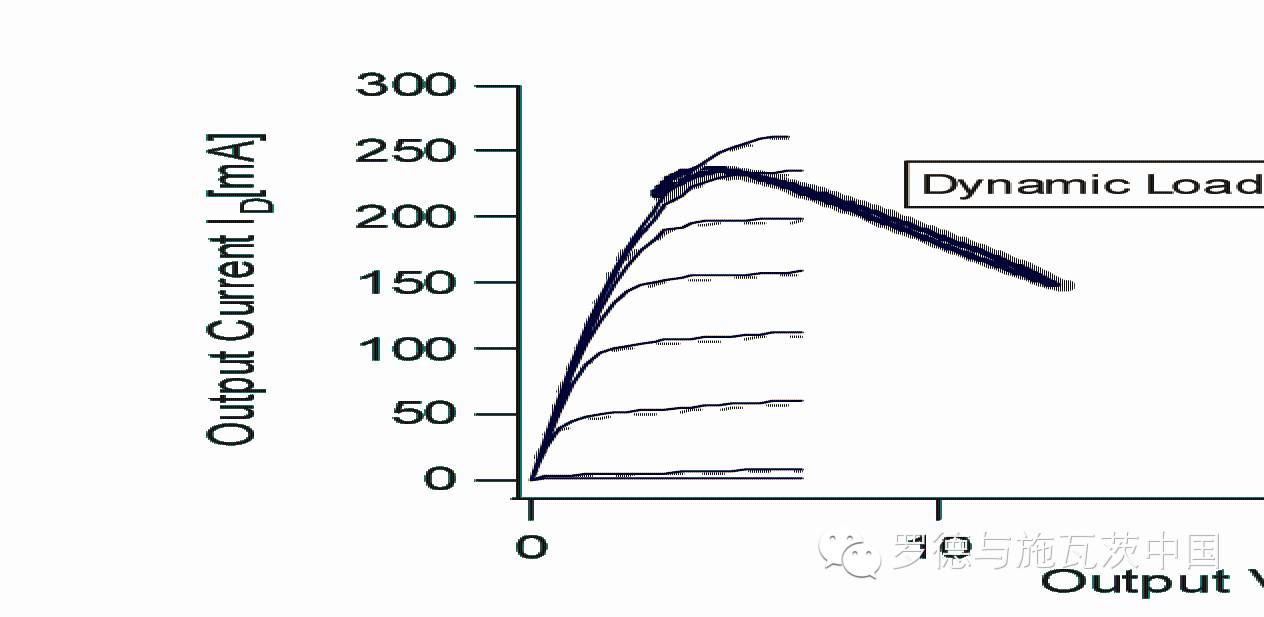

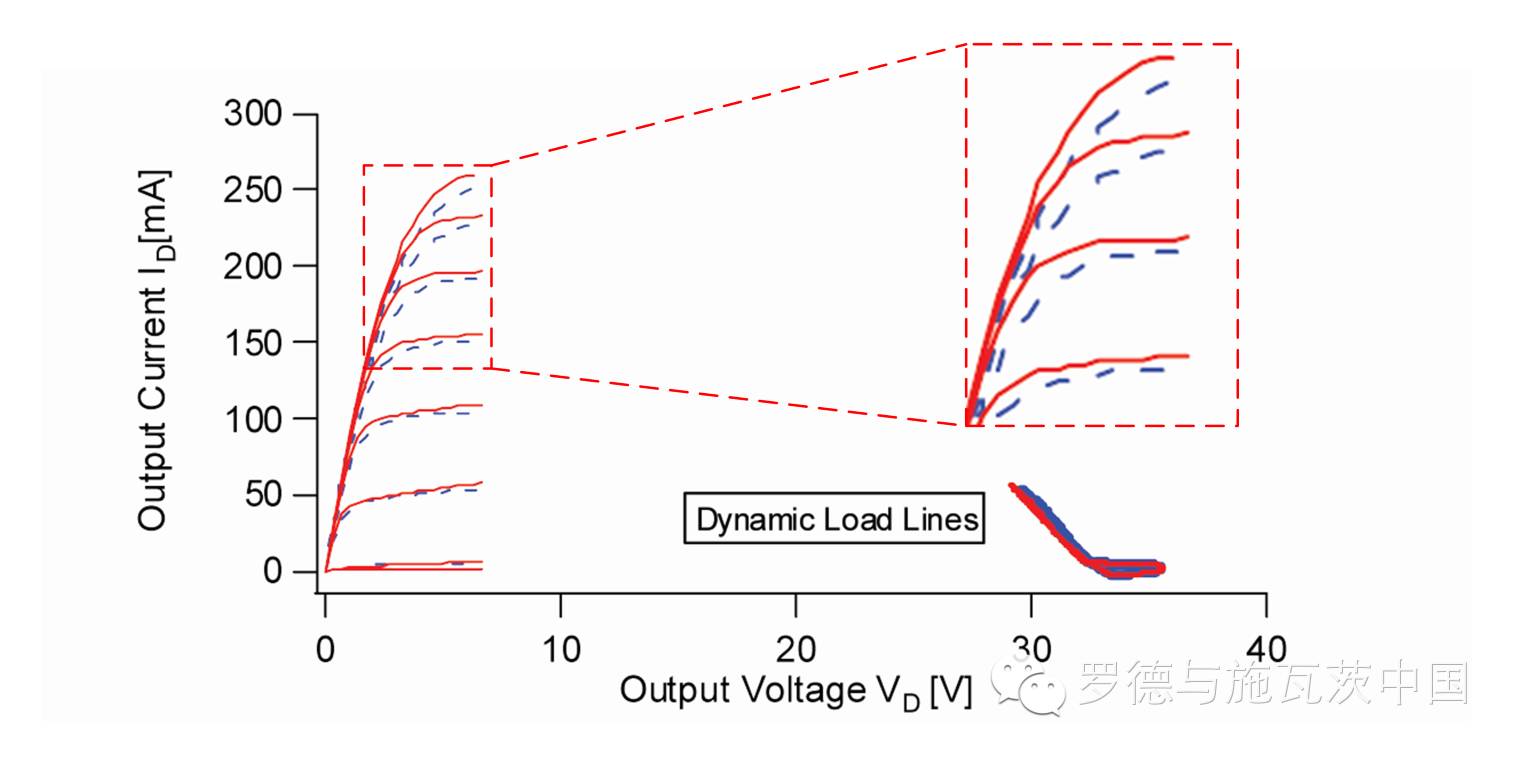

使用波形工程,可以只在器件的部分IV 区域进行表征。例如,通过将器件偏置在低漏极电压和高静态电流的工作状态,然后限制输入功率,就可以只表征 IV 曲线的高电流区域,如图 12 所示。相反地,通过将器件偏置在较高的漏极电压和低静态电流状态,可以只表征 IV 特性的高电压区域,如图 13 所示。在这两种情况下,尽管保持 RF输入功率不变,但是看一下 DCIV曲线,可以清楚的看到器件退化是由高电压区域内的强电场造成的,而非高电流产生的热效应造成的。了解这方面的信息后,工艺开发团队就可以定位问题所在,及时解决问题。

图 12 - 只高电流激励的应力测试

图 13 - 只高电压激励的应力测试

Cardiff Model+

上面已经展示了波形工程的重要作用,本节将说明如何利用更加高级的行为模型将设计过程移回到仿真器中。虽然行为建模技术(例如 X-Parameters)可以解决阻抗的问题,但对于每一个阻抗点,都需要创建大量的非线性模型数据,同时还需要在仿真器中进行大量的内插。相反地, Cardiff Model+ 多项式,尽管也是从 PHD 模型多项式衍生而来,却能够扩展多项式的阶数,使单个模型就可适用于所有阻抗情况 [10]。这样可以显著减小模型文件的大小。

案例研究 – Cardiff Model+

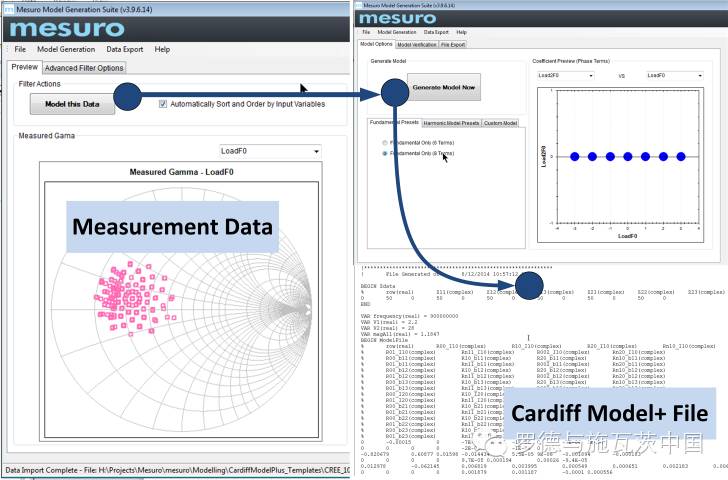

本案例展示了一个0.5W pHEMT 器件在9GHz 建模的过程和结果。在本例中,模型只针对谐波阻抗的一些固定集合,但也可根据需要包含在多项式中。一旦完成负载牵引测量,创建模型的过程就变得非常简单,将测试数据加载到模型生成软件,选择相应的模型类型,在本例中只选择基本模型,然后导出模型。模型文件还可以导出为适合 ADS 或 Microwave Office 软件使用的格式,如图 14 所示。

图 14 - 模型生成软件

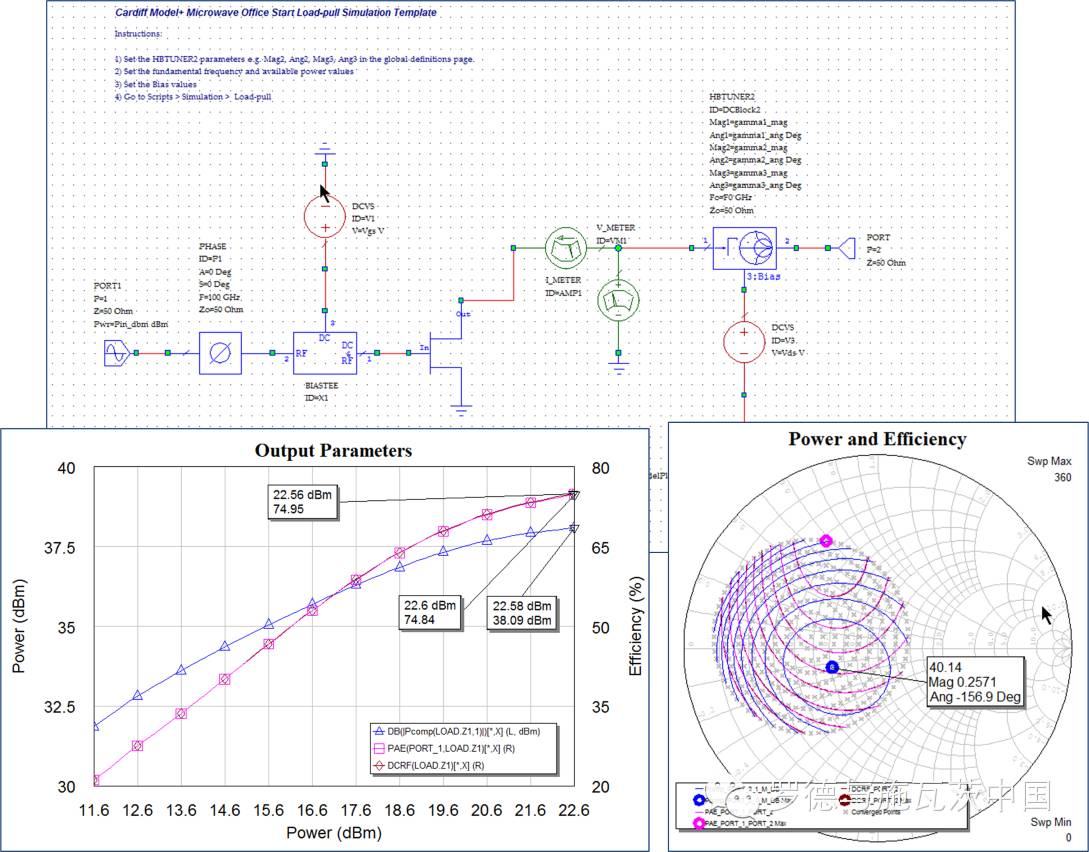

一旦模型完成,就可在模型生成器中直接验证结果。导出的模型可在 CAD 环境中使用,请参见图 15,而且可以进行传统的功率和效率分析以及执行波形工程。

图 15 - 在 Microwave Office 中运行的 Cardiff Model+

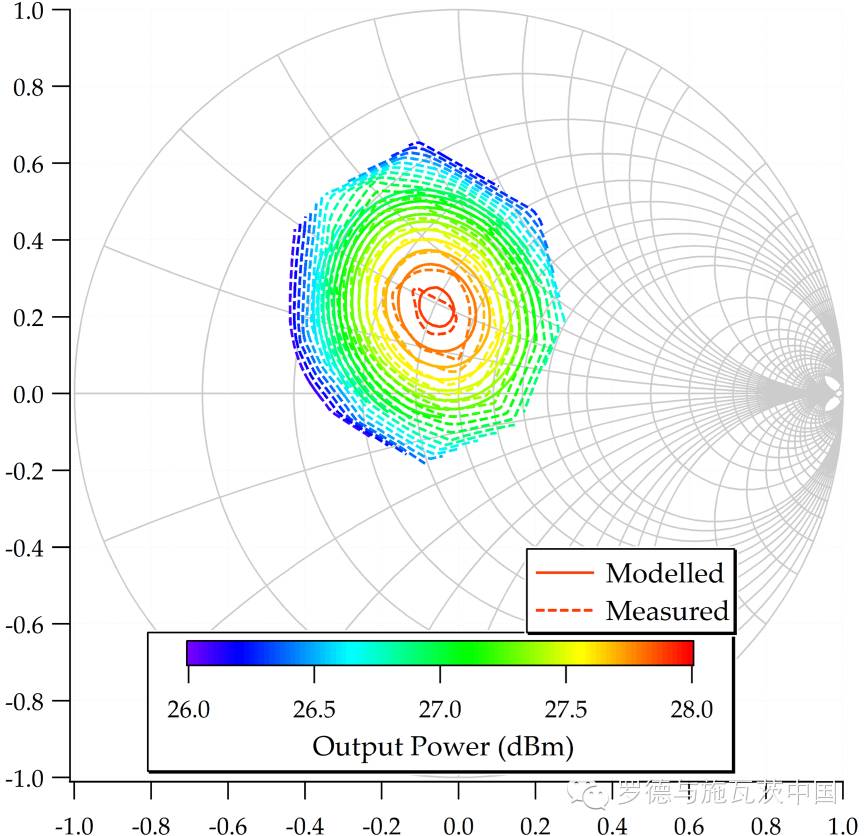

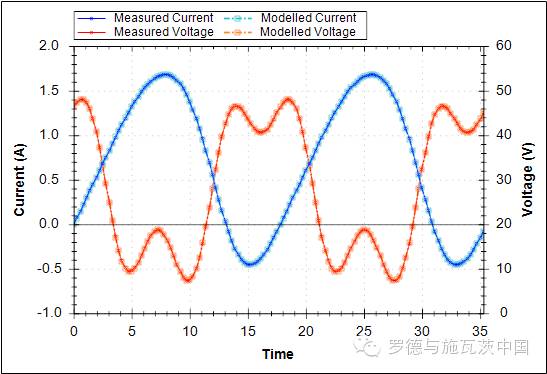

图 16 和 17 分别展示了建模和测量的负载牵引测试圆图和波形的对比,说明模型准确预测器件在不同阻抗性能的能力。

图 16 -建模和测量的负载牵引曲线

图17 -建模和测量的时域电压和电流波形

结论

本文展示了如何将 VNA 技术的发展与非线性测量解决方案的发展相结合,以使新器件和集成非线性器件模块的设计流程实现简单化。介绍并探讨了 Cardiff Model Lite 这一简单的行为模型及其作为基本模型的限制。还介绍了根据 Rohde & Schwarz VNA 最新技术开发的最先进的测量系统,说明了如何使用有源负载牵引改善负载牵引平台的性能。接下来,通过工艺开发和大功率放大器设计方面的案例研究,介绍了波形工程。最后介绍了更加高级的行为模型多项式 Cardiff Model+,允许用户将波形工程方法完全嵌入到仿真环境中。

-

请教,pspice如何模拟非线性元器件?2015-01-09 0

-

非线性器件的问题2018-11-08 0

-

是否需要澄清线性和非线性器件模型?2019-01-18 0

-

非线性效应测量2019-06-03 0

-

线性器件/系统和非线性器件/系统有什么区别2019-07-09 0

-

非线性电阻威廉希尔官方网站 分析2008-12-04 912

-

非线性器件在频谱搬移中的应用2016-11-05 612

-

开关磁阻电机的非线性建模及仿真2017-01-21 1058

-

调频准谐振变换器系统的非线性全阶建模及符号分析法2017-09-14 597

-

非线性威廉希尔官方网站 的分析方法_非线性威廉希尔官方网站 分析举例2018-03-13 28637

-

线性器件和非线性器件系统到底有什么区别2020-09-10 1976

-

威廉希尔官方网站 分析与电子线路经验谈 从线性到非线性2020-09-02 5871

-

为什么说二极管是一种非线性器件呢?2023-02-20 6374

-

探讨一下射频非线性器件2023-03-28 1269

-

为什么说二极管是一种非线性器件2023-09-02 2653

全部0条评论

快来发表一下你的评论吧 !