基于FPGA的ARM并行总线和端口设计

接口/总线/驱动

描述

通过EP2C20Q240器件和LPC2478处理器,研究ARM应用系统外部并行总线的工作原理和时序特性,以及在FPGA中进行双向总线设计的原则,设计并实现了FPGA并行总线.借助Quartus II仿真工具,对FPGA并行总线进行了时序仿真,并用SignalTap II逻辑分析仪进行在线测试,验证设计的正确性.

0 引言

在数字系统的设计中,FPGA+ARM 的系统架构得到了越来越广泛的应用,FPGA主要实现高速数据的处理;ARM 主要实现系统的流程控制.人机交互.外部通信以及FPGA 控制等功能.I2C.SPI 等串行总线接口只能实现FPGA 和ARM 之间的低速通信 ;当传输的数据量较大.要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输.

下面基于ARM处理器LPC2478以及FPGA器件EP2C20Q240,以ARM外部总线的读操作时序为例,研究两者之间高速传输的并行总线;其中,数据总线为32 位;并在FPGA 内部构造了1024x32bits 的SRAM 高速存储缓冲器,以便于ARM 处理器快速读写FPGA 内部数据.

1 ARM并行总线的工作原理

ARM 处理器LPC2478 的外部并行总线由24 根地址总线.32根数据总线和若干读写.片选等控制信号线组成.根据系统需求,数据总线宽度还可以配置为8 位.16 位和32 位等几种工作模式.

在本设计中,用到ARM 外部总线的信号有:CS.WE.OE.DATA[310].ADDR[230].BLS 等.CS 为片选信号,WE 为写使能信号,OE 为读使能信号,DATA 为数据总线,ADDR 地址总线,BLS 为字节组选择信号.ARM 的外部总线读操作时序图,分别如图1 所示.

根据ARM 外部并行总线操作的时序,ARM 外部总线的读写操作均在CS 为低电平有效的情况下进行.由于读操作和写操作不可能同时进行,因此WE 和OE 信号不能同时出现低电平的情况.

数据总线DATA 是双向的总线,要求FPGA 也要实现双向数据的传输.在时序图中给出了时序之间的制约关系,设计FPGA 时应该满足ARM 信号的建立时间和保持时间的要求,否则可能出现读写不稳定的情况.

2 FPGA 的并行总线设计

2.1 FPGA 的端口设计

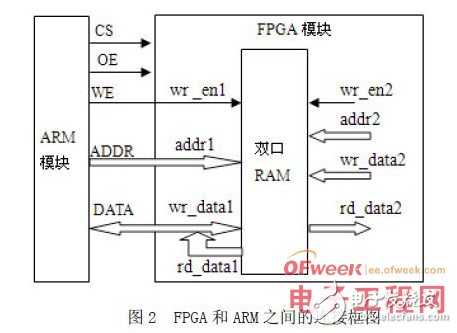

FPGA 和ARM 之间的外部并行总线连接框图,如图2 所示.由于FPGA 内部的SRAM 存储单元为32 位,不需要进行字节组的选择,因此BLS 信号可以不连接.为了便于实现ARM 和FPGA 之间数据的快速传输,FPGA 内部的SRAM 既要与ARM 处理器进行读写处理,还要跟FPGA 内部的其他逻辑模块进行数据交换,因此SRAM 采用双口RAM 来实现.

从端口的方向特性看,DATA 端口是INOUT(双向)方式,其余端口均为IN(输入)方式.从端口的功能看,clk20m 是全局时钟,在实现时应采用FPGA 的全局时钟网络,这样可以有效减少时钟延时,保证FPGA 时序的正确性.ADDR 是16 位的地址总线,由ARM 器件输入到FPGA.DATA 是32 位的双向数据总线,双向总线的设计是整个设计的重点.OE 为ARM 输入到FPGA 的读使能信号.

WE 为ARM 输入到FPGA 的写使能信号.CS 为ARM 输入到FPGA 的片选信号,FPGA 没有被ARM 选中时必须输出高阻态,以避免总线冲突.

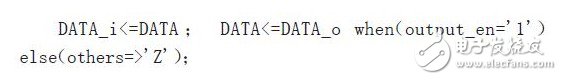

2.2 FPGA 的双向总线设计

在FPGA 的并行总线设计中,如果顶层和底层的模块都要用到双向的IO 端口,则要遵守设计原则;否则不利于VHDL 程序的综合.双向IO 端口的设计原则是:只有顶层设计才能用INOUT类型的端口,在底层模块中应把顶层的INOUT 端口转化为独立的IN(输入).OUT(输出)端口并加上方向控制端口.顶层设计的VHDL 代码如下:

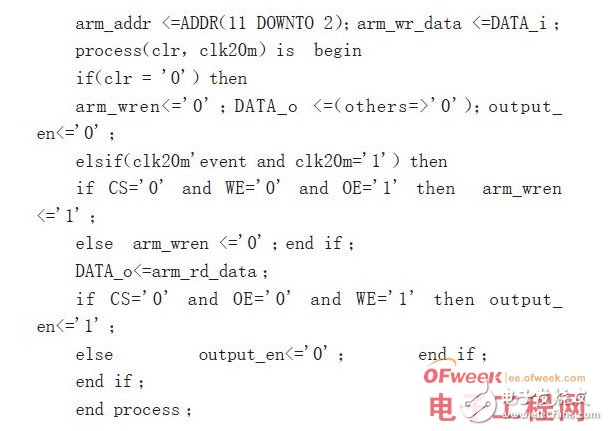

其中,DATA_i.DATA_o 和output_en 均为FPGA 内部的信号,在内部的各层次模块中,通过这三个信号就可以进行单向的IO 控制.这样,顶层设计中双向的DATA 端口转化为了内部单向的DATA_i(输入).DATA_o(输出)和output_en(输出使能).在内部各模块中,结合这三个信号以及ADDR.OE.WE.CS 等信号,则可方便地实现ARM 总线接口的功能.实现的VHDL 关键代码如下:

3 仿真结果分析

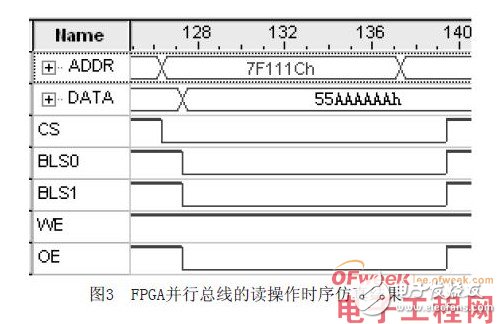

通过Quartus II 仿真工具,对FPGA 并行总线进行时序仿真;仿真结果如图3 所示.根据ARM 并行总线的读写时序图要求,从仿真结果可以看出FPGA 的总线接口设计满足了设计的要求.由于选用的FPGA 器件内部带有逻辑分析仪的功能模块,通过Quartus II 软件中的SignalTap II 逻辑分析工具,对FPGA的设计模块进行在线测试,发现总线时序了满足ARM 并行总线的要求,且工作稳定,从另一个角度验证了设计和仿真结果的正确性.

4 结论

由于FPGA 技术和ARM 技术应用越来越广泛,通过设计并行总线接口来实现两者之间的数据交换,可以较容易地解决快速传输数据的需求,因此设计满足系统要求的FPGA 并行总线显得尤为重要.本文设计的FPGA 的ARM 外部并行总线接口,满足了总线的时序要求,并在某航空机载雷达应答机中进行了应用,系统运行稳定,性能良好.以上的设计和仿真方法,对其他类似的设计也有一定的参考作用.

-

在赛灵思FPGA中使用ARM及AMBA总线2012-03-01 0

-

工程师深谈ARM+FPGA的设计架构2017-01-12 0

-

什么是基于FPGA的ARM并行总线?2019-09-17 0

-

ARM单片机和FPGA有什么区别 精选资料分享2021-07-16 0

-

用ARM与FPGA并行总线通信该如何去实现呢2022-11-22 0

-

AD1847串行端口音频编解码器如何与并行总线接口的实例2009-05-13 725

-

并行端口工作原理2009-07-27 3159

-

基于FPGA的ARM并行总线设计与仿真分析2013-08-15 7946

-

基于FPGA的ARM并行总线研究与仿真2017-01-24 867

-

基于FPGA和多DSP的多总线并行处理器设计2017-10-19 790

-

ARM+FPGA开发:基于AXI总线的GPIO IP创建2020-12-25 5675

-

基于FPGA的ARM并行总线设计原理2023-10-10 190

-

并行总线和串行总线的区别2023-12-07 3707

-

高速并行总线的工作原理是什么 高速并行总线有哪些2024-10-06 336

全部0条评论

快来发表一下你的评论吧 !