同步串行接口SSI的工作原理以及在音频处理中的应用

接口/总线/驱动

描述

引 言

嵌入式系统是“控制、监视或者辅助装置、机器和设备运行的装置”(devices used to control, monitor, or assiST the operaTION of equipment, machinery or plants)。从中可以看出嵌入式系统是软件和硬件的综合体,还可以涵盖机械等附属装置。目前国内一个普遍被认同的定义是:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。嵌入式系统必须根据应用需求对软硬件进行裁剪,满足应用系统的功能、可靠性、成本、体积等要求。所以,如果能建立相对通用的软硬件基础,然后在其上开发出适应各种需要的系统,是一个比较好的发展模式。目前的嵌入式系统的核心往往是一个只有几K到几十K微内核,需要根据实际的使用进行功能扩展或者裁减,但是由于微内核的存在,使得这种扩展能够非常顺利的进行。

随着嵌入式系统的广泛应用,系统内串口通信的需求越来越高,串行数据传输的协议也多样化,常用的有SSI、SPI、I2C、UART等。SSI(Server Side Include),通常称为服务器端嵌入,是一种类似于ASP的基于服务器的网页制作技术。大多数(尤其是基于Unix平台)的WEB服务器如Netscape Enterprise Server等均支持SSI命令。另外,在计算机硬件领域SSI是同步串行接口(Synchronous Serial Interface)的英文缩写。微处理器MCF5329中的SSI接口除了能用作一般的串行数据传输外,由于它带有的帧同步信号可用作左右声道数据的同步,支持两种音频总线接口(I2S和AC97接口),微处理器用一片或少数几片大规模集成威廉希尔官方网站 组成的中央处理器。这些威廉希尔官方网站 执行控制部件和算术逻辑部件的功能。微处理器与传统的中央处理器相比,具有体积小,重量轻和容易模块化等优点。微处理器的基本组成部分有:寄存器堆、运算器、时序控制威廉希尔官方网站 ,以及数据和地址总线。微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,是微型计算机的运算控制部分。它可与存储器和外围威廉希尔官方网站 芯片组成微型计算机。

TLV320DAC23是TI公司推出的高性能立体声高端编解码芯片,支持多种采样率和多种音频格式,并具有功耗低、封装小的特点,广泛应用于便携式数字音频处理系统中。

1 同步串行接口SSI的工作原理

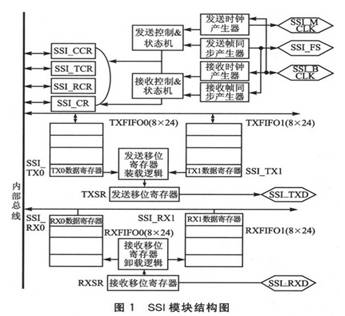

Synchronous SerialInterface(SSI)是一个全双工的串行接口,允许芯片与多种串行设备通信。可以使用“服务器端包含 (SSI)”指令将文本、图形或应用程序信息包含到网页中。例如,可以使用 SSI 包含时间/日期戳、版权声明或供客户填写并返回的表单。对于在多个文件中重复出现的文本或图形,使用包含文件是一种简便的方法。将内容存入一个包含文件中即可,而不必将内容输入所有文件。通过一个非常简单的语句即可调用包含文件,此语句指示 Web 服务器将内容插入适当网页。而且,使用包含文件时,对内容的所有更改只需在一个地方就能完成。 SSI模块结构如图1所示。

从图中可看出,SSI模块由发送威廉希尔官方网站 、接收威廉希尔官方网站 、串行时钟和帧同步时钟产生威廉希尔官方网站 组成。发送威廉希尔官方网站 和接收威廉希尔官方网站 相互独立,但是共用串行时钟和帧同步时钟。

1.1 SSI模块引脚信号描述

SSLCLKIN:SSI时钟输入信号。

SSLBCLK:SSI串行比特时钟。

SSLMCLK:SSI串行主时钟信号,在SSI主模式下,

该信号也作为过采样时钟信号。

SSI_FS:SSI串行帧同步信号。

SSLRXD:SSI串行接收数据信号。

SSI_TXD:SSI串行发送数据信号。

1.2 SSI的操作模式

SSI有3种基本同步操作模式:普通模式、网络模式和门时钟模式。

普通模式是最简单的模式,一帧内只能传输一个字,而且每一帧都需要帧同步信号来控制同步;网络模式主要用于多时隙的情况下,一帧内可以传输2个字到32个字不等;门时钟SSI_BCLK模式下,串行比特时钟SSI_BCLK指示了发送引脚或接收引脚上的有效数据。

除了上述3种基本模式外,针对音频上的应用,SSI还支持两种衍生模式——I2S模式和AC97模式,分别用于传输I2S和AC97音频格式数据。

1.3 SSI的初始化

初始化SSI模块的正确顺序:

①上电或重启SSI(SSI_CR[SSI_EN]=0),即关闭SSI模块功能。

②配置SSI模块。涉及的寄存器包括控制寄存器SSI_CR、中断允许寄存器SSI_IER、发送配置寄存器SSI_TCR、接收配置寄存器SSI_RCR和时钟控制寄存器SSI_CCR。

③通过SSI_IER寄存器设置必要的中断或DMA。

④设置SSI_CR[SSI_EN]=1允许SSI模块功能。

⑤设置SSI_CR[TE/RE],开始发送/接收数据。

1.4 SSI的工作过程

(1)发送数据

单通道时,数据从串行发送数据寄存器SSI_TX0中传到发送移位寄存器TXSR中,再通过串行发送引脚SSI_TXD发送出去,然后根据用户设置情况决定是否产生发送中断。如果发送缓冲区TXFIFOO被允许,则SSI_TX0继续从TXFIFOO中取数据,直到TXFIFOO中的数据全部被发送,再通过用户设置情况决定是否产生发送中断。双通道时,发送移位寄存器TXSR交替从SSI_TX0和SSI_TXl中取出数据。

(2)接收数据

单通道时,数据从串行接收引脚SSI_RXD进来,由接收移位寄存器RXSR传输给接收数据寄存器SSI_RX0,再根据用户设置情况决定是否产生接收中断。如果接收缓冲区RXFIFOO被允许,则SSI_RX0将数据写入RXFIFOO,并继续从接收移位寄存器中获取数据。双通道时,接收移位寄存器RXSR交替将数据传输给SSI_RX0和SSI_RXl。

2 音频编解码芯片简介

Codec 编码解码器主要作用是对视频信号进行压缩和解压缩。计算机工业定义通过24位测量系统的真彩色,这就定义了近百万种颜色,接近人类视觉的极限。现在,最基本的V GA显示器就有640*480像素。这意味着如果视频需要以每秒30帧的速度播放,则每秒要传输高达27MB的信息,1GB容量的硬盘仅能存储约37 秒的视频信息。因而必须对信息进行压缩处理。通过抛弃一些数字信息或容易被我们的眼睛和大脑忽略的图像信息的方法,使视频的信息量减小。这个对视频压缩解压的软件或硬件就是编码解码器。编码解码器的压缩率从一般的2 :1-100:1不等,使处理大量的视频数据成为可能。

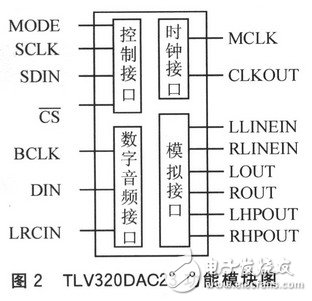

TLV320DAC23是TI公司推出的一颗高性能立体声音频处理芯片(CODEC芯片),采用了多比特sigma-delta过采样技术,采样率可以从8 kHz到96 kHz,传输字长可选择为16位、20位、24位或32位;最大输出信噪比可达到100 dB;控制端口可兼容SPI、2-wire等协议;回放模式下功率为18 mw,省电模式下小于15μW;适用于便携式的数字音频处理。其功能模块框图如图2所示。

2.1 控制接口

控制接口用于对器件TLV320DAC23的寄存器编程,设置音频芯片的工作参数。它兼容两种模式:SPI三线模式和2一wire模式。

MODE:模式选择引脚。为0时,采用2一wire模式;为1时,采用SPI模式。

SCLK:控制端口串行数据时钟。

SDI:控制端口串行数据输入。

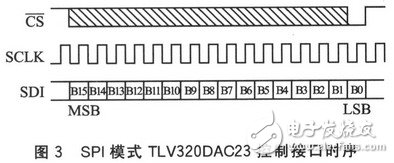

CS:控制端口输入锁存/地址选择。在SPI模式下,CS用于数据锁存控制;在2一wire模式下,CS定义了器件地址域的第7位。SPI模式下,一个控制字为16位,分为两部分:高7位为控制地址,低9位为控制字。16位的控制字由MSB位开始传输,每个比特在SCLK的上升沿被锁存,整个16位的控制字在最低位被CS锁存进TLV320DAC23。

2.2 模拟接口

模拟接口包括线输入、线输出和耳机输出。耳机输出可以驱动16Ω或32 Ω的耳机,音量增益为6 dB到一73 dB。

LLINEIN、RLINEIN:左、右声道输入。

LOUT、ROUT:左、右声道输出。

LHPOUT、RHPOUT:左、右声道耳机输出

2.3 数字音频接口

数字音频接口用于输入TLV320DAC23的D/A数据。

BCLK:I2S串行比特时钟。主模式时BCLK为输出,从模式时BCLK为输入。

DIN:I2S串行数据输入。

LRCIN:字时钟信号(帧信号),用于控制左、右声道的数据。在主模式中,由TLV320DAC23产生该信号,在从模式中,由主设备(如DSP或MCU)产生该信号。

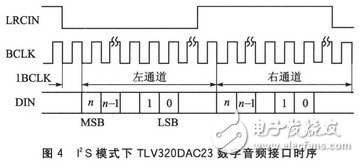

TLV320DAC23支持4种音频接口模式:右对齐模式、左对齐模式、I2S模式和DSP模式。这4种模式都是最高有效位MSB在前,16到32位不同的字长(右对齐除外,它不支持32位)。图4是I2S模式下的数字音频接口时序,数据的MSB在LRCIN下降沿后的第2个BCLK上升沿开始传输。

2.4 时钟接口

MCLK:芯片主时钟信号。当TLV320DAC23作为主设备时,该信号由芯片自身产生;当TLV320DAC23作为从设备时,该信号由外部产生。

CLKOUT:时钟输出信号。可以为MCLK或MCLK/2。

3 基于MCF5329的音频驱动设计

3.1 硬件威廉希尔官方网站

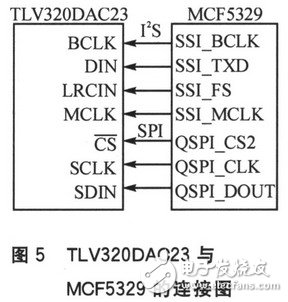

TLV320DAC23与MCF5329的接口有两个:一个是控制接口,用于设置TLV320DAC23的寄存器,从而设置它的工作参数。由于MCF5329具有QSPI模块,它兼容SPI接口格式,所以TLV320DAC23的控制接口采用SPI模式。另一个是数字音频接口,用于传输TLV320DAC23的音频数据并控制数据的时序。

在本设计中,由微控制器MCF5329提供时钟信号,所以将MCF5329设为主设备,TLV320DAC23作为从设备。具体连接如图5所示。

3.2 软件设计

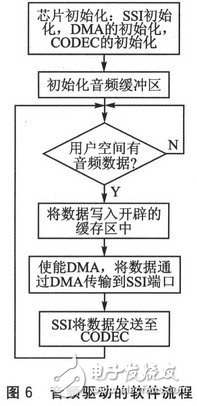

音频播放的过程如下:程序检测到用户空间有需要播放的音频数据,便将音频数据拷贝到所建立的缓冲区中;然后通过DMA将缓冲区的音频数据传输到SSI模块的发送引脚SSI_TXD,发送引脚将数据发送至TLV320DAC23中,通过耳机播放出来。

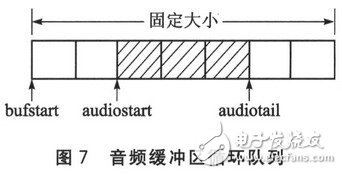

软件设计的流程如图6所示。其中,音频缓冲区被设置为一个固定大小的循环队列,其设置如图7所示。初始时,bufstart、audiostart、audiotail都指向缓冲区头。当用户空间有数据时,将数据拷贝到缓冲区并用audiotail指示数据尾部,数据的头部通过DMA引擎连接到SSI_TXD引脚。

结 语

本文分析了同步串行接口SSI的工作原理及过程,并通过与编解码芯片TLV320DAC23的通信详细介绍了SSI在音频处理中的应用。实践表明,SSI接口简单,使用灵活可靠。

来源;电子工程网

-

串行音频接口(SAI)中slot是什么意思?2024-05-11 0

-

SSI在音频处理中的应用2019-05-22 0

-

实用AGC算法的工作原理及在音频FPGA中的应用2020-10-21 0

-

基于同步串行接口(SSI)的LED显示器设计2010-12-11 728

-

SSI同步串行技术在时栅传感器中的应用研究2011-01-01 514

-

SSI接口技术及其在音频处理中的应用2011-09-24 3495

-

Stellaris外设驱动库_SSI2016-01-13 736

-

详解双向/串行/同步(BiSS)位置编码器的接口2017-11-17 19551

-

NA400系列SSI编码器模块使用说明2017-11-25 1123

-

NA400系列SSI编码器模块使用说明书2017-12-08 1213

-

音频编解码器的音频串行接口配置2018-05-17 1193

-

同步串行控制器SSC的介绍以及如何为音频应用配置SSC的详细资料概述2018-06-13 3412

-

SPI接口的基本概念和工作原理2023-09-26 4366

-

SSI编码器工作原理及应用2023-10-13 4109

-

串行接口的工作原理和结构2024-08-25 1695

全部0条评论

快来发表一下你的评论吧 !