分频威廉希尔官方网站 的分频方式

音频威廉希尔官方网站

描述

分频威廉希尔官方网站 的分频方式

构成简单的分频威廉希尔官方网站 人可以听到的声音的频率范 围是在20Hz—20kHz之间,祈望仅使用一只扬声器就能够保证放送20Hz—20kHz这样宽频率的声音是很难做到的,因为这会在技术上存在各种各样 的问题和困难。所以,在通常情况下,高质量的放音系统为了保证再现声音的频率响应和频带宽度,在专业范畴内大都采用高低音分离式音箱放音。而采用高低音分 离式音箱放送声音时,就必然要对声音按频段分离,将声音按频率分段的个数就是声音分频数。

声音的分频主要是受扬声器的控制,因为绝大多数扬声器都有自己最适合的频率范围,真正的高质量全频扬声器非常少见并且价格极端昂贵。同时为了克服不同频率声音扬声器引起的切割失真和减少同一音箱中的不同扬声器之间产生的声音干涉现象,必须对声音进行分频,将不同频段的声音送入不同的扬声器。

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频;另一种是被动分频 (ActiveCrossover),或者叫功率分频,也可以叫内置分频、无源分频。主动分频是指分频器不在音箱内部,而在功率放大之前,由于此时声音信 号很弱,因此容易将声音彻底分频,缺点是相应的电子线路分频点较为固定,不容易和不同扬声器配合,常见于高端和专业音响,随着多路功放的普及,主动分频方 式比以前普及很多。被动分频是指分频器在音箱内,此时声音信号已经经过放大,分频威廉希尔官方网站 会造成一定干扰,但音箱可以适用于不同功放。

最简单的分频就是二分频,将声音分为高频和低频,分频点需要高于低音喇叭上限频率的1/2,低于高音喇叭下限频率的2倍,一般的分频点在2K到5K之间。但是这样分频对低音照顾仍然不够完善,因为低音为 了获得更好效果,往往需要单独处理,并且扬声器的切割失真对低音的影响也最大,因此近些年三分频逐渐流行起来。三分频是将声音分为低音、中音和高音,有两 个分频点,低音分频点一般在200Hz以下,或者120Hz,甚至更低,高音分频点一般为2Hz-6KHz。此外也有少量的四分频或者多分频系统。显然更 多分频数理论上更有利于声音的还原,但过多的分频点会造成整体成本上升,并且实际效果提升有限,因此常见的分频数仍然是二分频和三分频。

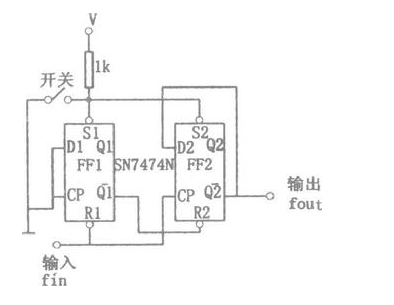

2N分频威廉希尔官方网站 的实现方法

1 目的

分频系数较大的2N 分频威廉希尔官方网站 需要采用标准计数器来实现,此处的方法是直接将计数器的相应位赋给分频威廉希尔官方网站 的输出信号即可实现分频功能。采用这个方法的好处是:一是不需要定义中间信号,设计简单,节约资源;二是可以避免毛刺现象的发生,从而避免了逻辑错误产生的可能性。

下面采用VHDL 和Verilog 两种语言实现的2分频、4分频和8分频。

2 VHDL实现(不带复位信号)

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY clk_8div_2 IS

PORT(CLK:IN std_logic;

CLK_DIV2:OUT std_logic;

CLK_DIV4:OUT std_logic;

CLK_DIV8:OUT std_logic);

END clk_8div_2;

ARCHITECTURE rtl OF clk_8div_2 IS

SIGNAL counter:std_logic_vector(2 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK’event AND CLK=’1’) THEN

IF (counter = “111”) THEN

count’0’);

ELSE

counter

END IF;

END PROCESS;

CLK_DIV2

CLK_DIV4

CLK_DIV8

END rtl;

3 Verilog实现(有复位信号)

3.1

module clk_8div_2(

input CLK,

output CLK_DIV2,

output CLK_DIV4,

output CLK_DIV8,

input RESET

);

reg [2:0] clk_counter;

always @ (posedge CLK or posedge RESET) begin

if (RESET)

begin clk_counter

end

begin clk_counter

assign CLK_DIV2 = clk_counter[0]; assign CLK_DIV4 = clk_counter[1]; assign CLK_DIV8 = clk_counter[2];

endmodule

3.2 测试文件

module test_clk;

// Inputs reg CLK; reg RESET; // Outputs wire CLK_DIV2; wire CLK_DIV4; wire CLK_DIV8; // Instantiate the Unit Under Test (UUT) clk_8div_2 uut ( .CLK(CLK),

); .CLK_DIV4(CLK_DIV4), .CLK_DIV8(CLK_DIV8), .RESET(RESET) initial begin // Initialize Inputs CLK = 0; RESET = 1; // Wait 100 ns for global reset to finish #100;

RESET = 0;

end

always #10 CLK

- 相关推荐

- 扬声器

- 二分频

- 分频威廉希尔官方网站

-

石英晶体与分频威廉希尔官方网站 及制作2009-04-13 1073

-

任意分频威廉希尔官方网站 图2009-04-09 2910

-

分频系数可变的分频器2009-04-11 1381

-

简单的分频威廉希尔官方网站2009-04-11 2014

-

脉冲分频威廉希尔官方网站2009-06-12 4001

-

分频威廉希尔官方网站2009-06-12 7281

-

什么是分频威廉希尔官方网站2009-06-22 5940

-

10分频威廉希尔官方网站2009-06-22 16430

-

时钟分频及定时变换威廉希尔官方网站2009-10-11 2294

-

可编程分频器威廉希尔官方网站2010-01-12 3568

-

基于Verilog的FPGA分频设计2011-11-09 1278

-

分频是什么意思_分频威廉希尔官方网站 有什么用2017-11-02 38904

-

分频器的设计-奇偶分频2018-12-08 10006

-

偶数分频、奇数分频、半整数分频和小数分频详解2023-03-29 5006

-

分频器之小数分频设计2023-06-05 1614

全部0条评论

快来发表一下你的评论吧 !