xilinx7系列FPGA的7种逻辑代码配置模式

可编程逻辑

描述

今天咱们聊聊xilinx7系列FPGA配置的相关内容。总所周知FPGA上电后,其工作的逻辑代码需要从外部写入FPGA,FPGA掉电后其逻辑代码就丢失,因此FPGA可以被无限次的配置不同的逻辑代码,但FPGA需要配备外部的非易失存储器来存储其逻辑代码或者通过单片机、DSP或者其它控制器来实现FPGA上电后的逻辑代码载入。

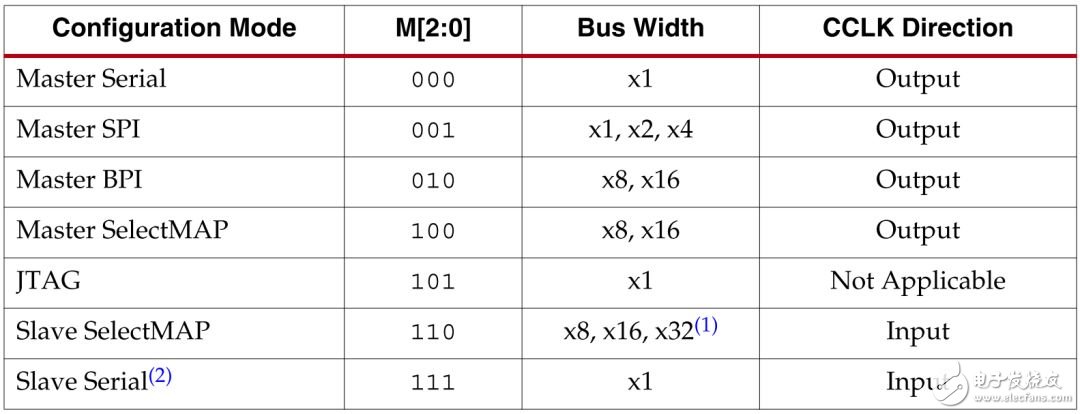

xilinx7系列FPGA设计有专门的逻辑代码配置管脚,通过不同的管脚接法,其逻辑代码配置模式可以分为以下7种:

1,主串配置模式

2,从串配置模式

3,主并配置模式

4,从并配置模式

5,JTAG配置模式

6,主SPI配置模式

7,主BPI配置模式

所谓的主,即配置时钟CCLK由FPGA提供;所谓从,即配置时钟CCLK由外部控制器提供。下面这张表代表了这7种配置模式,其模式的切换由FPGA的3个配置管脚M0、M1、M2控制:

下面咱们分别说说xilinx7系列FPGA的这7种配置模式:

1,主串配置模式

在该模式下,FPGA向外部的非易失性串行数据存储器或者控制器发出CCLK时钟信号,配置数据会以串行方式载入FPGA,在前几代的FPGA中,存储器通常选择xilinx 官方的XCF串行系列存储器,并给出了相应的设计原理图,但在7系列FPGA中,这种方式貌似被放弃了,其官方的配置文档里并无主串配置模式的相关详细描述。

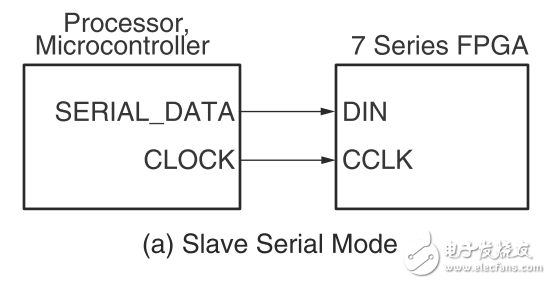

2,从串配置模式

如下图1所示,在该模式下,由外部的处理器提供CCLK时钟和串行数据,用户实现起来相对复杂,不够大众化,这里就不做介绍了。

图1

3,主并配置模式

同样的,该模式在其官方文档并无详细设计描述,无从参考。

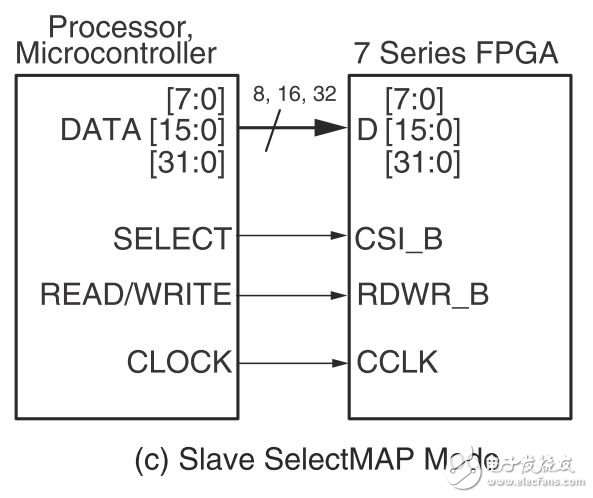

4,从并配置模式

如下图2所示,在该模式下,外部处理器提供配置时钟和并行的配置数据,该模式相对于串行方式来说,配置的速度快,但设计稍微复杂。下图3为官方给出的详细配置原理图,该模式同样使用较少。

图2

图3

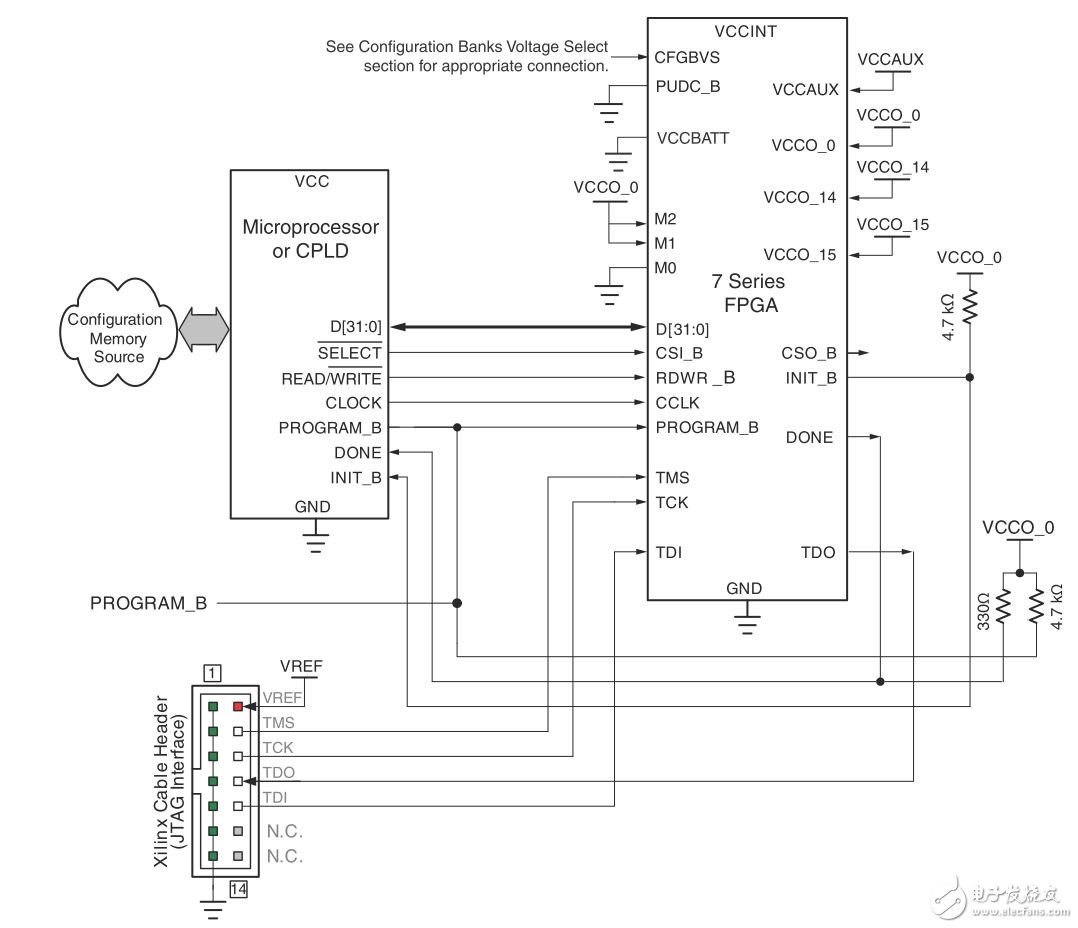

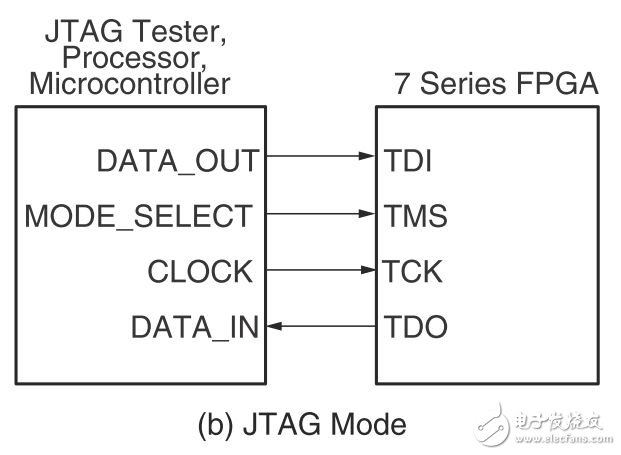

5,JTAG配置模式

如下图4所示,该模式属于工程调试模式,咱们在设计FPGA时必带这种模式。该模式只能在线配置和调试FPGA,无法存储逻辑代码。最简单的操作方式是使用xilinx官方提供的专用JTAG调试下载器,但同时也允许用户通过外部处理器自行设计JTAG的数据协议来配置FPGA逻辑代码。再次强调,该模式只是一个调试模式。

图4

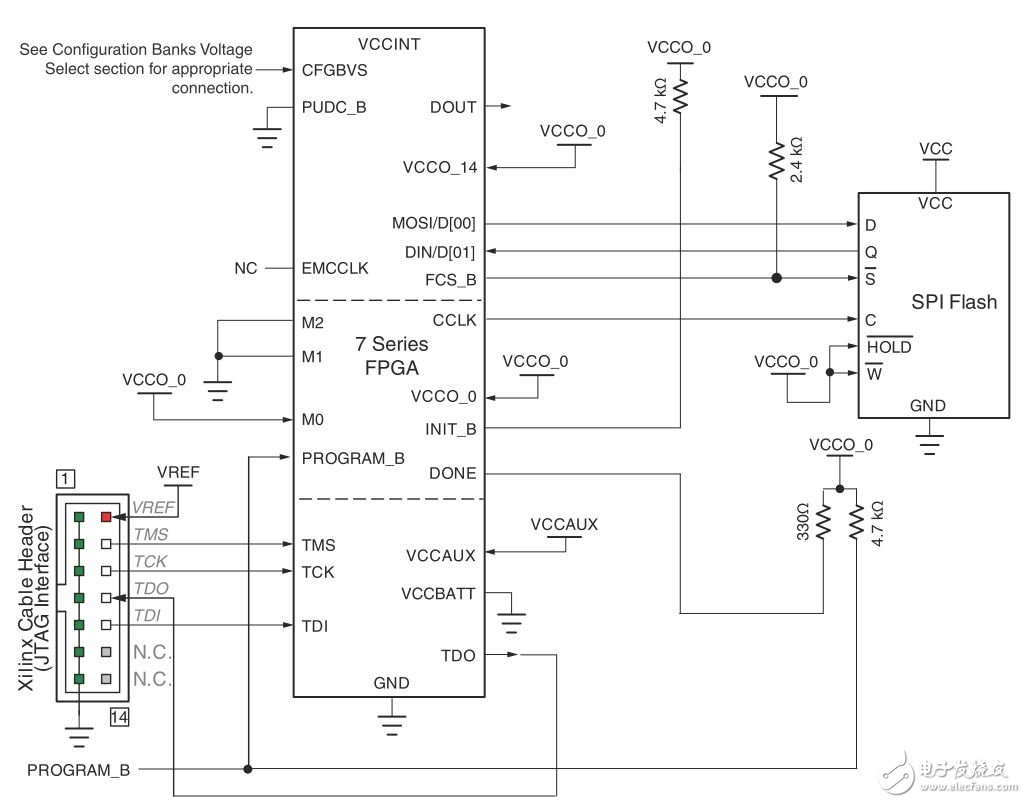

6,主SPI配置模式

这种模式应该算是咱们使用最广泛的配置模式了,通过外挂一个SPI存储器即可。通常该模式和JTAG配置模式一起设计。JTAG模式在线调试好逻辑代码后,将该逻辑代码存储在SPI存储器中,以后FPGA上电后就会自动载入存储器中的逻辑代码。下图5为官方给出的详细配置原理图。

图5

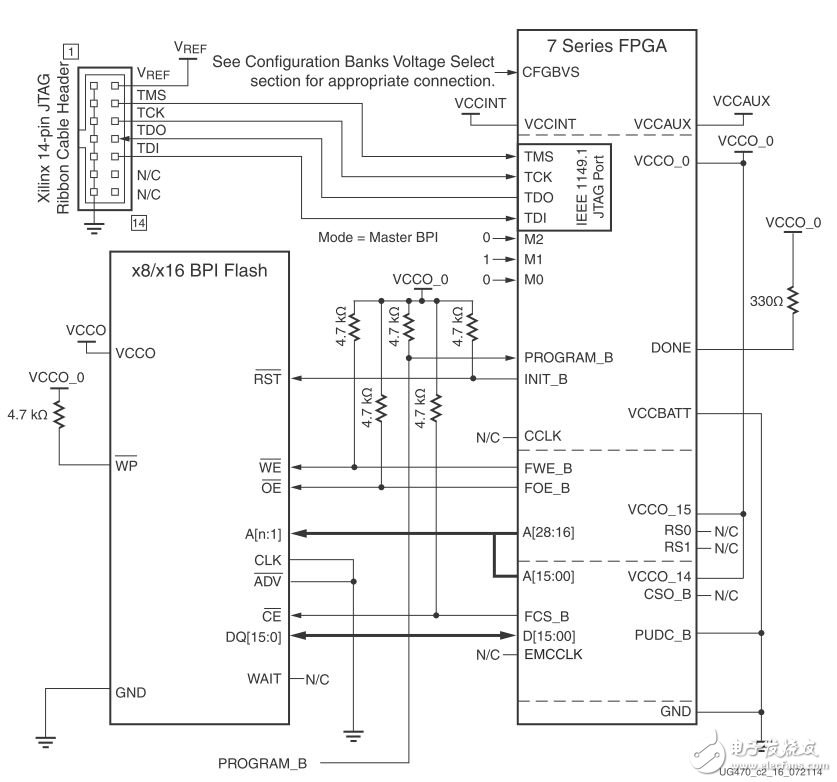

7,主BPI配置模式

该模式的时钟CCLK同样由FPGA提供,并行的数据比SPI模式的串行数据配置速度要快,但设计稍微复杂一点。图6为官方给出的详细配置原理图。

图6

咱们在设计FPGA时,基本上都是采用JTAG配置模式+主SPI配置模式(图5)或者JTAG配置模式+主BPI配置模式(图6)。前者用于一般的应用,后者用于对FPGA上电后逻辑代码载入速度有较高要求的应用。

-

3.Xilinx7系列普及讲座之-----Xilinx7系列Memory资源2013-03-31 0

-

1.Xilinx7系列普及讲座之-----Xilinx7系列IO使用规则2013-03-31 0

-

2.Xilinx7系列普及讲座之-----Xilinx7系列Clocking资源2013-03-31 0

-

xilinx公司的7系列FPGA应用指南2012-08-07 2136

-

Xilinx7系列FPGA包装和插脚产品规范的资料免费下载2019-02-20 847

-

Xilinx 7系列FPGA选择资源的技术参考指南2020-12-09 1199

-

Xilinx 7系列FPGA可配置逻辑块的用户指南2020-12-09 889

-

Xilinx 7系列FPGA内存资源的用户指南2020-12-09 1420

-

Xilinx 7系列FPGA时钟资源2020-12-10 940

-

Xilinx7系列FPGA选择资源用户指南2020-12-10 953

-

XILINX可编程逻辑®7系列FPGA2022-11-03 1987

-

Xilinx 7系列与Ultrascale系列FPGA的区别2023-09-15 5580

-

AMD Xilinx 7系列FPGA的Multiboot多bit配置2024-02-25 1265

-

Xilinx 7系列FPGA功能特性介绍2024-04-22 5374

-

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性2024-11-05 758

全部0条评论

快来发表一下你的评论吧 !