基于RS-485接口的信号隔离自收发威廉希尔官方网站 设计

接口/总线/驱动

描述

RS-485标准在工业控制、电力通讯、智能仪表等领域中使用广泛。但是,在工业控制等现场环境中,情况复杂,常会有电气噪声干扰传输线路;在多系统互联时,不同系统的地之间会存在电位差,形成接地环路,会干扰整个系统,严重时会造成系统的灾难性损毁;还可能存在损坏设备或危害人员的潜在电流浪涌等高电压或大电流。因此,对RS-485接口的隔离是非常有必要的。

ADM2483是一款集成了信号通道隔离和RS-485收发器的芯片。以单芯片实现了对RS-485接口的隔离,威廉希尔官方网站 连接简单,设计方便,性能上远高于繁琐的光耦隔离485威廉希尔官方网站 设计。在某些系统应用中,由于I/O口数量有限,因此我们希望半双工的RS-485收发器能够实现自收发功能,以节省用于控制RE与DE的两路I/O端口。目前,实现这一功能的主流方案是采用74HC14芯片。

隔离RS-485接口威廉希尔官方网站

之前我们经常采用的485接口隔离威廉希尔官方网站 是利用三个光耦隔离收发及控制信号,加上485收发器共需要4片IC,且采用光耦隔离需要限流及输出上拉电阻,必要时还会使用三极管驱动。设计威廉希尔官方网站 繁琐,耗费时间长,如果没有之前使用光耦的经验,那么在选用光耦限流及输出上拉电阻方面会耗费很多不必要的时间;且光耦的输出信号上升时间较长,在与数字I/O端口相接时,需另加施密特整形才能保证信号的波形符合标准,如在FPGA、DSP等系统中的应用。

ADM2483是内部集成了磁隔离通道和485收发器的芯片,内部集成的磁隔离通道原理与光耦不同,在输入输出端分别有编码解码威廉希尔官方网站 和施密特整形威廉希尔官方网站 ,确保了输出波形的质量。且磁隔离功耗仅为光耦的1/10,传输延时为ns级,从直流到高速信号的传输都具有超越光耦的性能优势。内部集成的低功耗485收发器,信号传输速率可达500Kbps,后端总线可支持挂载256个节点。具有真失效保护、电源监控以及热关断功能。

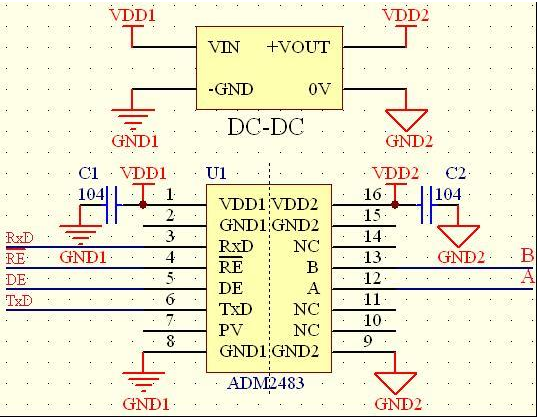

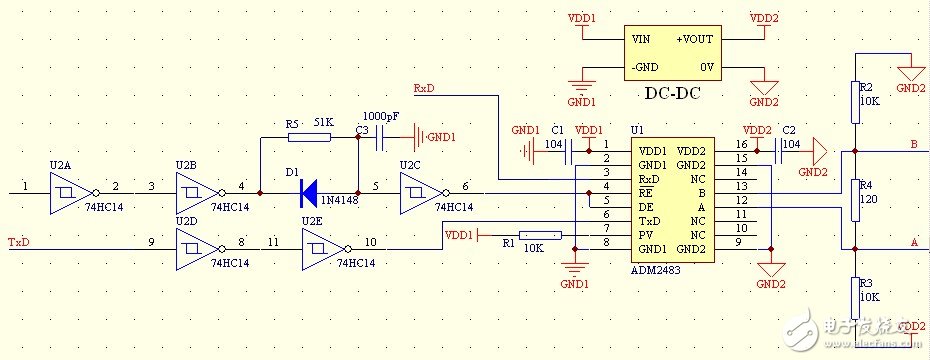

要实现隔离RS-485接口的威廉希尔官方网站 设计只需在ADM2483的电源与地之间接一个104的去耦电容即可。当然,DC-DC隔离电源是必不可少的。其威廉希尔官方网站 连接如下图:

信号自收发威廉希尔官方网站

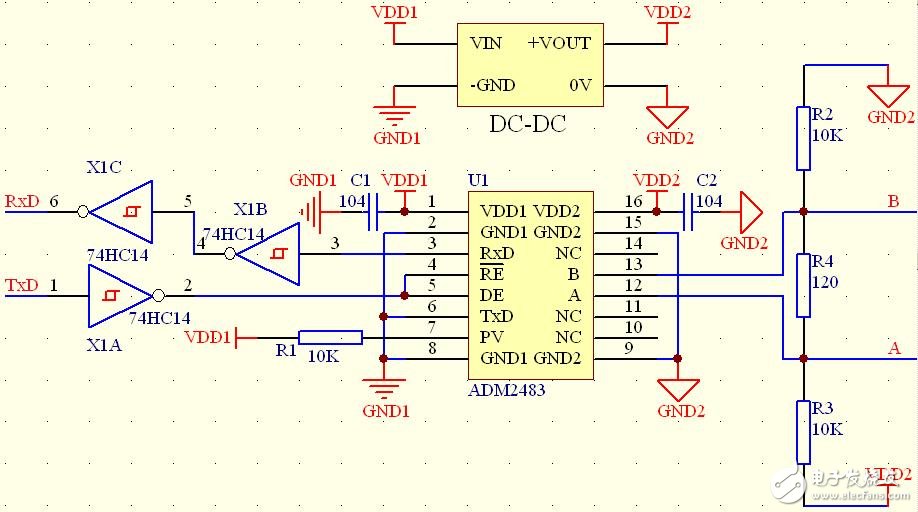

信号自收发威廉希尔官方网站 我们采用74HC14芯片,利用它的施密特波形翻转性能来控制RE、DE引脚,以实现信号的自收发。其威廉希尔官方网站 连接如下图:

如图所示,MCU的发送信号经过施密特触发器反向后输给DE和RE脚,发送数据引脚TxD接地。

当有高电平信号发送时,经反向变为低电平信号,DE/RE引脚输入为低电平,使发送驱动器禁止,总线为高阻状态,此时由A、B总线上的上拉电阻产生高电平输出。

当有低电平信号发送时,经反向变为高电平信号,DE/RE引脚输入为高电平,使发送驱动器工作,由于TxD引脚端接地,为低电平,这样就将低电平发送至总线。

本参考设计仅为实现RS-485接口的自收发功能,在实际应用中,应根据使用情况作出相应的修改。此收发威廉希尔官方网站 也有不足之处,当在连续发送高电平时,ADM2483的DE/RE引脚处于接收状态,所以,此时的发送端和接收端都处于接收状态,这时的总线是空闲状态,是允许各节点发送数据的,因此一般在主从式的网络结构中采用此方法。

在网络上也有不同的几种实现RS-485收发器自收发的方案,分别有以下几种:

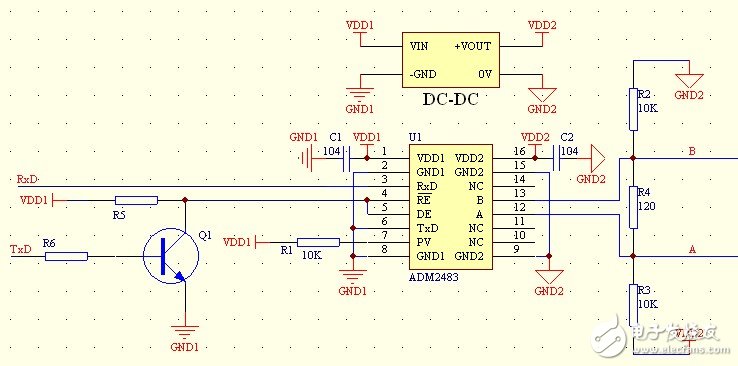

利用三极管反向原理实现

威廉希尔官方网站 如下图:

当不发送数据时,TxD信号为高电平,经V1反向后使ADM2483处于接收状态。

当发送数据时,TxD为高时,经V1反向,使发送驱动器禁止,总线为高阻状态,此时由A、B总线上的上拉电阻产生高电平输出。TxD为低时,经V1反向,使发送驱动器工作,由于TxD引脚端接地,为低电平,这样就将低电平发送至总线。

采用这种威廉希尔官方网站 时,需要程序保证不同时进行接收和发送的操作。

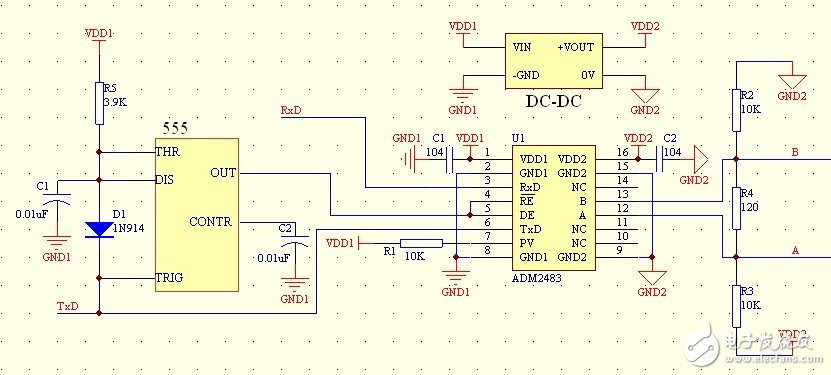

利用555定时器,其原理于以上威廉希尔官方网站 类似,威廉希尔官方网站 图如下:

555定时器为边沿触发,当TxD发送高电平时,555定时器OUT引脚输出低电平,当TxD发送低电平时,555定时器OUT引脚输出高电平,当TxD转为高电平时,OUT引脚输出的高电平状态会延迟一会再转入低电平,以确保发送数据的正确性。

采用74HC14和RC威廉希尔官方网站 实现,此威廉希尔官方网站 是对单纯使用74HC14实现自收发威廉希尔官方网站 的改进,增加了RC充放电威廉希尔官方网站 ,减少总线处于空闲状态的时间,威廉希尔官方网站 如下图:

当TxD信号为高电平,则通过电阻为电容充电,其充电时间为T,该时间应设置为串口发送一个字节所需要的时间,由R,C参数来确定。当电容充满后,则DE/RE为低电平,使ADM2483处于接收状态。

在发送数据时,TxD起始位产生第一个下降沿,使电容经过二极管进行快速放电,使DE/RE很快变为高电平,ADM2483处于发送状态。在发送过程中, 当TxD变成高电平时,电容通过电阻缓慢充电,使DE/RE仍然保持在发送状态,可有效吸收总线上的反射信号。当RC充电结束,使DE/RE转入接受状态时, 总线上的上拉、下拉电阻将维持TxD高电平的发送状态,直至整个bit发送结束。

当数据发送完毕以后,TxD变为高电平,RC又开始充电,即经T时间后,ADM2483又转换为接收状态。

责任编辑;zl

- 相关推荐

- 接口威廉希尔官方网站

- RS-485接口

- 信号隔离

-

有关隔离RS-485收发器的7个设计问题2018-08-11 0

-

隔离型RS-485收发器设计问题总结2019-07-29 0

-

隔离型RS-485收发器设计有什么问题?2019-07-31 0

-

均方根信号和电源隔离RS-485收发器2020-05-13 0

-

有关隔离式RS-485收发器的7大设计问题2020-08-19 0

-

嵌入式隔离RS-485收发器原理及应用2010-03-06 1008

-

自动收发转换的RS-485接口威廉希尔官方网站 及测试威廉希尔官方网站2009-09-27 4457

-

RS-485接口保护威廉希尔官方网站2009-11-20 7116

-

RS-485自收发威廉希尔官方网站 的参考设计2011-01-20 20101

-

RS-485隔离式数字接口2017-11-21 2643

-

基于74HC14芯片与ADM2483芯片实现RS-485接口的信号隔离自收发设计2019-02-22 15358

-

如何解决RS-485自动收发威廉希尔官方网站 应用异常的问题呢?2023-06-30 5683

-

SM系列全隔离RS-485收发芯片“全家福”来啦!2023-11-14 2545

-

如何解决RS-485自动收发威廉希尔官方网站 应用异常?2024-11-02 265

全部0条评论

快来发表一下你的评论吧 !