一种基于FPGA内部存储器的适合音频解嵌的高效异步FIFO设计

可编程逻辑

描述

在视音频嵌入解嵌系统中,嵌入音频、音频解嵌与音频转换成音频帧标准格式输出都是工作在不同的时钟频率下的。多时钟带来的问题就是如何设计异步时钟之间的接口威廉希尔官方网站 。

异步FIFO存储器是一种在数据交互系统中得到广泛应用的先进先出逻辑器件,具有容纳异步信号的频率(或相位差异)的特点。使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据。因此,异步FIFO被广泛应用于实时数据传输、网络接口、图像处理等方面。

虽然目前也出现了一些通用的异步FIFO内核,但在一些具体环境下其工作效率并不是最理想的。针对这个问题,本文介绍了一种适合音频解嵌的高效异步FIFO,对通用异步FIFO进行了一些改进,最后利用Verilog HDL硬件描述语言设计并仿真实现。

1 SDI音频嵌入基本格式

在模拟视频中存在着行、场消隐期,而行、场消隐期内并不存在有效图像信号。对于数字视频信号,同样地也存在没有有效视频信号的区间。

模拟视频中的行消隐期间,在数字视频中被称为行辅助数据区HANC(Horizontal Ancillary Data)。分量数字视频格式的每一个有效行中,625/50制共有1 728个取样字(525/60制为1 716个取样字),其中对Y、Cb和Cr取样有1 440个取样字(0~1 439)。而对行消隐期间的取样可以有288个取样字(525/60制为276个取样字)。

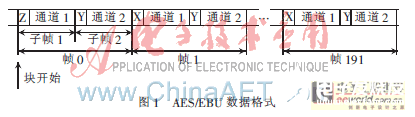

目前辅助数据区也即行消隐区最大的用途是放置数字音频,被放置的数字音频称为嵌入音频。图1是AES/EBU音频数据块结构[1]。

一个音频块由192个连续帧组成,每个帧包含相关的两个子帧,使得一个数字音频码流可以作为立体声、双声道模式使用。这两个子帧(32 bit)分别表示一个音频通道中的一个音频样本,每个子帧的32 bit中包含24 bit的音频数据和一些辅助数据。

音频嵌入就是将每个子帧的32 bit信息按照SMPTE-292[2]标准分别嵌入到3个数据字和一个辅助数据字中,并将这些数据字嵌入到HANC中。解嵌的目的就是把每个音频子帧对应的这4个字找到,按照顺序把这些子帧组合成AES/EBU音频块格式,使输出为直接可识别的音频码流。

2 通用异步FIFO设计

2.1 通用异步FIFO结构

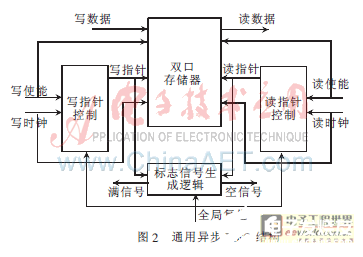

图2所示为通用异步FIFO结构,一般由四个模块构成:数据存储模块、写地址产生模块、读地址产生模块和标志位产生模块。

系统分为读时钟和写时两个完全独立的时钟域。读写两端的使能和时钟信号作为读写指针控制的基础控制输入信号。更新的读写指针既作为存储器的写入读出地址又作为标志信号模块的输入。标志产生模块通过对读写地址的比较来得到存储器的空、满标志信号。将写满信号和读空信号分别反馈到写指针和读指针控制模块,控制指针值的更新。

2.2 亚稳态消除方法

由于读写标志控制分别工作于不同的时钟域,在其产生威廉希尔官方网站 中,如果比较触发器建立时间和保持时间的要求没有得到满足,触发器就会进入一个介于逻辑1和逻辑0的中间状态,称之为亚稳态。为了降低亚稳态发生的概率,可采用格雷码地址计数[3]。二进制计数器在计数值增加时,可能同时会有多位数值发生变化,而格雷码计数器每次加1只有一位数值发生变化。所以将二进制读写指针转换为格雷码,送到另一个时钟域进行比较,可以降低亚稳态发生的概率。

2.3 空、满标志产生

通过对读写格雷码地址高两位的比较,得到存储器工作的满空趋势[4],再比较地址值是否相等最终判断空、满标志。把这两个2 bit数组合成4 bit数的16种组合,可以得到:当写地址格雷码最高两位和读地址格雷码最高两位分别组合为:0001、0111、1110、1000时,存储器趋向满状态;为0100、1101、1011、0010时,存储器趋向空状态。

空、满趋势通过事件触发,随时根据读写地址的更新值进行判断。再结合读写地址的比较结果来最终判断存储器的空、满状态。

3 改进型异步FIFO设计

3.1 改进方案

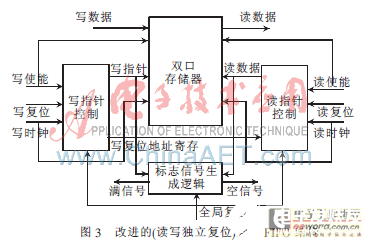

根据AES/EBU音频格式可知,每192帧(384子帧)音频构成一个AES/EBU音频块,作为一个连续输出单位,并用一个Z标志来指示这一音频块的开始。根据这一标准,本文设计了一种专用于该音频格式输出的异步FIFO。该异步FIFO具有单端复位,并根据写地址复位寄存值作为读地址更新的参考,使读数据更可靠。FIFO深度设计为384子帧,位宽为24 bit。当用每个存储单元(24 bit)存储一个子帧中的音频数据码来指示地址时,由于设计深度为384子帧,利用9 bit格雷码来指示地址时,最高两位不会达到10的情况下,那么在满、空标志判断中的趋势判断就可以少考虑一种情况,即写、读地址格雷码最高两位组合为0001、0111、1100时,趋向满;为0100、1101、0011时,趋向空。这种改善,既减小了存储器的大小,又减小了程序的复杂度。

考虑到解嵌的音频信号可能存在丢帧、错帧,有的时候可能一块数据中并没有192帧的数据,而只是一部分数据,因此,在实际工作中需要利用块开始标志Z复位写地址指针。为了保证输出端也能在读地址复位的地方进行复位,保证输出的音频块与输入端对应,本设计提出了利用一个地址寄存器寄存写地址复位时的写地址,并利用该地址作为读地址指针更新参考,这样就增加了读取数据的可靠性。

图3是改进的(读写独立复位)异步FIFO结构。

3.2 设计仿真

系统设计时,利用Quartus II进行RTL级的逻辑设计并综合处理,然后设计仿真平台[5],利用Modelsim仿真工具对整个系统进行门级仿真。根据设计的异步FIFO 的工作特性,仿真平台对FIFO工作到满状态、空状态,以及写指针复位后的读操作进行了较全面的覆盖。

下面是测试平台的激励生成代码:

always #40 wr_clk=~wr_clk;

always #10 rd_clk=~rd_clk;

always @(posedge wr_clk) begin

if(!rstn) begin

wr_data《=0;

cntw《=0;

rd_en《=0;

wr_en《=0;

end

else if(cntw==400) begin

rd_en《=1;

cntw《=cntw+1;

end

else if(cntw==500) wr_rstn=0;

else begin

wr_en《=1;

wr_rstn《=1;

wr_data《=wr_data+1;

cntw《=cntw+1;

end

end

代码的功能是在较低的时钟速率下,先进行写操作,等到确保写满后(即计数达到400时),以高速的读操作来读取数据,并继续写数据。当计数到500时,对写操作复位,此时的复位地址是98。

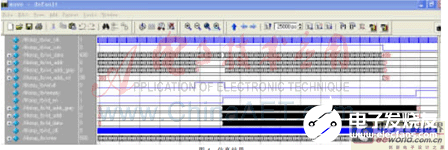

根据上述的改进方法,设计、仿真完成后,用Altera公司的Cyclone Ⅲ系列EP3C10E144C8芯片实现威廉希尔官方网站 程序设计。仿真结果如图4所示。在图中可以看到,wr_addr_rst的值一开始默认为383,但写入端有写复位时,即为写复位时的地址值98,该值也即作为读操作的地址复位参考值传递到读操作模块。等到读操作进行第二轮读取并读到第98个地址时,再复位到0地址时,仿真完成。

本文基于FPGA内部存储器,提出了一种针对视音频解嵌系统更具效率的异步FIFO,对通用的FIFO进行改进,并利用硬件描述语言及相应的仿真工具实现了功能仿真。仿真结果表明,本设计能很好地按照设计的意图工作。此外,还针对视音频解嵌系统中,音频块输出端异步FIFO提出了写复位地址寄存,读地址根据此寄存值来进行更新及复位的改进,提高了异步FIFO的工作效率和可靠性。

-

SDI音频解嵌IP模块设计及应用2010-04-22 0

-

请问怎样去设计一种异步FIFO?2021-06-18 0

-

异步FIFO结构及FPGA设计2009-04-16 650

-

基于PCI接口芯片外扩FIFO的FPGA实现2010-01-06 568

-

一种异步FIFO的设计方法2006-03-24 769

-

用FPGA芯片实现高速异步FIFO的一种方法2014-05-28 3836

-

基于FPGA的异步FIFO设计方法详解2018-07-17 8390

-

基于FPGA的异步FIFO的实现2018-06-21 6513

-

TMS320C67系列DSP的EMIF与异步FIFO存储器的接口设计详细资料介绍2019-07-31 1370

-

异步bus交互(三)—FIFO2021-12-17 511

-

异步fifo详解2022-12-12 4173

-

同步FIFO和异步FIFO的区别 同步FIFO和异步FIFO各在什么情况下应用2023-10-18 1687

-

FPGA学习-异步FIFO原型设计与验证2023-11-17 532

全部0条评论

快来发表一下你的评论吧 !