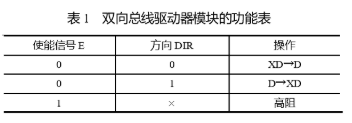

采用可编程器件CPLD实现ARINC429收发威廉希尔官方网站 与接口板的通信设计

可编程逻辑

描述

PC104总线系统是一种新型的计算机测控平台,作为嵌入式PC的一种,在软件与硬件上与标准的台式PC(PC/AT)体系结构完全兼容,它具有如下优点:体积小、十分紧凑,并采用模块化结构,功耗低,总线易于扩充,紧固堆叠方式安装,适合于制作高密度、小体积、便携式测试设备,因此在军用航空设备上有着广泛的应用,但也正是PC104板的这种小尺寸结构、板上可用空间少给设计带来了一定的困难,所以本设计采用了复杂可编程器件CPLD,用CPLD完成了PC104总线与429总线通讯的主要威廉希尔官方网站 ,大大节省了硬件资源,本文着重介绍了CPLD部分的设计。

1 、系统总体设计

CPLD是一种复杂的用户可编程逻辑器件,由于采用连续连接结构,易于预测延时,从而使威廉希尔官方网站 仿真更加准确。再加上使用方便的开发工具,如MAX+PLUSII、Quartus等,使用CPLD器件可以极大地缩短产品开发周期,给设计修改带来很大方便。本论文描述了利用开发工具MAX+PLUS II实现CPLD处理ARINC429数据通信。系统设计方案如图1所示。

ARINC429收发威廉希尔官方网站 部分,由两组3282和3l82芯片构成,其中每组芯片实现二路接收、一路发送,其中的控制信号均有CPLD编程产生:在CPLD部分,D[0.。.15]为16位双向数据总线,实现AR1NC429收发威廉希尔官方网站 与PC104总线接口之间的数据通信,IO16为16位芯片选择信号;在PC104总线接口部分,XD[0.。.15]为16位双向数据总线,XA[1.。.9]为地址总线,连接CPLD,进行选片操作,XIOR和XIOW 为IO读写信号,XAEN 是允许DMA控制地址总线、数据总线和读写命令线进行DMA传输以及对存储器和I/O设备的读写。

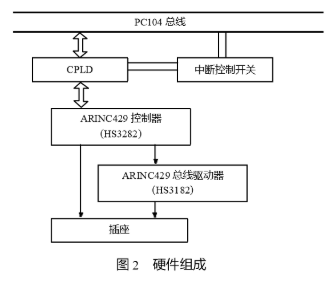

2、 系统硬件组成

429的PC104总线接口板的硬件组成框图如图2所示,主要包括AR1NC429收发威廉希尔官方网站 (HS3282和HS3l82芯片组)、CPLD、429板与PC 机的接口总线PC104总线、与外部的429接口IDC16插座、中断控制开关等,其关系如图2所示。

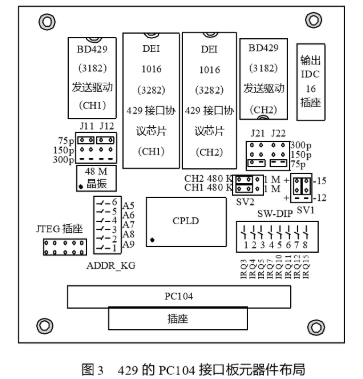

本接口板元器件布局如图3所示。

3、 CPLD内部功能及实现

3.1 开发流程描述

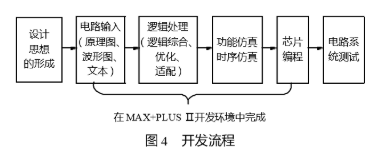

本系统中的CPLD使用Altera公司的MAX7000S系列可编程逻辑器件中的EPM7128SQC100-6型号,从最初的威廉希尔官方网站 设计思想到MAX+PLUSII的波形仿真,再到CPLD芯片编程结束要经过的一般开发流程如图4所示。

3.2 CPLD中的模块设计

本设计中CPLD 的功能是实现ARINC429收发威廉希尔官方网站 与接口板的接口总线PC104总线的数据通信。其功能模块可以分为6部分,以下逐一介绍各模块的功能及其实现的方法。

(1)产生AR1NC429控制器HS3282所需的TTCLK时钟信号模块

TTCLK即发射器时钟信号,本设计中该信号有480 KHZ和1 MHZ两种可选频率,是由一个48 MHZ的晶振提供信号给CPLD,然后由CPLD编程产生480KHZ和1MHZ两种信号以备选择。该模块用图形编辑的方式实现。要产生3282所需要的480KHZ信号需要对输入48MHZ信号进行两次10分频,要产生1 MHZ信号需要对输入信号进行6分频再8分频。6分频威廉希尔官方网站 采用3个JK触发器实现,8分频威廉希尔官方网站 采用74393实现,10分频威廉希尔官方网站 采用7490实现。

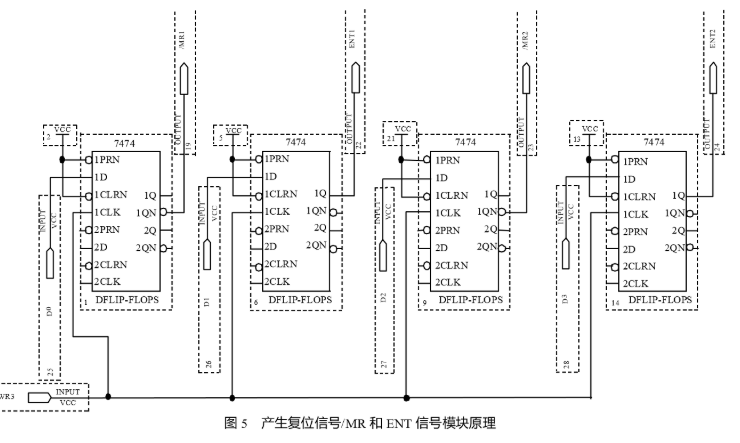

(2)产生复位信号/MR和控制发射器使能信号ENTX的信号ENT模块/MR是对3282的主复位信号,/MR将直接送到HS3282,而ENT将送到另一模块中,用于控制发射器使能信号ENTX的产生,ENTX=ENT*/TXR,其中TXR为发送缓冲区空标志。该模块也采用威廉希尔官方网站 设计输入方式。其威廉希尔官方网站 主要由4个D型触发器74LS74芯片来完成。输入为总线驱动器的前4个输出,即D0~D3,时钟脉冲为产生HS3282读写信号模块的一个输出信号/WR3,输出为两个HS3282的复位信号/MR1和/MR2以及ENT1和ENT2。本模块具体实现威廉希尔官方网站 如图5所示。

(3)产生片选信号/MCS的模块

本模块产生的/MCS信号用于驱动双向总线驱动器,进行数据传输,并用于选片对HS3282进行读写。此模块用一片8位判决威廉希尔官方网站 74LS688来实现其功能。其中P5-P1接一组基址选择开关,Q5~Q1分别接PC104总线的地址总线的XA7、XA9、XA8、XA6和XA5,G接PC104总线的地址使能信号端XAEN。只有当XAEN输入为低时,并且P5~Pl与Q5-Q1的对应端相等时,输出为低,才有效。

(4)双向总线驱动器模块

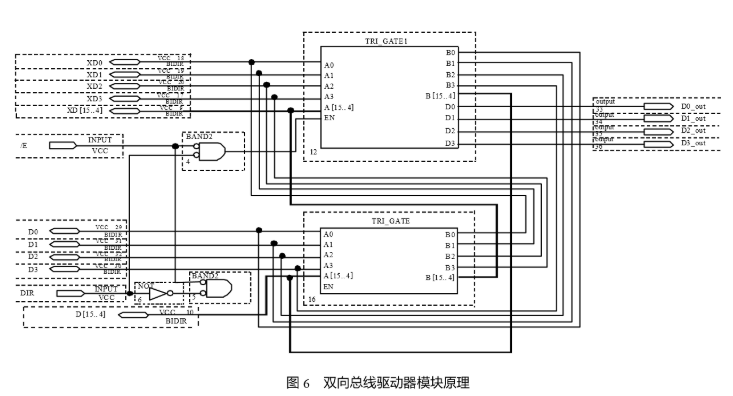

该模块实现AR1NC429收发威廉希尔官方网站 与接口板的接口总线PC104总线的16位数据传输。该模块设计过程为,先用VHDL设计输入方式设计两个单向三态数据收发器,然后用威廉希尔官方网站 设计输入方式,将两个单向数据收发器合成为一个双向数据收发器。

双向总线驱动器模块产生其一个单向三态数据收发器(TRI_GATE1)的VHDL语言设计如下

library ieee;

use ieee.std_logic_1164.all;

entity tri_gate1 is

port(a0,al,a2,a3:in std_ logic;

a:in std_logic_vector(15 downto 4);

en:in std_logic;

b0,b1,b2,b3:out std_logic;

b:out std_logic_vector(15 downto 4):

D0,D1,D2,D3:out std_logic);

--向模块2中送数据的4个输出端

end tri_gatel;

architecture behav of tri_gate1 is

begin

process

begin

if en=‘1’ then --EN为高电平时收发器有效

b0《=a0;b1《=a1;b2《=a2;b3《=a3;b《=a;

D0《=a0;D1《=a1;D2《=a2;D3《=a3;

else --EN为低时高阻状态

b0《=一Z;b1《=-Z;b2《=-Z ;b3《=‘Z’;b《=“ZZZZZZZZZZZZ”;

end if

end process;

end behav;

产生另一个单向三态数据收发器(TRI_GATE)的VHDL语言与此类似,只是少了D0~D3的输出部分。两个单向三态数据收发器构成双向总线驱动器的威廉希尔官方网站 设计如图6所示(D0_out~D3_out作为图5中的D0-D3输入)

(5)产生HS3282读信号与写信号和ENTX使能信号模块

本模块要实现的功能是产生HS3282的读写信号和发送使能信号及一个送入PC104总线的输入输出16位芯片选择信号/IO16。该模块用VHDL语言输入,其相应的VHDL语言如下

library ieee;

use ieee.std logic_1164.all;

entity gal4243 is

port(MCS,XIOW,XIOR,A1,A2,A3,A4,ENT1,

ENT2,TXR1,TXR2: in std_logic;

WR0,W Rl,WR2,W R3,WR4,W R5,W R6:

out std_logic;

RD0,RD1,RD2,RD3,RD4:out std_logic;

IO16,ENTX1,ENTX2:out std_logic);

end gal4243;

architecture behav of gal4243 is

begin

process

begin

WR6《=XIOW or MCS or A4 or(not A3) or(not A2)or A1;

WR5《=XIOW or MCS or A4 or(not A3) or A2 or(not A1);

WR4《=XIOW or MCS or A4 or(not A3) or A2 or A1;

WR3《=XIOW or MCS or A4 or A3 or(not A2)or(not A1);

WR2《=XIOW or MCS or A4 or A3 or(not A2)or A1;

WR1《=XIOW or MCS or A4 or A3 or A2 or(not A1);

WR0《=XIOW or MCS or A4 orA3 or A2 or A1; --产生写信号

if MCS=‘0’ then

IO16《=MCS;

else

IO16《=‘Z’;

endif;

RD4《=XIOR or MCS or(notA4)orA3 or A2;

RD3《=XIOR or MCS or A4 or(not A3)or(not A2);

RD2《=XIOR or MCS or A4 or(not A3)or A2;

RDI《=XIOR or MCS or A4 or A3 or(not A2)

RD0《=XIOR or MCS or A4 or A3 orA2;--产生读信号

ENTX1《=ENT1 and(not TXR1);

ENTX2《=ENT2 and(not TXR2);--产生发送使能信号

end process;

end behav;

(6)中断控制模块

本模块用于实现中断控制操作,有一个接收器满便产生中断,产生中断时亦能判断出中断源。该模块是用VHDL输入方式产生的,其相应的VHDL程序如下

library ieee;

use ieee.std logic_1164.all;

entity U32 is

port(TXR1,DR11,DR12,TXR2,DR21,DR22,RD4:in std_logic;

D0,D1,D2,D3,D4,D5,INT:out std_logic);

end U32;

architecture behav of U32 is

begin

process

begin

if RD4=‘0’ then

D0《=not DR11:

D1《=not DR12;

D2《=not DR21;

D3《=not DR22;

--产生中断时用来判断哪个接收器满

D4《=TXR1;

D5《=TXR2;

--用来判断哪一个发送缓冲区空

else

D0《=‘Z’;D1《‘Z’;D2《=‘Z’;D3《=‘Z’;D4《=‘Z’;D5《=‘Z’;

endif;

INT《=not(DR11 and DR12 and DR21 and DR22); --有一个接收器满便产生中断

end process;

end behav;

3.3 CPLD程序的下载

各输入模块经过编译处理,根据其相互关系连结,再通过功能仿真和时序仿真确认无误后,对各输入输出端口进行管脚分配。当整个设计完成时,MAX+PLUSII将生成一个文件(.pof),该文件通过下载电缆从JTAG口传送到PC104板上的CPLD芯片内部。这样就可将CPLD构造成自己的专用芯片,由此便可以对设计的PC104板卡进行调试。调试过程中CPLD的设计部分还可根据需要进行修改,只是修改后要重新产生.pof文件,重新将文件加载到芯片中。

4、 结束语

针对PC104接口板的尺寸小的特点,本论文介绍了用CPLD实现基于PC104总线的429接口板,CPLD大大节省了硬件资源,同时也节省了板卡上的可利用空间,彻底解决了PC104 板卡的小尺寸给设计带来的困难。且CPLD修改简单,给调试工作带来了方便。该板卡经过调试后实验,可稳定工作。实验结果表明:应用CPLD简化了系统结构,缩短了设计周期,提高了系统的可靠性。

责任编辑:gt

-

基于USB的ARINC429总线接口模块设计2008-10-14 0

-

基于PC/104设计与实现ARINC429接口模块2019-04-16 0

-

采用专用接口威廉希尔官方网站 PCI9054实现ARINC429总线接口板设计2019-04-26 0

-

采用NIOS II实现ARINC429总线接口板设计2019-04-29 0

-

多通道ARINC429总线数据接收和发送的实现2019-06-13 0

-

怎么设计便携式ARINC429总线通信设备?2019-08-19 0

-

如何用CPLD实现基于PC104总线的429接口板的设计?2021-04-29 0

-

怎样去设计ARINC429总线接口板?有哪些步骤?2021-05-27 0

-

FPGA可编程器件和CPLD可编程器件有哪些相同点和不同点2021-11-10 0

-

基于DSP的ARINC429通信板设计2009-07-08 540

-

航空用ARINC429总线收发系统设计与实现2009-07-16 862

-

基于NIOSⅡ的ARINC429总线接口板设计2010-12-07 504

-

PCI总线ARINC429通信卡实现方法2011-05-18 782

-

基于PCMCIA 的ARINC429 通信卡设计2016-03-15 905

-

如何使用FPGA实现ARINC429接口和总线数据接收2021-02-03 1664

全部0条评论

快来发表一下你的评论吧 !