基于复杂可编程逻辑器件实现数据采集系统的软硬件设计

可编程逻辑

描述

1 引言

以往的数据采集系统多数采用单片机、DSP等微处理器产生A/D转换芯片所需要的控制时序,以及通道转换所需要的时序逻辑信号,这样会占用CPU较多的时间。本文介绍基于CPLD的高速高精度数据采集系统设计方法,所需控制时序及地址译码等威廉希尔官方网站 均由CPLD产生,并将转换结果放于双端口RAM中,CPU随时从双端口RAM中读取转换结果,大大提高系统的数据采集速度。

在某些控制系统中,其数据采集除了要满足最基本的精度和速度要求外,还必须在动态范围、分辨率等指标上满足要求。普通的高位数A/D在转换精度和速度上难以兼顾,例如目前市场上∑-Δ型串行输出24位A/D,其转换时间都在ms级,不能满足高速数据采集的要求,为了在较低成本的前提下仍能获得较高的动态范围和采集速度,设计中采用了基于CPLD控制的带浮点放大器的两级并行A/D转换方案,系统在小信号输入时放大较高的倍数,以增加A/D转换的有效位数,在大信号时放大较低的倍数,截断小量保证信号的主要部分,既保证了数据采集系统的动态测量范围,同时又兼顾到系统的采集精度和速度。

2 带浮点放大器的CPLD数据采集系统硬件设计

2.1 系统硬件整体框图

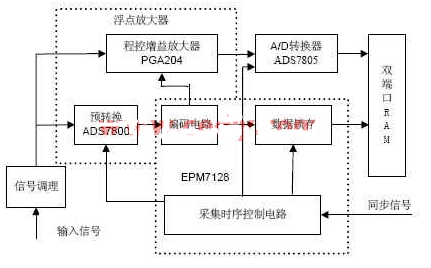

带浮点放大器的CPLD高速高精度数据采集系统硬件威廉希尔官方网站 如图1所示,它由模拟信号输入调理威廉希尔官方网站 、程控放大器PGA204、A/D 转换器ADS7800和ADS7805、双端口存储器IDT7134、数据采集时序控制器EPM7128等构成。

所需控制时序及地址译码等威廉希尔官方网站 均由可编程逻辑器件EPM7128产生,CPLD通过编程用多种计数器、逻辑威廉希尔官方网站 、时钟威廉希尔官方网站 等组成的纯硬件子系统实现A/D的控制、转换、读取时序,不仅节省了PCB面积,减少了整个系统结构的复杂程度,提高了系统的可靠性。

图1 带浮点放大器的CPLD多通道数据采集系统硬件威廉希尔官方网站 图

浮点放大器的结构如图1的上方虚线框内所示,主要由12位的预转换A/D转换器ADS7800、编码威廉希尔官方网站 和程控增益放大器PGA204组成。首先,输入信号接入预转换威廉希尔官方网站 ,根据ADS7800的输出结果,由编码威廉希尔官方网站 判断输入信号的范围,设定程控放大器的放大倍数(1、10、100、1000倍四个档);程控放大威廉希尔官方网站 主要是根据编码威廉希尔官方网站 确定下来的增益码实现对输入信号的放大,在不超出16位A/D输入范围的前提下,尽量将信号放大足够的倍数,以扩大数据采集系统的动态范围,随后将放大适当倍数的模拟信号再送入16位A/D转换器。浮动的放大倍数称为“阶码”,16位A/D转换结果称为“尾码”,数据采集系统的输出结果由“阶码”+“尾码”组成,这类似于计算机中浮点数的表达方式,“浮点”放大器也因此得名。

系统采用了具有高速采集保持功能的转换器ADS7800,它支持双极性模拟量输入,输入范围±10V、±5V可选,内部具有时钟和电压参考,采样速率可高达333kHz,从而保证了信号分档的速度。美国BB公司出品的16位A/D芯片ADS7805具有如下突出特点:(1)自带采样/保持器,方便对交流信号的采样;(2)最高采样频率可达100kHz;(3)转换结果全16位并行输出,具有三态缓冲功能,与16位数据总线接口方便;(4)提供±10V的输入范围,与工业标准兼容;(5)单+5V电源供电,可方便地与其它芯片接口。

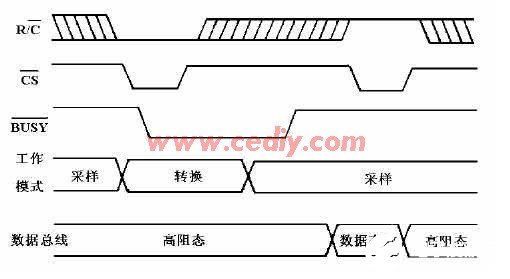

2.2 ADS7800和ADS7805的时序

图2 A/D转换器的工作时序图

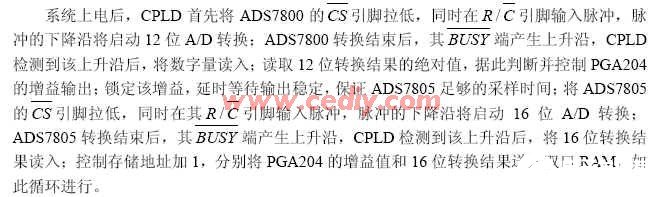

2.3 系统工作流程

数据采集子系统的主要控制流程如下:输入信号接入ADS7800进行预转换;编码威廉希尔官方网站 将ADS7800的12位转换结果,取其绝对值,并根据输入信号落在那个区间,确定程控放大器的增益,取得“阶码”;锁定增益数值,经适当放大后的信号送入A/D转换器ADS7805取得16位的有效“尾码”;将“阶码”和“尾码”送入双端口RAM保存;切换地址重复上述过程。

从上述过程可以看出时序逻辑控制威廉希尔官方网站 必须保证两片A/D转换器的转换与结果存储、读取协调可靠有序地运行,时序控制威廉希尔官方网站 应当自动生成A/D控制信号以及共享RAM的写入、地址等信号。

3 数据采集系统软件设计

运用VHDL硬件设计语言,采用状态机方法对CPLD进行编程实现流水控制。下面以对ADS7800和PGA204组成的浮点放大器的控制为例,CPLD简要程序如下:

ARCHITECTURE AD_CPLD OF adnew_test IS

PROCESS(clockin)

begin

if Reset=‘1’ then

RC12《=‘1’;

state《=s0;

elsif clockin‘event and clockin=’1‘ then

busy_12n1《=busy_12n2; --判断ADS7800的BUSY端是否上升沿

busy_12n2《=Busy12; --读取ADS7800的BUSY端状态

busy_12pd《=not busy_12n1 and busy_12n2;

case state is

when s0=》

RC12《=’1‘;

state《=s1;

when s1=》 --启动ADS7800

RC12《=’0‘;

state《=s2;

when s2=》

RC12《=’1‘;

state《=s3;

when s3=》

if busy_12pd=’1‘ then --ADS7800转换结束

Data_fw《=Data12_in; --读取ADS7800结果

state《=s4;

end if;

when s4=》 --转换结果取绝对值

if Data_fw》2047 then --》7FFH

Temp_fw《=Data_fw AND “011111111111”;

else

Temp_fw《=not Data_fw AND “011111111111”;

end if;

state《=s5;

when s5=》 --PGA204的增益控制

if Temp_fw《3 then

PGA_G《=“11”; --放大1000倍

else

if Temp_fw《20 then

PGA_G《=“10”; --放大100倍

else

if Temp_fw《200 then

PGA_G《=“01”; --放大10倍

else

PGA_G《=“00”; --放大1倍

end if;

end if;

end if;

state《=s0;

when others=》 --初始化状态;

state《=s0;

end case;

end if;

end PROCESS;

END AD_CPLD;

4 结束语

本文作者创新点:所设计的带浮点放大器的CPLD数据采集系统,其浮点放大器在小信号输入时放大较高的倍数,在大信号时放大较低的倍数,保证了数据采集系统的动态测量范围;双端口RAM作为A/D转换与CPU之间的桥梁,为高速数据吞吐提供了有力的硬件支持;CPLD具有大量I/O管脚和较强的带载能力,内部资源丰富、处理速度快, 可实现灵活多变的控制流程;结合以上几方面的优势,系统总体上实现了对输入模拟信号的高速、高精度数据采集。该系统已应用于本人参与设计的MSINS/GPS微小型组合导航系统中,已产生经济效益20余万元;该数据采集系统也可以广泛应用于需要宽输入范围、高精度、高采样速度和数据处理速度的智能仪器设计中,经济效益将会相当可观。

责任编辑:gt

-

基于复杂可编程逻辑器件(CPLD)的120MHZ高速A/D采集卡的设计2011-03-05 0

-

可编程逻辑器件2014-04-15 0

-

如何采用可编程逻辑器件和A/D转换器组成高速数据采集卡?2021-04-15 0

-

求一种基于复杂可编程逻辑器件的硬件校正实现方案2021-04-28 0

-

PLD可编程逻辑器件2021-07-22 0

-

可编程逻辑器件设计2006-03-25 1021

-

基于复杂可编程逻辑器件(CPLD)的120MHZ高速AD采集2010-01-17 721

-

可编程逻辑器件基础及应用实验指导书2010-03-24 629

-

基于单片机的复杂可编程逻辑器件快速配置方法2009-03-28 857

-

什么是PLD(可编程逻辑器件)2009-06-20 26248

-

EDA技术与应用(可编程逻辑器件)2012-05-23 915

-

可编程逻辑器件(书皮)2022-07-10 455

-

采用复杂可编程逻辑器件实现多路信号采集系统的设计2020-03-03 1507

-

基于可编程逻辑器件和VHDL语言实现信号源的方案设计2020-08-07 1428

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 2841

全部0条评论

快来发表一下你的评论吧 !