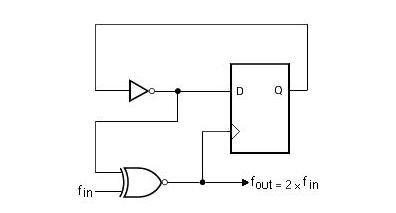

数字倍频威廉希尔官方网站 原理图

电子说

1.3w人已加入

描述

一个数字倍频威廉希尔官方网站

这个就是原理图,奉上代码

1 ///////////////////////////////////////////////////////////////////////////// 2 // DATE : Wed Jun 6 22:58:17 CST 2012 3 ///////////////////////////////////////////////////////////////////////////// 4 module clk_mul( 5 input wire clk 6 , input wire rst_n 7 , output wire clk_out 8 ); 9 ////////////////////////////////////////////////////////////////////////////// 10 // variable declaration 11 reg temp_mul ; 12 ////////////////////////////////////////////////////////////////////////////// 13 // logic 14 always @(posedge clk_out or negedge rst_n) begin 15 if(~rst_n) temp_mul <= 1'b0 ; 16 else temp_mul <= #2 ~temp_mul ; 17 end 18 assign clk_out = ~(clk ^ ~temp_mul) ; 19 ////////////////////////////////////////////////////////////////////////////// 20 21 endmodule // CREATED by poiu_elab@1207 22 23 //////////////////////////////////////////////////////////////////////////////

这个东西很简单的,但是要注意,它的核心是第16行的#2,这里的延时(占空比)可以通过威廉希尔官方网站 的Tco和经过反相器的时间来搞定(其中可以插入一些buffer来调节时间),testbench这么来写(很简单,但是便于下面解释延时对占空比的影响还是附上)。

1 /////////////////////////////////////////////////////////////////////////////// 2 // DATE : Wed Jun 6 23:00:31 CST 2012 3 /////////////////////////////////////////////////////////////////////////////// 4 `define CLK_CYCLE 20 5 module tb(); 6 /////////////////////////////////////////////////////////////////////////////// 7 // variable declaration 8 reg clk ; 9 reg rst_n ; 10 wire clk_out ; 11 /////////////////////////////////////////////////////////////////////////////// 12 // stimulation generation 13 initial forever #(`CLK_CYCLE/2) clk = ~clk; 14 initial begin 15 rst_n = 1'b0 ; 16 clk = 1'b1 ; 17 #500; 18 rst_n = 1'b1 ; 19 #5000; 20 $stop; 21 end 22 /////////////////////////////////////////////////////////////////////////////// 23 // module instaniation 24 clk_mul u_clk_mul( 25 .clk ( clk ) 26 , .rst_n ( rst_n ) 27 , .clk_out ( clk_out ) 28 ); 29 /////////////////////////////////////////////////////////////////////////////// 30 31 endmodule // CREATED by poiu_elab@1207 32 33 ///////////////////////////////////////////////////////////////////////////////

下面给出仿真图,当#2的时候,是这样的,其中你要关心的其实是~temp_mul & clk, 当你要是q端经过反相器的信号与接入的clk信号相同的时候你的clk_out就会起来,之后你的q端翻转了的话,你的clk_out就会落下来,这时候在下一个clk翻转的时候,你的~temp_mul & clk就会又要把clk_out拉起来,q端又翻转,以此类推,就可以继续在每个clk的跳变沿出现你的clk_out的高电平,调整你的Tco和反相器延时就可以调整你的高电平时间,由于周期又是固定的,这样就可以调整你的占空比。

而当#5的时候,是这样的

看出什么端倪了没,当你的延时,正好是时钟周期的1/4的时候,你就可以得到一个占空比是50%的2倍频时钟。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 反相器

- 倍频威廉希尔官方网站

-

威廉希尔官方网站 图:数字无线接收威廉希尔官方网站 原理图2012-07-31 0

-

长虹倍频DT2000彩电威廉希尔官方网站 图2009-05-08 598

-

单片数字锁相倍频威廉希尔官方网站 的设计与实现2009-09-14 1411

-

低频倍频器威廉希尔官方网站 图2009-03-31 1731

-

宽带倍频器威廉希尔官方网站 图2009-03-31 663

-

倍频威廉希尔官方网站 (MC1596)的应用威廉希尔官方网站 图2009-04-05 4532

-

方波倍频威廉希尔官方网站 图2009-04-09 7151

-

四倍频器威廉希尔官方网站 图2009-04-09 1767

-

倍频威廉希尔官方网站 图2009-05-08 2932

-

具有50%占空比的倍频器威廉希尔官方网站 图2009-05-18 1252

-

倍频器威廉希尔官方网站 图2009-07-20 2562

-

基于VHDL的数字倍频器设计2011-12-07 1145

-

数字时钟威廉希尔官方网站 设计原理图pcb图2015-12-07 4928

-

码盘四倍频的威廉希尔官方网站 原理图免费下载2019-10-25 1348

-

数字威廉希尔官方网站 如何实现倍频?2023-09-18 7375

全部0条评论

快来发表一下你的评论吧 !