如何在FPGA内实现扰码过程

电子说

描述

一、扰码的作用

对数字信号的比特进行随机处理,减少连0和连1的出现,从而减少码间干扰和抖动,方便接收端的时钟提取;同时又扩展了基带信号频谱,起到加密的效果。为了保证在任何情况下进入传输信道的数据码流中“0”与“1”的概率都能基本相等,传输系统会用一个伪随机序列对输入的传送码流进行扰乱处理,将二进制数字信息做“随机化”处理。

二、扰码的原理

伪随机序列是由一个标准的伪随机序列发生器生成的,其中“0”与“1”出现的概率接近50%。用伪随机序列对输入的传送码流进行扰乱后,无论原始传送码流是何种分布,扰乱后的数据码流中“0”与“1”的出现概率都接近50%。扰乱虽然改变了原始传送码流,但这种扰乱是有规律的,可以在接收端解除。将待发送的信息序列与发端产生的m序列进行模二加(扰码),扰码序列通过传输信道传送到接收端,接收端接收到扰码序列,使用同样的m序列进行模二加,即可恢复原来的信息。

三、扰码实现方法

1. 数学模型

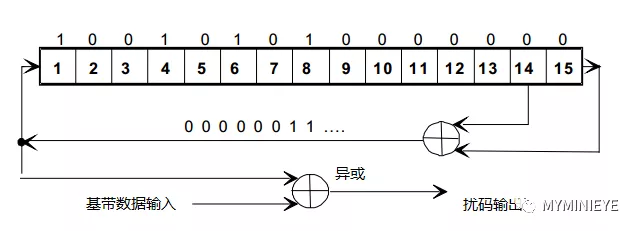

扰码模块对每个数据块进行随机化处理,随机化序列和数据块同步,每个数据块都要重新初始化随机序列,随机化从数据块的 MSB 位开始处理,K_BCH 位结束(K_BCH为定义的数据输入长度)。扰码序列的生成多项式为1+X14+X15,初始序列为100101010000000,扰码实现结构如下:

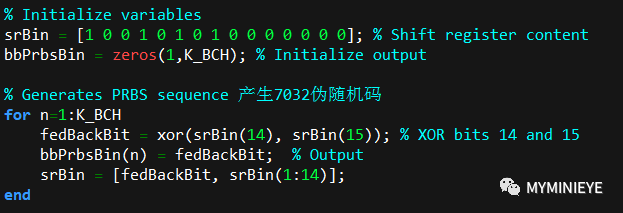

matlab代码

根据以上结构,在matlab里产生伪随机序列,函数代码如下,其中K_BCH 为7032,为一组数据的长度,运行得到7032长度的伪随机序列码。

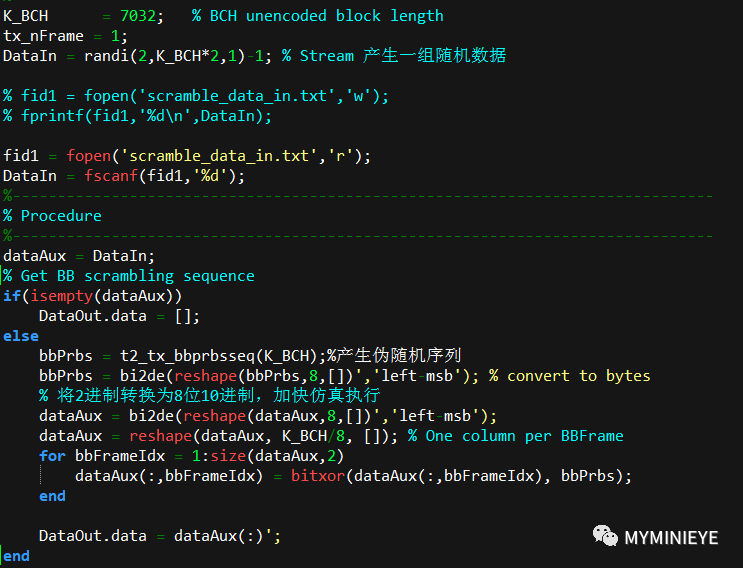

产生一组随机数据,用作数据的输入,与此同时,这个数据也被用作modelsim的数据输入。输入数据和m序列作模二加,即异或,进行扰码处理,得到最终输出,扰码的matlab的程序如下

3. FPGA实现

在FPGA内实现扰码过程的,并不复杂,主要是信号的控制,这里使用AXI总线的结构,定义模块的输入输出接口如下

|

名称 |

方向 |

有效状态 |

描述 |

|

clk |

in |

- |

时钟,上升沿有效 |

|

rstn |

in |

low |

同步复位 |

|

s_data_tvalid |

in |

high |

输入数据有效信号 |

|

s_data_tdata[0:0] |

in |

- |

数据输入 |

|

s_data_tready |

out |

high |

准备接收数据使能 |

|

s_data_tlast |

in |

high |

表示输入最后1bit数据 |

|

m_data_tvalid |

out |

high |

数据输出有效信号 |

|

m_data_tdata[0:0] |

out |

- |

数据输出 |

|

m_data_tready |

in |

high |

下一模块接收准备使能 |

|

m_data_tlast |

out |

high |

表示输出最后1bit数据 |

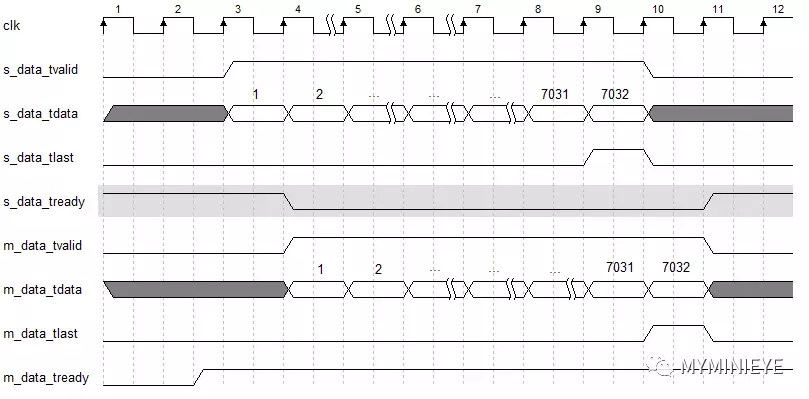

该模块主要处理基于数据块的操作,每个数据完成一次扰码操作,并且每一帧的初始扰码移位寄存器均要初始化。应满足的时序如下

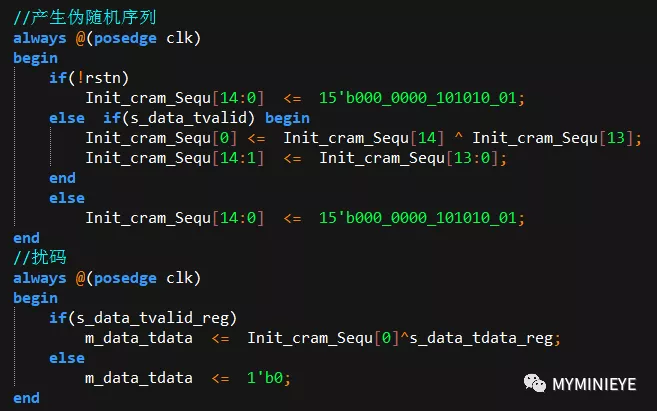

完成的功能为伪随机序列的产生和数据扰码两个过程,如下

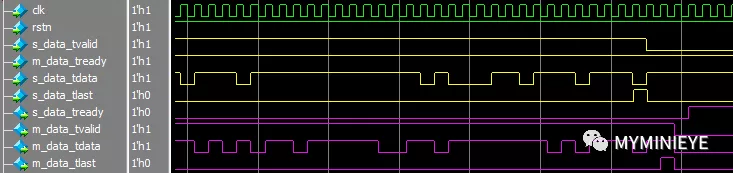

通过modelsim仿真波形,可以看到,输入数据经过扰码之后的输出能够减少连1的出现。

4. 数据比对

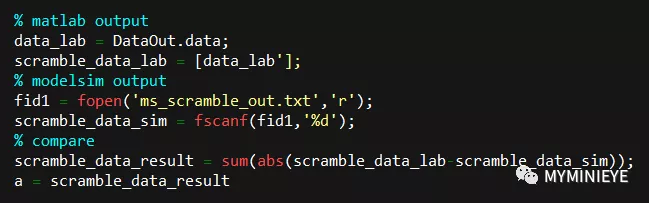

对同一输入数据,用matlab和FPGA分别进行扰码操作,然后把结果写入到本地,通过对比,验证Verilog代码的正确性。

编辑:hfy

全部0条评论

快来发表一下你的评论吧 !