xilinx7系列FPGA新设计的IO专用FIFO解析

电子说

描述

之前介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念——IO_FIFO。

1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。

FPGA的每个BANK有4个IN_FIFO和4个OUT_FIFO,相当于每12个IO对应1个IN_FIFO和1个OUT_FIFO。

IN_FIFO从ILOGIC接收4bit位宽的输入数据,但却可以输出4bit或者8bit位宽的数据到FPGA内部SLICE。OUT_FIFO正好相反,从OLOGIC接收4bit或者8bit位宽的输入数据,但却输出4bit位宽数据。

每一个IO_FIFO的存储大小为768bit,可以配置成12组4X4位宽数据的FIFO,也可以配置成10组4X8bit位宽数据的FIFO。每个IO_FIFO的深度为9。如图1所示为IO_FIFO的结构示意图:

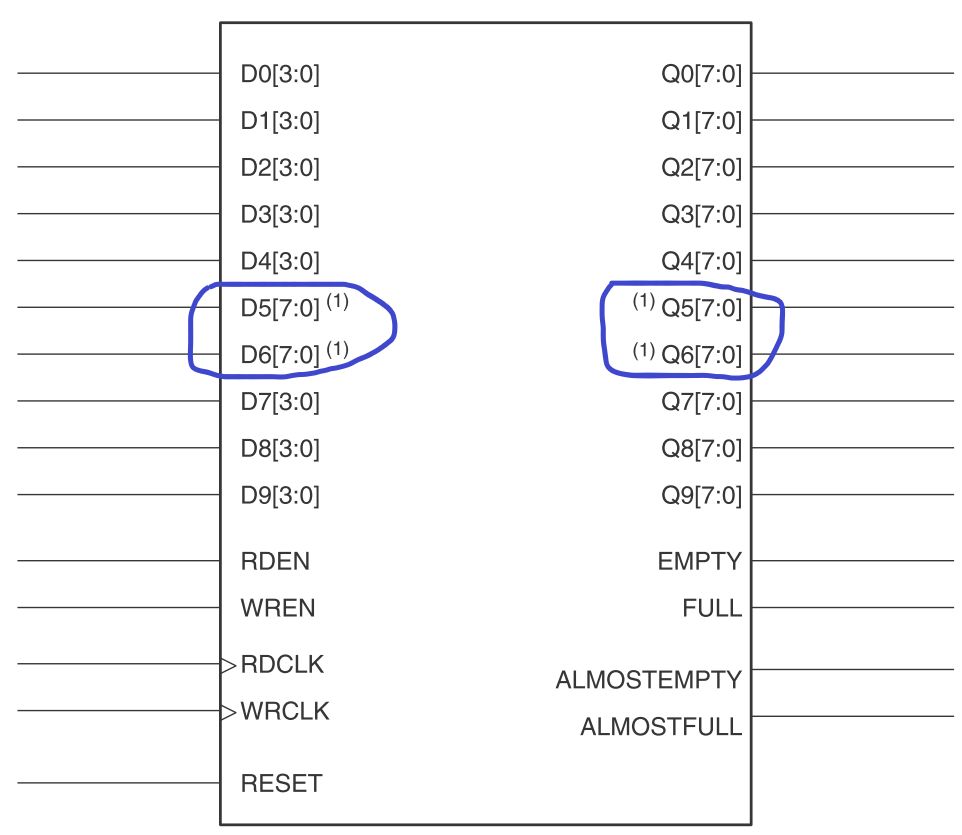

如图2所示为IN_FIFO的原语框图:

正如前面所说,当配置成12组的4bit位宽输入,4bit位宽输出时,输入D0[3:0]~ D9[3:0]对应输出Q0[3:0]~ Q9[3:0];输入D10[3:0]即为输入D5[7:4],对应输出Q5[7:4];输入D11[3:0]即为输入D6[7:4],对应输出Q6[7:4]。

当配置成10组4bit位宽输入,8bit位宽输出时,D0[3:0]~D9[3:0]对应输出Q0[7:0]~ Q9[7:0],此时写时钟频率是读时钟频率的2倍。OUT_FIFO和IN_FIFO操作过程正好相反,咱们这里就不罗嗦了。

总的来说,IO_FIFO其实就是存储深度比较小、位宽固定为4/8bit的普通FIFO ,7系列FPGA单独设计了这样的FIFO,更适用于IO接口处的字节/半字节数据缓存。

编辑:hfy

-

1.Xilinx7系列普及讲座之-----Xilinx7系列IO使用规则2013-03-31 0

-

2.Xilinx7系列普及讲座之-----Xilinx7系列Clocking资源2013-03-31 0

-

3.Xilinx7系列普及讲座之-----Xilinx7系列Memory资源2013-03-31 0

-

Xilinx7系列IO实现差分信号2020-12-23 0

-

FPGA从Xilinx 的7系列学起(8)2017-02-08 442

-

Xilinx7系列FPGA包装和插脚产品规范的资料免费下载2019-02-20 848

-

xilinx7系列FPGA的7种逻辑代码配置模式2019-10-20 3081

-

Xilinx 7系列FPGA时钟资源2020-12-10 942

-

Xilinx7系列FPGA选择资源用户指南2020-12-10 953

-

Xilinx7系列FPGA IO资源的电气特性2020-12-29 872

-

Xilinx7系列FPGA管脚定义与Pinout文件下载2022-07-11 3549

-

xilinx7系列FPGA的应用及功能解析——chiptuo(芯片拓展者)2023-05-12 1138

-

Xilinx 7系列FPGA的时钟结构解析2023-08-31 2622

-

Xilinx 7系列FPGA功能特性介绍2024-04-22 5383

-

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性2024-11-05 772

全部0条评论

快来发表一下你的评论吧 !