集成在IC中的I²CI / O单元结构

描述

I²C是一种同步,多主控,多从属串行接口,允许微€€芯片相互通信。作为漏极开路/集电极开路的通信标准,即使集成威廉希尔官方网站 使用不同的电压轨,I²C也允许集成威廉希尔官方网站 (IC)进行通信。

I²C标准的四种速度

I²C标准具有四种运行速度:

标准模式:100 kHz

快速模式:400 kHz

快速模式加:1 MHz

高速模式:3.4 MHz

I²C总线:串行数据和串行时钟的 I²C总线使用两根线串行数据(SDA)和串行时钟(SCL) -和所有I²C主从设备仅通过这两条线相连接。每个设备既可以是发射机,也可以是接收机。

SDA和SCL信号都是双向的。每个器件的SDA和SCL引脚均为漏极开路引脚。它们具有连接到其的上拉电阻以获得逻辑1。逻辑1取决于电源电压;逻辑1取决于电源电压。没有标准的总线电压。

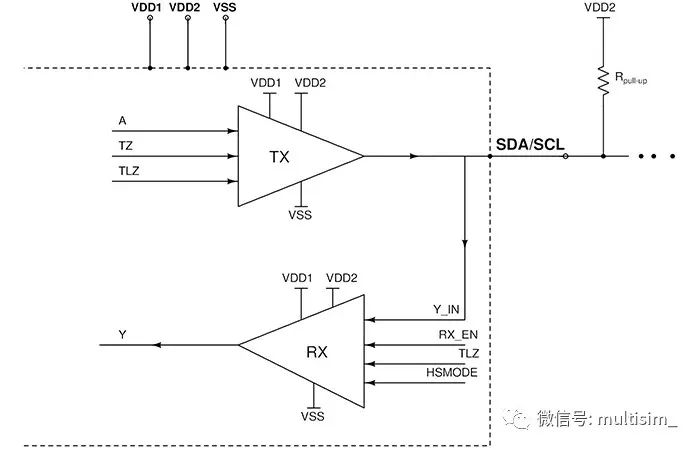

I²C细胞结构让我们讨论集成在IC中的I²CI / O单元结构。I²CI / O单元结构的框图如图1所示。

图 1.I²CI / O驱动器框图 在发送时间范围内使能TX块,而在接收时间范围内使能RX块。

VDD1和VDD2是主器件和从器件工作的两个不同的电压轨。VDD1是内部操作的芯片电源,而VDD2是外部系统使用的电源电压。为了支持不同的电压轨,需要一个电平转换器将信号从一种电源电压转换为另一种电源电压。

I²C模块中的发送器威廉希尔官方网站

发送器威廉希尔官方网站

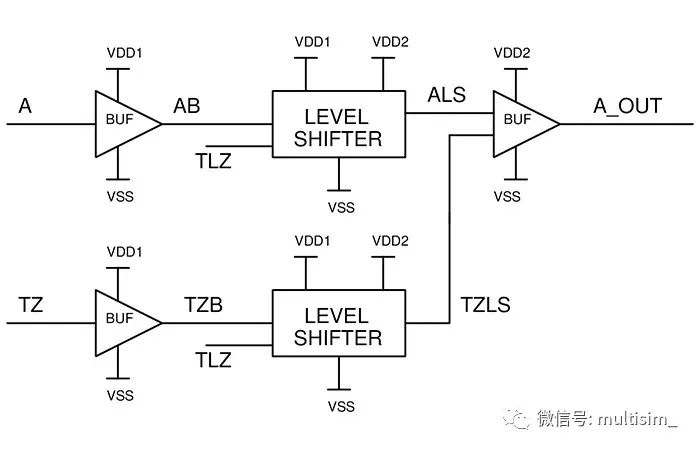

框图如图2所示。

图2.发送器框图

A是要在引脚SDA / SCL上发送出去的数据信号。VDD1掉电期间,TLZ是三态控制。TZ从VDD1移位到VDD2,以使能A_OUT的输出漏极开路缓冲器。

如果在系统运行过程中有意或无意地使VDD1掉电,而VDD2仍处于活动状态,则TZ使能信号变低或不确定。这可以使输出缓冲器为A_OUT。

TLZ信号用作故障安全机制。TLZ在掉电期间被拉低,从而将TZ信号拉高。此时,不再启用输出缓冲区。当VDD1掉电时,漏极开路缓冲器将处于三态状态。

要了解有关使用I²C缓冲器的用例,好处和应用的更多信息,请查阅AAC关于何时使用I²C缓冲器的技术文章。

I²C模块中的接收器威廉希尔官方网站

接收器威廉希尔官方网站

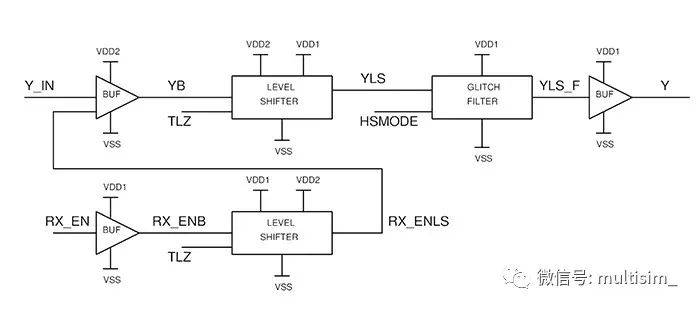

框图如图3所示。

图3.接收器框图

接收器威廉希尔官方网站

通过RX_EN信号使能。TLZ具有与发射器块相同的功能。HSMODE信号启用高速模式。

RX_EN信号从VDD1到VDD2进行电平转换,以使能接收Y_IN信号的缓冲器。然后,电平转换器将缓冲的Y_IN信号移至VDD1电压轨。

使用故障过滤器I²C信号容易受到噪声和干扰。结果,您需要一个毛刺滤波器来滤除所有不需要的毛刺,并仅允许有效信号通过。在标准/快速模式下,<= 50ns的毛刺被抑制。在高速模式下,抑制毛刺<= 10ns。

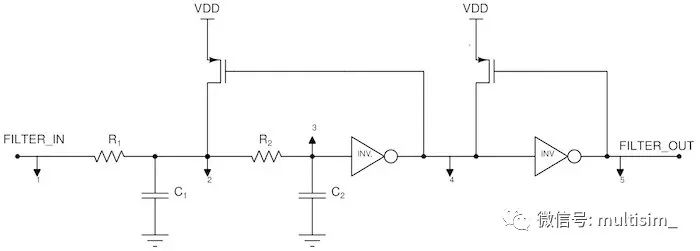

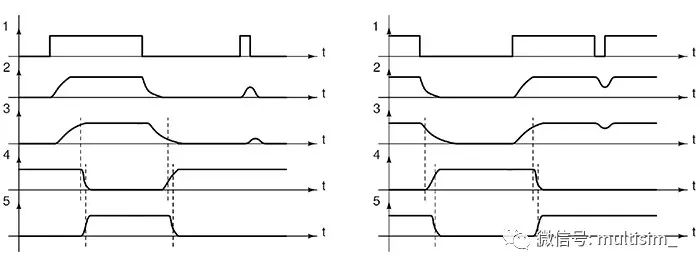

毛刺滤波器的设计如图4所示,时序图如图5所示。

图4.毛刺滤波器设计

图5.毛刺滤波器的时序图

RC时间常数会延迟通过信号并抑制任何毛刺。R1,C1,R2,C2的组合确定要抑制的毛刺的脉冲宽度。根据I²C规范,接收器应能够抑制标准和快速模式下<= 50ns的毛刺脉冲,以及在高速模式下<= 10ns的毛刺脉冲。

来自毛刺滤波器的输出信号被缓冲,并被IC处理以进行进一步的操作。

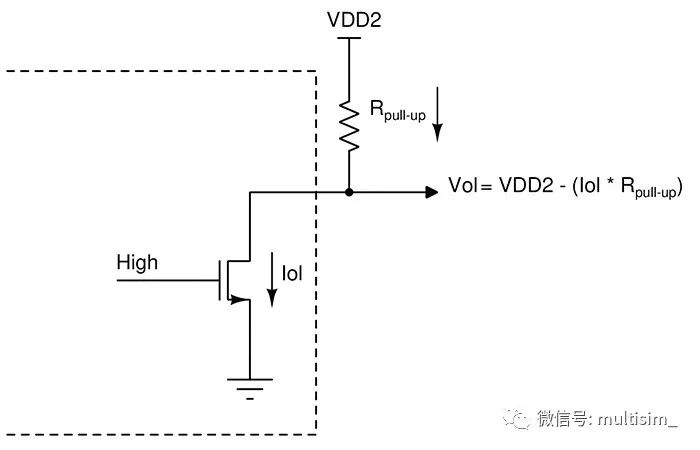

开漏配置的上拉电阻I²C线路上的输出缓冲器采用漏极开路配置,我们将在有关I²C总线所需硬件的文章中对此进行详细讨论。任何I²C器件只能在这些I²C线上驱动低电平或使其处于三态。为了获得逻辑高电平,需要在三态条件下将上拉电阻器将其拉至电压轨。

当器件驱动为低电平时,这些上拉电阻通过NMOS汲取电流,如图6所示。

图6.开漏配置

上升时间取决于上拉电阻和寄生电容的时间常数,通常比下降时间更长,因为下降是由器件(即由NMOS)驱动的。因此,对于不同的工作速度,需要使用不同的上拉电阻。

责任编辑:xj

原文标题:设计集成威廉希尔官方网站

I2C模块的I / O驱动器

文章出处:【微信公众号:multisim】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 集成威廉希尔官方网站

- I2C

-

程序中USB的DP和DM IO配置为50Mhz,需要打开I/O补偿单元来减少噪音吗?2024-04-26 0

-

设计集成威廉希尔官方网站 I2C模块的I / O驱动器2020-09-21 0

-

在I/O威廉希尔官方网站 中ESD保护结构的设计要求2021-04-02 0

-

I/O继电器内部结构原理图2010-03-02 1884

-

MCU---I/O基本结构2021-10-28 374

-

集成在PCB板上的EtherCAT远程I/O模块2022-10-19 1669

-

I/O单元的结构说明 简单介绍几种数字I/O单元2023-01-19 14804

-

在低成本MSP430 MCU中集成I2C I/O扩展器2024-09-24 127

全部0条评论

快来发表一下你的评论吧 !