单个LFPAK器件在不同配置的pcb上的热性能的因素

描述

单个LFPAK器件

本节将检查影响单个LFPAK器件在不同配置的pcb上的热性能的因素。从这一点开 始,当讨论叠层或结构从器件中去除热量的能力时,使用短语“热性能”。为了全面了解影响热性能的因素,我们将从最简单的一层叠层的PCB开始,然后系统地向PCB中添加更多的层。

实验设计1:单层PCB

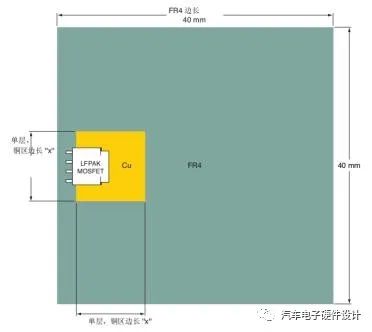

最简单的PCB叠层是单层铜;一个一层层叠。在实验设计1中,我们将检验器件结温(Tj)随顶层铜面积的变化。参见图1。

图1所示。单个的器件;一层层叠

图1展示了MOSFET器件,该器件安装在边长为“x”的第一层铜的正方形区域上,

FR4的尺寸为40mmx40mm。与此布局相对应的三种可能的威廉希尔官方网站 配置如图2所示。

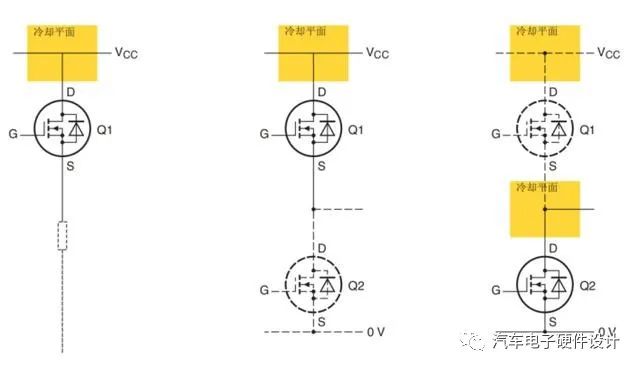

a.高边负载开关设置:MOSFET

b.半桥设置:MOSFET,Q1和Q2

c.半桥设置:MOSFET,Q2和Q1

图2所示。图1布局的三种可能的威廉希尔官方网站 配置。

图2(a)显示了MOSFET Q1配置为高边负载开关,其漏极片连接到VCC平面(黄色)。图2(b)和图2(c)展示了MOSFETs Q1和Q2连接在半桥结构中。这两种器件都是主要的通过连接到漏极的冷却平面,尽管对于Q2来说,这个平面相当于半桥的中点,而不是电源平面。通过将平面附加到MOSFET源极上,还可以实现少量的额外冷却,尽管源极引脚并不是从封装中获得的主要热路径,因此额外的好处是最小的。

一般来说,主要的热路径是通过封装漏极片,进入任何连接到这个连接的平面,这是本指南中要考虑的配置。

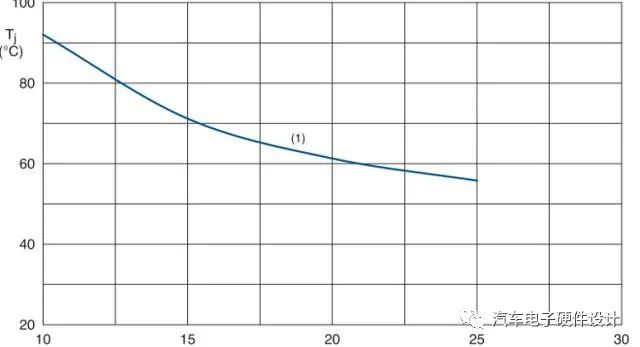

通过对不同尺寸的“x”进行实验设计,我们可以确定器件结温度(Tj)随铜面积的变化情况。结果如图3所示。记住环境温度是20℃。

图3所示。器件结温度与第一层顶铜面边长“x”

图3的图形有两个显著的特征:

•Tj在很大程度上取决于边长“x”,即第1层铜的面积

•顶层铜为MOSFET提供加热的能力显示了“边际递减规律”。换句话说,我们不能为了继续减少Tj而在第一层增加更多的铜面积。相反,从曲线的形状我们可以得出这样的结论:无论在第1层提供的多少铜面积,Tj永远不会低于50℃。

第4.1.1节指出,实际上有两个限制温度不能超过:MOSFET的Tj和PCB材料的TPCB的温度。对于表面安装的MOSFETs,最大TPCB点通常出现在MOSFET漏极片上,正如人们可能期望的那样。对于LFPAK封装中的MOSFETs,TPCB通常会比Tj小0.5℃,因此我们可以合理地说TPCB≈Tj。这将对LFPAK封装的其余实验设计作出假设。

如果环境温度保持在45℃以下,即使是第1层铜面积的较小区域也不会出现PCB降解的问题。

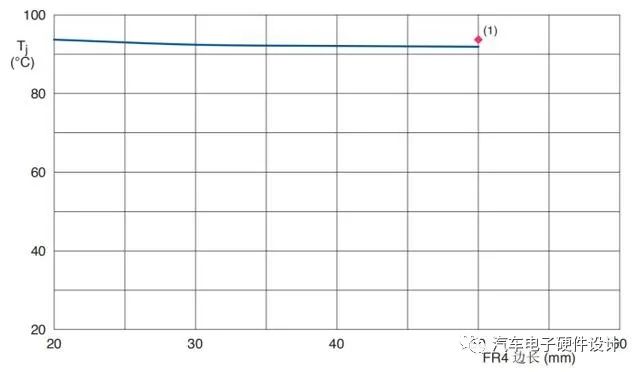

FR4尺寸对实验设计的影响

第4.3.1节中FR4 PCB面积的选择可能看起来既随意又不能代表实际应用中的PCB尺寸。然而,在这一节中,我们将看到光秃的FR4面积对器件(Tj)几乎没有影响。为了证明这一原理,我们对20mmx20mm、30mmx30mm、50mmx50mm的FR4尺寸进行了额外的实验设计,第1层铜面积固定在10mmx10mm。结果如图4所示。

图4:结温与FR4边长

图4的结果表明裸FR4的尺寸对器件Tj几乎没有影响。这与图3的结果形成了鲜明的对比,在图3中我们改变了第1层铜面积。当我们比较时,两组结果之间的差异很容易理解铜和FR4的热导率;铜的导热系数约为380w /(m.K),而FR4的导热系数仅为0.6W/(m.K)。由于热导率是一种衡量热量如何轻易地通过一种物质的指标,因此很明显,即使是增加大面积的FR4(这是一种糟糕的热导体)也远不如增加更小面积的高导热铜有效。我们可以通过在模型中添加1层铜的不连通区域来进一步说明FR4的绝缘特性,如图5所示。

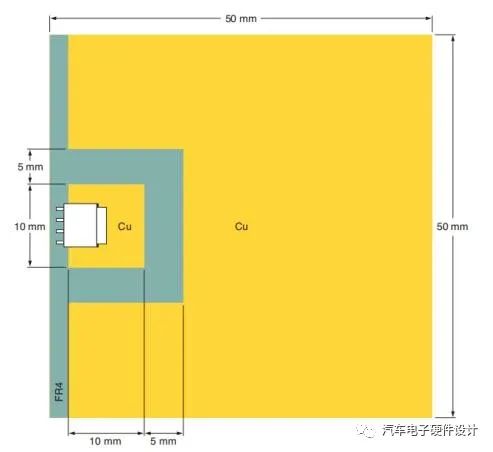

图5:在50mm×50mm FR4板上增加一层铜

图5显示了50mm×50mm的FR4布局,其中1层大部分区域都充满了大量的铜。在器件周围留下了5mm的间隙,其封装为10mmx10mm的铜面积。虽然我们可能已经预料到额外的第1层铜会对器件Tj造成重大影响,但事实并非如此。由于设备周围的隔离间隙和中间FR4的导热性差,热能无法利用额外的“散热”区域。FR4以这种方式“隔离”热源的能力很重要,将在第4.4节“两个LFPAK器件”和第4.5节“四个LFPAK器件”中再次实验设计。

责任编辑人:CC

-

PCB热设计概述2023-04-20 0

-

PCB提高中高功耗应用的散热性能2018-09-12 0

-

影响PCB板上孔焊接性能的因素2020-01-06 0

-

影响单个LFPAK器件在不同配置的pcb上的热性能的因素2023-04-20 0

-

PCB外壳对PCB热设计的影响因素2023-04-20 0

-

研究不同的模式对PCB设计热性能的影响2023-04-20 0

-

PCB板上两个LFPAK器件的热性能介绍2023-04-21 0

-

不同的PCB和器件配置对热行为的影响2023-04-21 0

-

an-2026PCB设计简单开关电源模块的热性能的影响2017-06-22 1052

-

orcad中单个器件的PCB封装如何处理2021-10-11 12412

-

LFPAK88:一个非常酷的客户2023-02-10 1340

-

影响pcb蚀刻性能的五大因素有哪些?2024-03-28 957

-

基于热性能的NIS(V)3071 PCB设计考虑因素2024-07-23 1332

-

TPS62366热性能和器件使用寿命信息2024-08-26 108

-

LM501x热性能和示例PCB设计2024-09-07 108

全部0条评论

快来发表一下你的评论吧 !