基于总线接口芯片SN74LVTH245A实现长距离数据传输系统的设计

描述

在某型雷达系统中,雷达发射机控制器实时监控发射机各设备状态并采集关键数据,发送给雷达中心控制计算机,并根据接收到的控制字完成对发射机点频、调制方式等功能和状态的控制。这就要求在发射机控制器与雷达中心机之间建立高速、可靠的连接。实践中,两机间的多节点数据传输距离不小于50m,并且发射机控制器是由PC/104构建的硬件平台,工作电压为+5V;而中心控制计算机是基于ADSP21060构建的硬件平台,工作电压为+3.3V。在这种前提下,两机现有的并口、串口、USB2.0等接口显然不能满足要求,其他诸如以太网的实时性难以满足要求,光纤通信通道因多节点的因素构建成本过高。基于此,本文提出了一种基于双口RAM、总线接口芯片和差分信号传输的并行总线通信解决方案。

数据传输系统方案

由于系统要求的传输距离长,需采用差分平衡传输技术;对于+5V与+3.3V的总线接口,采用美国TI公司总线接口芯片SN74LVTH245A完成混合电压总线I/O,其中,总线接口芯片的电源电压为+3.3V;由于差分驱动与接收芯片的传输方向是单向的,而系统要求双向数据传输,对16位数据总线的高8位和低8位分别进行单向驱动与接收;利用本方案所采用的双口RAM,IDT70V24可分别进行高8位和低8位读写功能,完成双向数据传输。整个数据传输系统框图如图1所示。

数据传输系统设计

系统工作原理可表述如下:由于DSP板工作电压为+3.3V,PC/104板工作电压为+5V,考虑到长线传输的压降,将双机共享的双口RAM放在一块专用的接口板上,该接口板与DSP板设计为板间通信,通信距离不超过50cm,故DSP板即中心控制计算机仅需要普通的总线驱动与隔离就可以完成对双口RAM的读写访问,数据通信速率可达128Mbit/s。

利用IDT70V24高8位数据与低8位数据可分别进行读、写控制的功能特点,将PC/104板即发射机控制器的16位数据总线设计为低8位读、高8位写,这样,PC/104板访问双口RAM的所有信号除低8位数据线为差分接收外,其它所有如高8位数据线、地址线、读、写、片选均为差分输出,所有差分信号经双绞线传输到接口板上后,对应进行差分接收与驱动,将信号还原成+5V信号,所有信号经总线接口芯片SN74LVTH245A完成混合电压总线I/O, 然后直接与双口RAM连接,完成对双口RAM的访问,数据通信速率为64 Mbit/s。

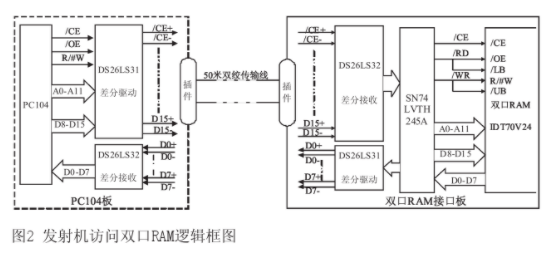

在本设计中,对于双口RAM的令牌仲裁/SEM、硬件仲裁/BUSY和中断仲裁/INT,充分利用双口RAM高、低8位读写功能,中心控制计算机写双口RAM低8位,读高8位,发射机控制器写双口RAM高8位,读低8位,有效避免了双机访问双口RAM的读写冲突,使得接口逻辑更为简单、成本更低。发射机控制器访问双口RAM的逻辑框图如图2所示。

解决的关键问题

设计使用差分平衡传输技术,解决了并行通信信号的多节点、长距离传输问题。工程实践中,通信距离为50m,节点6个,在实际设计中,应注意以下几个方面的问题。

首先,理论和实践均证明差分信号对使用双绞线进行传输性能最佳,使用屏蔽双绞线可大大提高传输系统抗电磁干扰的能力。

其次,差分信号的印制板布线是整个设计的难点,实际布线应尽量遵循下列原则:差分信号对应尽量短、走直线,切记差分对内的线间距保持一致;差分信号对一定保持同层布线;两组差分信号对之间的间距最好能达到差分对间距的10倍,条件限制的情况下,在差分对与差分对之间放置接地过孔可有效减少线间串扰。

最后,差分传输需要在接收端进行阻抗匹配,匹配阻抗值等于差分阻抗,其典型值为100Ω,但在设计实践中,匹配电阻应设计为容易调整的形式,具体的阻抗值应根据传输路径的长短和具体的电磁干扰环境进行配置。

基于以上所述,充分利用本设计使用的双口RAM功能特点,A机读低8位,则B机写低8位,A机写高8位,则B机读高8位,不仅使双工的并行通信得到实现,而且从根本上解决了双机共享双口RAM的读、写冲突问题和两侧CPU在工作不稳定时的误操作等问题。从而使得本方案的交叉事务处理设计变得相当简单,令牌仲裁/SEM、硬件仲裁/BUSY和中断仲裁/INT仅需要悬空或上拉即可,减少了设计成本。

总线接口芯片SN74LVTH245A是TI公司专为+5V与+3.3V混合电压系统设计的总线接口芯片,该芯片采用+3.3V供电电源,可驱动TTL威廉希尔官方网站 且不需要任何外围接口威廉希尔官方网站 ,使得混合电压接口威廉希尔官方网站 设计变得简单。

结语

本文实现的长距离数据传输系统,已成功应用于某型相控阵雷达中心控制计算机与发射机控制器之间的双工并行通信,通信距离大于50m,数据通信速率最高可达128 Mbit/s。该传输系统工作稳定、数据通信可靠,设计成本低,为大型电子系统设备间通信提供了一种性价比较高的解决方案。

责任编辑:gt

-

SN74lvth245a有何功能作用?2024-12-25 0

-

请问使用SN74lvth245a目的是什么?有什么功能作用?2019-05-10 0

-

以太网接口的设计及其数据传输的实现过程介绍2019-06-05 0

-

怎样去设计RS-485远距离通信接口和数据传输接口?2021-06-03 0

-

PCI总线高速数据传输系统设计2009-09-21 811

-

SOPC实现的PCI总线高速数据传输系统2012-02-10 1478

-

SN74LVTH245A-EP 具有三态输出的军用增强型塑料 3.3V ABT 八路总线收发器2018-11-02 204

-

SN74LVTH245A 具有三态输出的 3.3V ABT 八路总线收发器2018-10-12 645

-

基于双口RAM和SN74LVTH245A芯片实现长距离数据传输系统的设计2021-03-19 3946

-

万兆单模光模块SFP-XG-LX:高速长距离数据传输利器2023-12-04 1114

-

3.3伏ABT八进制总线收发器SN54LVTH245A SN74LVTH245A 数据表2024-03-01 323

-

3.3伏ABT八进制总线收发器SN74LVTH245A-EP 数据表2024-03-01 178

-

具有3态输出的3.3伏ABT八路总线收发器SN54LVTH245A SN74LVTH245A数据表2024-05-14 105

-

带18位通用总线收发器的3.3伏ABT扫描测试装置SN54LVTH18502A SN54LVTH182502A SN74LVTH18502A SN74LVTH182502A 数据表2024-05-14 119

-

具有三态输出的八进制总线收发器SN54ALS245A SN54AS245 SN74ALS245A SN74AS245数据表2024-05-14 138

全部0条评论

快来发表一下你的评论吧 !