如何将ARM的 Cortex™-M 处理器用于多核微控制器设计

电子说

1.3w人已加入

描述

本文将介绍设计、挑战以及与 Cortex-M 处理器和 CoreSight SoC 的使用相关的内容。

多核设计即将进入 MCU

一些应用程序可以从多核设计中受益

- 更高的性能/吞吐量

- 将实时和非实时任务结合在一起。

- 实时数据引擎+通信协议/GUI(例如NXP LPC4300)

- 实时控制任务 + 应用处理器(例如 Freescale Vybrid)

- 应用处理器 + 子系统 (OMAP)

- 出于可靠性原因——将关键核心操作与具有“更高风险”的任务隔离开来。这也可以促进认证。

多处理器系统挑战

记忆系统

- AMBA® 旨在支持多个总线主控,但是……

- 内存带宽和总线带宽有限

低功耗

- Cortex-M 处理器旨在支持各种睡眠模式

- 未使用的处理器可以进入睡眠模式甚至断电

- 总线系统和共享组件的时钟门控是可能的

- 需要考虑来自调试器的访问

调试

- CoreSight 调试架构允许共享调试和跟踪连接

- 各种走线总线宽度、时钟域

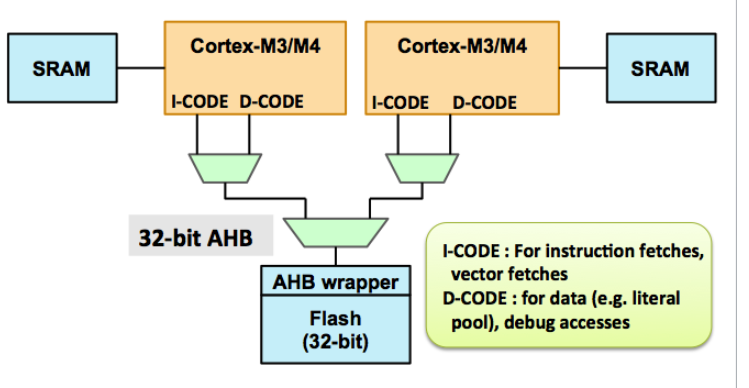

内存 – 程序 ROM / 闪存

- 当前的 Cortex-M 系列处理器没有缓存*

- 频繁的指令提取

- 相对于 CPU 时钟速度,闪存通常较慢

- 总线是32位的,很多指令都是16位的

- Cortex-M3 和 Cortex-M4 有一个指令缓冲区(3 字)

- 可以添加系统级缓存

- 额外的内存系统设计技巧

闪存访问加速器

- 64 位或 128 位闪存

- 预取单元

- 分支目标缓存

- 例如 STM32 F2/F4 有

- 艺术加速器

简单双核设计中的 ROM 共享

简单的程序 ROM 共享

获得 78% 的理想性能(Dhrystone 2.1,在 Verilog 模拟中)

修改仲裁

从任一核心获取文字,性能略有提高 78.9%

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADuCM320:精密模拟微控制器,14位模拟I/O, 带MDIO接口、ARM Cortex-M3处理器2021-03-21 969

-

【图书分享】STM32系列ARM Cortex-M3微控制器原理与实践2014-03-13 0

-

怎么区分ARM Cortex系列的处理器2018-09-13 0

-

什么是用于数字信号控制的CORTEX-M4处理器?2019-09-25 0

-

基于ARM® Cortex®‑M处理器概览2021-08-02 0

-

介绍易于使用的Arm Cortex-M处理器上的信号处理功能2022-07-29 0

-

LPC43xx/LCP43Sxx ARM Cortex-M4/M0多核微控制器资料分享2022-12-07 0

-

ARM Cortex-M处理器对比表2023-08-29 0

-

ARM Cortex-M 系列微控制器(ST)2009-11-02 952

-

东芝首款ARM Cortex-M0微控制器 专为智能电表而设计2012-06-01 1433

-

Stellaris微控制器用作IO处理器2016-01-12 623

-

ARM_Cortex-M0+微控制器原理与应用2016-01-15 654

-

《振南电子STM32视频教程》第一讲:ARM处理器和STM32微控制器2016-10-09 2237

-

STM32系列ARM Cortex-M3处理器微控制器原理与实践2017-09-22 1169

-

如何将Arm Cortex-M处理器与Xilinx的FPGA和SoC结合使用2023-09-15 259

全部0条评论

快来发表一下你的评论吧 !