FLY-BY拓扑结构:阻抗不连续到了什么程度呢

描述

相比T拓扑,fly-by在传输较高速率信号时更占优势一些,当然fly-by也并不就是完美的,它自身也存在很多缺陷,例如使用fly-by,负载之间有延时差,导致信号不能同时到达接收端。为解决这个问题,DDR3引入了read and write leveling,但是fly-by由于分支结构的存在,通道本身就存在一些缺点。例如:通道阻抗不连续;容性突变对时序的影响等等。下面就来详细的分析一下。

分支处阻抗的不连续程度受stub长度影响

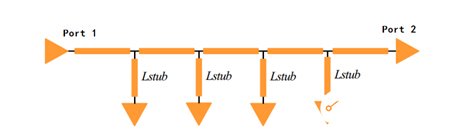

信号通道中只要有分叉就会存在阻抗的不连续,fly-by结构处处是分叉,阻抗不连续问题就很突出,到底这种阻抗不连续到了什么程度呢?下面就通过仿真实例来看看。在仿真软件中搭建如下拓扑结构,扫描通道S参数,再利用S参数反推出各个节点的阻抗。

图1

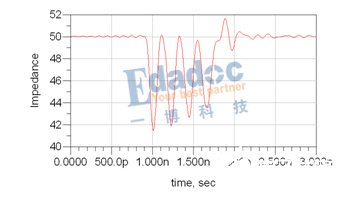

起初,我们将Stub长度都设定为100mil,扫描通道,得到通道的阻抗曲线如下

图2

由上图2可知,通道中有四次阻抗跌落,这些跌落分别对应该传输线的四个分支。Stub的长度与阻抗跌落的程度是否呈正相关呢?为简化分析过程,我们只允许通道中有一个Stub,扫描Stub长度,看看阻抗的变化趋势

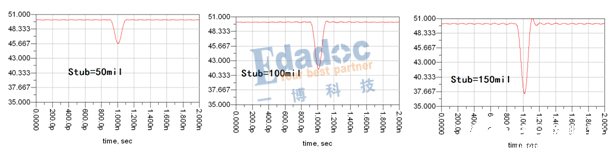

图3

仿真的结果如下图4所示。

图4

上图的结构是不是很容易让我们联想到过孔的Stub,没错,传输线上的Stub和过孔的Stub效应差不多,只不过我们在仿真过孔的时候,一般会选择三维建模,而且,过孔还考虑了焊盘的效应。

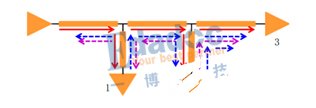

由图4的三个波形曲线可知,Stub越长,阻抗掉的越低。为什么会这样?传输线瞬态阻抗计算公式为Z=√(L/C)。就是信号感知的电感与电容的比值再开根号。因为分叉处的传输线与主线之间是并联关系,Stub就像并联在传输线上的小电容,Stub越长,电容量越大,阻抗也就越低。当然,fly-by结构的分支较多,每个分叉处都存在阻抗不连续,信号会在Stub之间来回反射,如图5所示,所以分析起来比较复杂。

图5

像这种复杂的反射,只能借助仿真软件去评估它对信号的影响程度。为了解决这个问题,工程上一般会选择在主通道末端接上上拉电阻。但是,末端端接只能解决末端反射问题,对于分支上的反射是不能完全消除的。

Stub电容效应对传输延时的影响

我们知道,连接在通道中途的短桩线和主通道是并联关系,而这些短桩线本身是有电容的,这就意味着这些小桩线相当于一个个的小电容并联在传输线中。由电容的频率响应曲线可知,电容对信号中的高频分量的阻抗是很低的,也就是说信号中的高频分量会因为通道中并联的小电容被过滤掉。高频分量的损失会导致信号的上升时间的变缓。到底是不是这样呢?

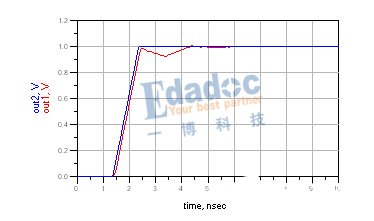

搭建如下拓扑,下图两个通道的长度是完全一致的。驱动端阻抗与传输线阻抗相匹配,在驱动端加载一个上升沿为1ns的激励。

图7

和我们推测的一样,连线中途的Stub会导致信号上升沿出现延迟的现象。因为: TD_0=Len√LC,信号在传输的过程中,每遇到一个Stub就会导致一个小小的延迟,多次累加后就会出现一个较大的延迟。这对高速信号来说,是不可忽略的影响。

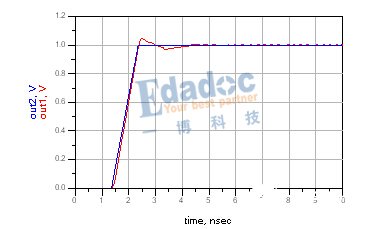

工程中会通过线宽补偿来减小这种容性突变,效果究竟怎么样呢,还是通过仿真来看一下。如上拓扑结构,调高Stub以及桩线之间走线的阻抗,看看上升沿的变化。

图8

由图8可知,Stub以及Stub之间的走线阻抗拉高之后,上升沿延迟现象得到改善。容性突变导致的负反射也得到一定的补偿。细心读者可能会发现,补偿之后,反射导致的过冲问题又显现出来,这可真是“按下葫芦浮起瓢”。怎么办?过冲问题只有交给端接电阻去解决了。

说了这么多,看来要想把fly-by结构对信号的影响说清楚还真是没那么容易。对于这种拓扑结构,常规的串扰控制自是不必多说的,另外,还需要牢牢记住的就是:Stub能短就尽量做短些吧;在负载很多的情况下,做一下阻抗补偿还是很有必要的。

编辑:hfy

-

(工程实践)DDR3 fly-by拓扑设计2015-11-16 0

-

FLY-BY拓扑,阻抗是怎么不连续的?2016-05-24 0

-

T型及Fly_by拓扑之应用总结2016-06-03 0

-

【分享】Altium 4层核心板(菊花链拓扑)案例2016-08-20 0

-

案例分享之DDR拓扑结构的选择2016-12-01 0

-

DDR3采用fly-by拓扑为什么有的采用RTT上拉端接,而有的采用RC下拉端接?2018-01-19 0

-

我的板子之前是按照fly-by拓扑(菊花链)布线,之后板子缩小打算用T行拓扑布线,有用过的大神知道可以直接更改吗?2018-05-28 0

-

请教一下DM8148的DDR控制器支持读写平衡吗,没找到描述,用fly-by拓扑,还是T型?2018-05-28 0

-

请问fly-by适用于多个芯片的情况效果一样吗?2019-09-16 0

-

如何解决PCB阻抗不连续问题2020-10-19 0

-

如何解决PCB设计中阻抗不连续问题2022-07-02 0

-

围绕拓扑结构与端接展开,浅谈对fly-by结构2021-04-11 6229

-

如何选择DDR的拓扑结构?怎样去改善信号质量呢?2021-04-08 3344

-

DDR PCB设计布线时,拓扑结构的选择2022-11-27 1516

-

PCB设计阻抗不连续的原因及解决方法2024-03-21 708

全部0条评论

快来发表一下你的评论吧 !