英特尔Core i5-L16G7处理器分析

电子说

描述

随着特征缩放到达物理极限,半导体行业开始研究后摩尔技术。在此领域,无论光刻技术节点,还是7纳米传统集成威廉希尔官方网站 、28纳米射频集成威廉希尔官方网站 ,多芯片封装对于在小形状因子中集成多种功能是至关重要的。所有这些都必须确保低成本并在短时间内上市。以此来看,Intel已经开发了几种互连技术以实现小芯片(chiplet)的异构集成。早在2018年,人们就在英特尔处理器上看到了这一技术的雏形,当时称为嵌入式多芯片互连桥(EMiB)。今天,英特尔展示了另一种在处理器中使用有源转接板和Foveros技术进行芯片互连的方案。

Foveros允许3D面对面(F-F)堆叠,通过使用硅通孔(TSV)在有源转接板上集成不同类型的器件。转接板作为不同小芯片之间的桥梁。它也包括低功率器件,如输入/输出(I/O)连接和高性能逻辑功率传输。

本报告分析的产品为英特尔Core i5-L16G7,特色是采用了英特尔的混合封装技术。该技术依赖于Foveros F-F芯片堆叠和PoP结构。该设计旨在将10nm运算芯片与SK Hynix LPDDR4 DRAM集成在一个PoP架构的封装体中。该方案降低了功耗并提高了核心性能,同时降低形状因子和Z高度,以适应超级移动应用。在该结构中,采用Foveros F-F技术和Via-Middle TSV工艺将10nm的运算芯片与22nm转接板直接互连,这样就可以方便地将功率传输到处理器芯片上。

关于Intel Foveros 3D Packaging Technology

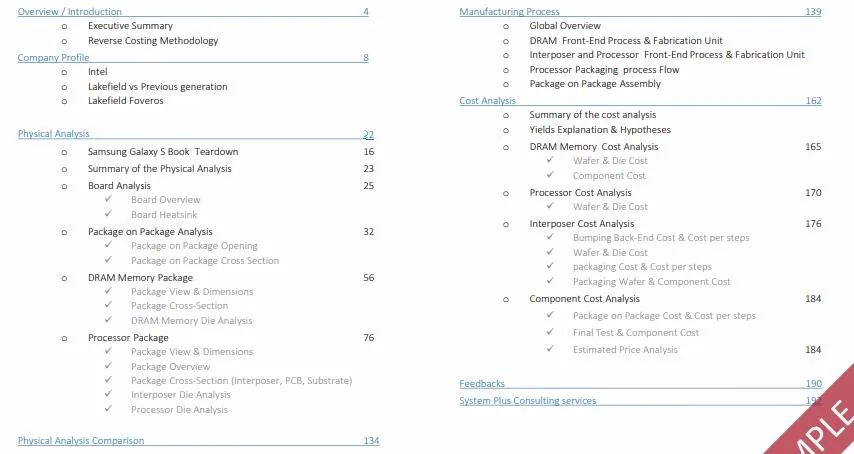

本报告对英特尔 Core i5-L16G7处理器进行了详尽分析,全面调研了英特尔混合封装技术,还分析了集成在封装体内的LPDDR4X DRAM芯片。最后,它包含了完整的成本分析和器件销售价格预估,并与台积电的CoWoS技术进行比较。

报告目录

相关报告

Fan-Out Packaging Processes Comparison 2020

Advanced System-in-Package Technology in Apple’s AirPods Pro

Advanced packaging technology in the Apple Watch Series 4’s System-in-Package

Status of the Advanced Packaging Industry 2020

Advanced Packaging Quarterly Market Monitor

(x)PU: High-End CPU and GPU for Datacenter Applications 2020

责任编辑人:CC

-

英特尔本月将推出32纳米6核Core i7-980X处理器2010-03-05 781

-

英特尔推笔记本架构的Core i5和i7微处理器2011-02-08 1322

-

支持嵌入式计算的基于英特尔酷睿I3 I3 I7处理器系列平台2011-12-07 1092

-

什么是酷睿i7处理器_i7处理器怎么样2012-09-14 30558

-

酷睿i5处理器详解_i5处理器怎么样2012-09-14 46848

-

英特尔酷睿i5和i7移动处理器细节曝光2012-11-26 2067

-

英特尔在CES发布酷睿i7处理器和VR体验技术2017-01-05 1697

-

英特尔酷睿i9处理器助力打造极致的游戏和内容创建体验2018-04-12 9757

-

国产CPU性能接近i3处理器,与英特尔i5看齐2018-08-28 5477

-

Sprint Vector采用英特尔酷睿i7处理器增强游戏的顺畅性2018-11-09 2241

-

全新i5-L16G7处理器曝光 搭载5核5线程2020-04-09 841

-

英特尔十代酷睿i7处理器也有TVB加速技术2020-04-14 6871

-

英特尔i5-11400处理器曝光:散热能力较弱2021-03-03 23532

-

英特尔推出先进的Intel Core i7处理器2021-03-25 5780

-

苹果M3芯片和英特尔酷睿i9处理器哪个强2024-03-08 7356

全部0条评论

快来发表一下你的评论吧 !