基于DSP芯片ADSP-TS101在雷达信号处理机中的应用及设计

处理器/DSP

描述

作为面向数字信号处理的可编程嵌入式处理器,DSP具有高速、灵活、可靠、可编程、低功耗、接口丰富、处理速度快、实时性好等特点。雷达信号处理系统所涉及的主要技术包括数据重采样、参数估计、自适应滤波、恒虚警处理、脉冲压缩、自适应波束形成和旁瓣对消等,通常需要完成大量具有高度重复性的实时计算。由于DSP可以利用硬件算术单元、片内存储器、哈佛总线结构、专用寻址单元、流水处理技术等特有的硬件结构,来高速完成FFT、FIR、复数乘加、相关、三角函数以及矩阵运算等数字信号处理。因此,DSP非常适合雷达数字信号处理算法的实现。本文详细地介绍了一种基于ADI公司高性能DSP—ADSP-TS101的雷达信号处理系统的具体实现方法。

1 系统部件及信号处理算法的实现

本系统是某雷达的信号处理机,总共有4块威廉希尔官方网站 板,分为母板、抗干扰板、脉冲压缩板和MTD板。

1.1 母板

母板主要是为其它三块单板提供电源,同时也可作为单板间信号传送的桥梁,将处理完的视频数据送到显示器显示。

1.2 抗干扰板

抗干扰板的主要功能包括中频采要、正交解调与低通滤波、自适应旁瓣对消及旁瓣消隐等。

(1) 中频采样

中频采样主要是通过ADC读人中频数据。本系统的ADC采用美国ADI公司生产的12位、40MSPS转换速率的高性能模数转换器,来将I、Q两路模拟信号以某一采样率转换为数字信号。

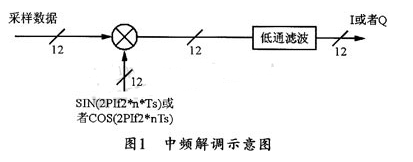

(2) 正交解调与低通滤波

该功能用于在FPGA中完成正交解调与低通滤波。在该系统中,FPGA选用的是ALTERA公司生产的EP1K100,,图1所示是该系统的中频解调示意图。由于系统会将采样信号均转换为1,0,-1,0,1……这样的数字序列,故在对采样信号进行解调后,会使其变为零中频信号,然后再对其做FIR低通滤波。

(3) 自适应旁瓣对消及旁瓣消隐

实现上述两算法总共要用到4片ADSP-TS101S。为了简化系统硬件、减少DSP的片间连线,系统的4个DSP之间应以松耦合的链路方式进行链接。可由DSP1将经过FlR低通滤波后的零中频信号以DMA方式读入。为了保证处理的数据为一帧完整的数据,本系统采用乒乓方式读人I、Q两路数据,这样可以保证一边读数据,一边处理,同时将定点数据转换为浮点数,并将处理结果送到DSP2。DSP2主要用于计算最佳旁瓣对消参数WI和WQ,并做旁瓣对消工作,再把处理结果送到DSP3。DSP3主要负责转发主副通路I、Q两路数据到DSP4,并计算主副通路I、Q两路数据模值的工作,同时负责将处理结果送到DSP4。DSP4主要完成旁瓣消隐运算并将处理结果发往脉冲压缩板。

1.3 脉冲压缩板

脉冲压缩板主要实现以下功能:

(1) 脉冲压缩

图2所示为脉冲压缩的实现原理图。脉冲压缩主要解决雷达作用距离与分辨率之间的矛盾,是雷达系统中较为成熟和经常采用的技术。假如总距离单元数为6000,则应将其补齐至8192点,然后做FFT。需要说明的是,这里用到的H(k)是在MATLAB中生成好的,然后存贮到DSP中以供其调用。在产生H(k)时,不光要采用加海明窗的方法,还应采用时域综合法进行旁瓣抑制。具体算法可参见相关资料。频域相乘后再做IFFT就是脉冲压缩的结果。该算法在DSP1中完成后,就可将处理后的数据送到DSP2做后续处理。

(2) 自适应滤波

自适应滤波采用自适应二次对消器来抑制云雨杂波,它由杂波测量和自适应二次对消器组成,主要在DSP2中完成自适应滤波参数Wi和Wq的估计运算,并做自适应滤波。然后把处理结果送到DSP3做后续处理。

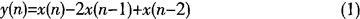

(3) 固定杂波对消

固定杂波对消采用二次对消器,其差分方程为:

在DSP3中做完固定杂波对消后,就可将结果送DSP4。

(4) 相参积累

可按矢量相加方式积累,积累帧数为16个;本设计采取滑窗方式保存本帧周期和前15个帧周期的视频数据:积累后除以16就可以取得平均值。DSP4在做完相参积累后就将处理过的数据送往MTD板做后续处理。

1.4 MTD板

MTD板实现的主要功能包括MTD处理、CFAR处理和非相参积累。

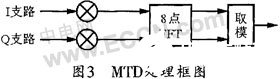

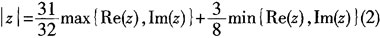

(1) MTD处理

MTD处理主要包括8点FFT程序和求模两部分。图3所示是其结构原理图,其中求模可采用如下近似公式:

该算法可在DSP1中完成,处理结果送入DSP2。

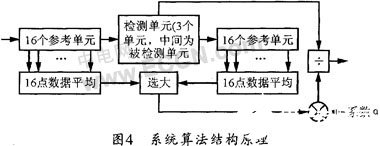

(2) CFAR处理

本系统中采用的算法框图如图4所示,CFAR处理的参考单元数N为35,前后各16个距离单元。

该算法在DSP2中完成后,将处理结果送到DSP3。

(3) 非相参积累

常用的非相参积累有单极点积累器、双极点积累器、滑窗积累平均积累等,本文采用简单的滑窗平均积累,其中Ns=8,Mr为总点数。那么:

该算法以及下面模块中的前半部分均在DSP3中实现。

(4) 输出模块

通过输出模块先完成浮点转定点,再乘以适当系数将数据范围压缩到10位,然后把大于零的振幅数据输出到D/A的视频数据,并用前帧同步作为中断,利用DSP的DMA0来将数据传至FPCA,再将FPGA锁存后的lO位视频信号输出到DAC。DAC选用具有10位有效数据位、125MSPS转换速率的高速器件AD9750,将数字信号转换为模拟信号后,可由OPA692F运算放大器驱动,并由视频电缆输出,以分别接到主机和显示设备。

2 系统设计注意事项

2.1 时钟

由于本系统是由多片ADSP-TS101组成的系统,所以由40 MHz晶振产生的时钟信号不能直接接到各DSP和FPGA,而应该通过驱动后再接到各DSP,且时钟信号到各DSP的距离应该尽可能接近。本系统中采用的时钟驱动芯片为IDT49FCT805。另外,在PCB布线时,应该将时钟信号尽量布在地层,并对其加以保护。

2.2 电源

ADSP-TS101有三个电源,其中数字3.3 V用于I/O供电;数字1.2 V用于DSP内核供电;模拟1.2 V为内部锁相环和倍频威廉希尔官方网站 供电。运行时要求数字3.3 V和数字1.2 V应同时上电。若无法严格同步,则应保证内核电源1.2 V先上电,I/O电源3.3 V后上电。本系统在数字3.3V输入端并联了一个大电容,而在数字1.2V输入端并联了一个小电容,其目的就是为了保证3.3V充电时间大于1.2V充电时间,以解决上述问题。系统用主机送来的5 V电压经过TPS54350得到3.3 V和1.2 V的电压。各片DSP的数字1.2 V电源各由一片TPS54350供给。6片DSP内部模拟1.2 V则由同一DSP芯片的VDD (1.2 V)经滤波网络后提供。FPGA的I/O电源为3.3 V,可由电源转换后直接使用,其2.5 V核电压应该单独由一片TPS54350来输出供电。

2.3 ADSP—TS101S的复位

TigerSHARC DSP的上电复位较为特殊,在设计时应充分引起重视。该DSP的上电复位波形要求如图5所示。这里应当注意的是,tstart_LO在供电稳定之后,还必须大于1 ms才能进行操作:而tpulsel_HI则必须大于50个系统时钟周期且小于100个系统时钟周期;tpulse2_LO必须大于100个系统时钟周期。

该DSP上电后正常复位时,低电平持续时间必须大于100个系统时钟周期。本系统采用Altera公司的FPGA EPlK100来产生上电复位波形和时序控制。由于EPlK100需要一个配置芯片,而且它和DSP存在一个上电先后的问题。也就是说,在上电后,如果FPGA芯片在进行配置文件的读入时,DSP上电仍未稳定,则应充分延长tstart_LO的低电平时间,以避免上电未稳定而FPGA上的波形已经结束。因此,应保证DSP上电稳定先于FPGA芯片配置文件的读入,此问题在系统设计时应予以充分重视,否则DSP将无法正常工作。

3 结束语

本文详细地介绍了雷达信号处理的各种算法在ADSP-TS101中的实现方法。该系统充分利用了ADSP-TS101S高速的运算能力及数据吞吐量。文中讨论了DSP应用过程中的时钟设计、电源设计和DSP复位问题,因而具有一定的工程指导意义。实践表明,由ADSP—TS101S构成的系统硬件结构简单,软件编写方便,而且成本较低。目前,该系统已成功应用于某雷达信号处理机中。

责任编辑:gt

-

一种基于TS101的SAR回波信号模拟器设计2019-07-22 0

-

如何利用FPGA与ADSP TS201设计总线接口?2019-08-09 0

-

如何采用ADSP-TS101实现高速信号处理系统的设计?2021-04-12 0

-

基于ADSP21161N的PD雷达数据处理机的设计2009-05-08 736

-

ADSP-TS101外部总线接口技术2009-08-11 875

-

毫米波跟踪雷达信号处理机设计2009-08-14 665

-

基于ADSP-TS101S的多芯片数字信号处理系统的实现方案2006-03-11 981

-

Adsp-TS101性能分析及其在雷达信号处理中的应用2010-09-23 1897

-

基于TS201的雷达信号处理机设计2011-07-20 954

-

基于VME总线TS101的通用多处理器模块设计2011-09-07 889

-

基于ADSP-TS101的高速数字威廉希尔官方网站 设计与仿真2012-09-06 2456

-

EE-157:解释ADSP-TS101上的分支目标缓冲区2021-04-15 939

-

EE-143:了解ADSP-TS101上的DMA2021-04-24 520

-

ADSP-TS101 TigerSHARC处理器编程参考2021-05-13 679

-

ADSP-TS101 TigerSHARC处理器硬件参考2021-05-22 577

全部0条评论

快来发表一下你的评论吧 !