关于四层板PCB设计阻抗匹配的要求和建议

描述

一块四层板PCB的层压和阻抗计算调整建议

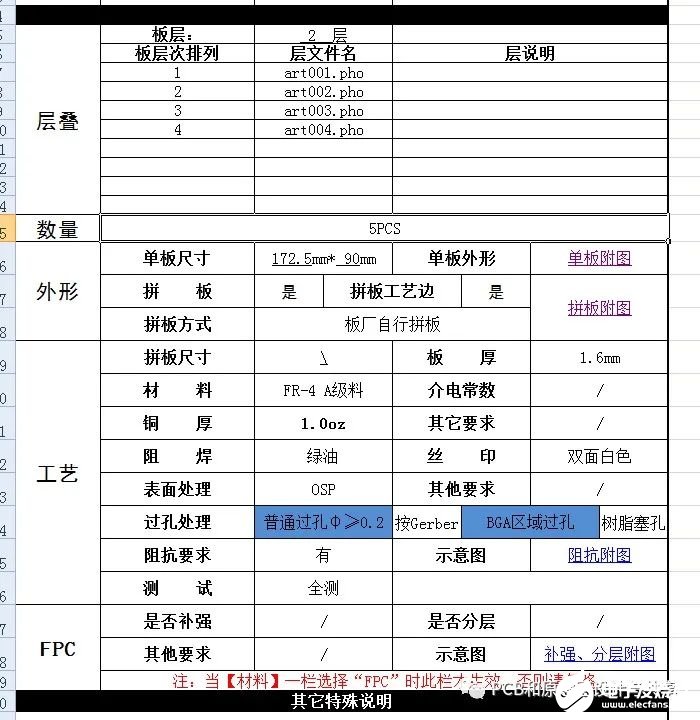

最近设计了一块四层板PCB,因为是高速威廉希尔官方网站 ,有阻抗匹配的要求,所以在发给pcb板厂打样时,特定指定了哪些线要做阻抗线。我自己给出的做板要求是这样的。

有阻抗匹配要求的线有单端的50欧姆射频线,有90欧姆的USB差分线,也有100欧姆的DDR差分线,如下图所示,

50欧姆射频线阻抗要求:

90欧姆usb差分线和100欧姆DDR差分线阻抗要求:

我自己简单计算了上述阻抗线的阻抗,半固化片用2116,参考平面的高度按4.5mil来算,介电系数用4.2,铜厚1zo。单端射频线线宽走6mil,间距10mil,算出单端走线的阻抗是50.47欧姆。

usb差分线线宽走了5mil,间距是5mil,线到地的间距是6mil,算出来的结果是88.96欧姆。

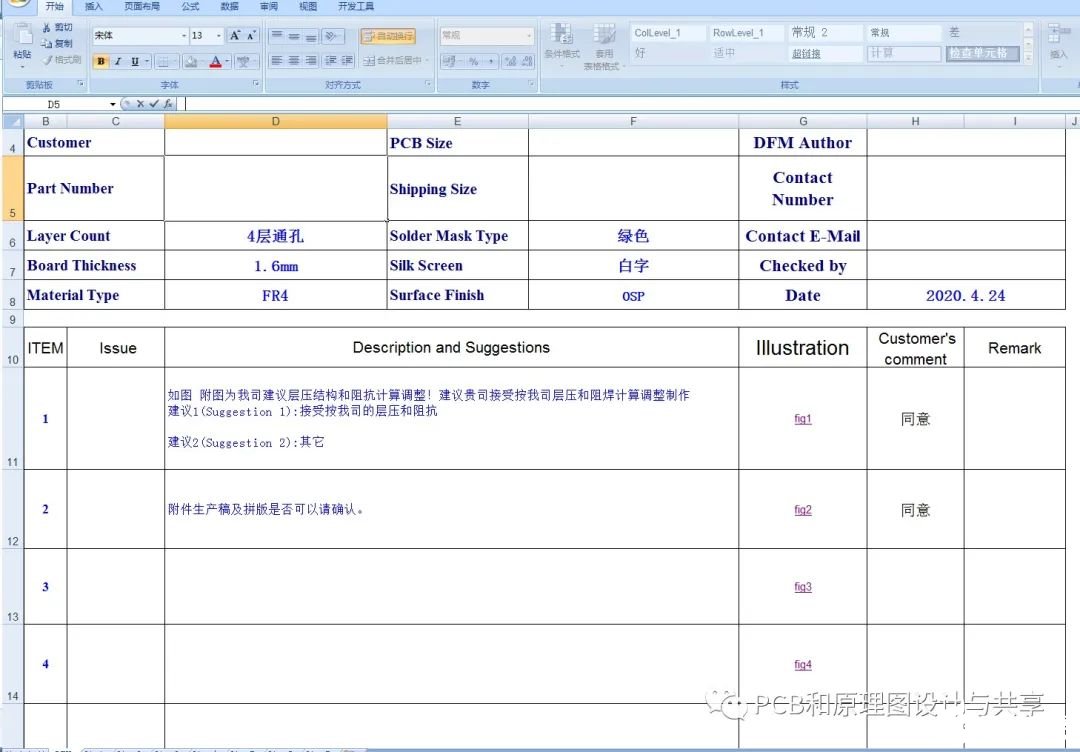

之后板厂评估后反馈回来的层压和阻抗计算调整建议是这样的,

从板厂反馈回来的信息可以知道,板厂用的板芯厚是1.3mm,半固化片用的是

3313PP,厚度是0.1mm,换算成mil应该是大概是4mil。

50欧姆单端射频线不需要调整,按照板厂的层压方式算出的阻抗是51.77欧姆,可以满足阻抗要求

90欧姆usb差分线需要由原稿的5mil线宽,5mil间距调整到5.5mil线宽,4.5mil间距,计算出来的阻抗是89.89欧姆,才能满足要求。

100欧姆的DDR差分线不需要调整,按照板厂的层压方式算出的阻抗是99.42欧姆,满足要求。

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- pcb

- 阻抗

- DDR

- 高速威廉希尔官方网站

-

如何解决PCB设计中的阻抗匹配问题2012-03-03 0

-

关于四层板阻抗匹配问题2012-06-04 0

-

高速PCB设计中的阻抗匹配2019-05-31 0

-

10层板PCB,内层信号层(5,6)阻抗匹配如何选择参考层?2022-04-24 0

-

高频高速PCB设计中的阻抗匹配,你了解多少?2023-05-26 0

-

PCB阻抗匹配计算工具(附教程)2012-11-02 11091

-

高速PCB中的阻抗匹配2017-08-28 1467

-

怎样理解阻抗匹配_pcb阻抗匹配如何计算2018-05-02 42762

-

PCB设计中的阻抗匹配的介绍特征阻抗及常见阻抗匹配的方式详细概述2018-07-12 1998

-

PCB阻抗匹配设计有什么技术要求?可以使用那些方法设计?2018-08-26 10012

-

技术 | 如何解决PCB设计中的阻抗匹配问题2019-06-21 6845

-

【硬见小百科】高速PCB设计中的阻抗匹配2019-12-13 2937

-

PCB设计阻抗匹配问题的解决办法2020-11-12 5179

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 2507

-

PCB阻抗匹配过孔的多个因素你知道哪些?2024-07-04 1344

全部0条评论

快来发表一下你的评论吧 !