AHB总线的应用框图/接口信号/基础传输

接口/总线/驱动

描述

AHB概述

AHB总线(AdvancedHigh-performanceBus)是AMBA(AdvancedMicrocontrollerBusArchitecture)片上总线体系的一部分。在SOC芯片中,AHB总线主要应用于对性能要求较高的组件之间互联,如用于CPU和片内高速RAM、DMA之间互联。

图1AHB协议演进

如图1所示,AHB协议在AMBA2中提出。随着AMBA协议族的演进加入了AHB_Lite,AHB5Lite。本文从AHB2入手对AHB协议进行介绍,再对比AHBLite,AHB5Lite同AHB2之间的差异。

AHB应用框图

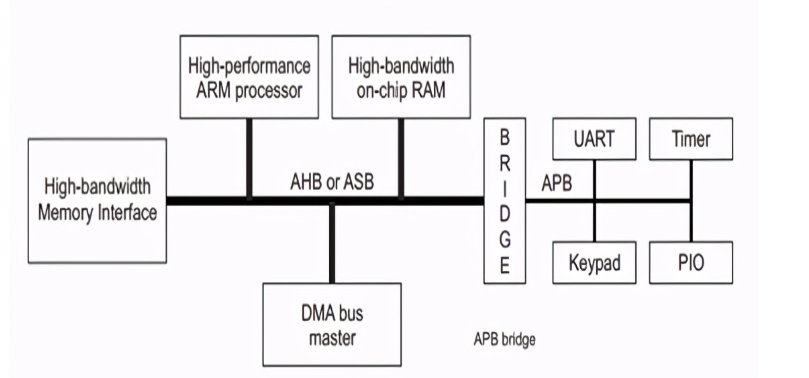

图2AHB总线应用框图

继续借用上篇介绍APB接口时使用的应用框图。如图2所示,AHB总线主要用于高性能ARM核,高带宽片上RAM,DMA,高带宽Memory接口,APB桥之间的互联。

AHB总线结构

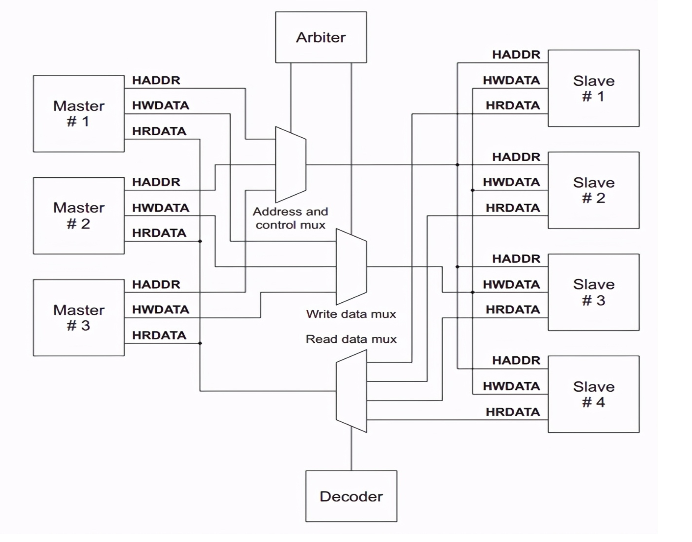

图3AHB总线结构

AHB总线由AHBMaster,AHBSlave,基础组件等3类组件组成。其中基础组件包含:Arbiter,Decoder。AHB总线为多Master总线和APB总线的单Master有着显著的不同。为了解决多总线访问外设问题引入Arbiter进行仲裁,Decoder则负责Slave之间的地址译码。

AHB总线接口信号

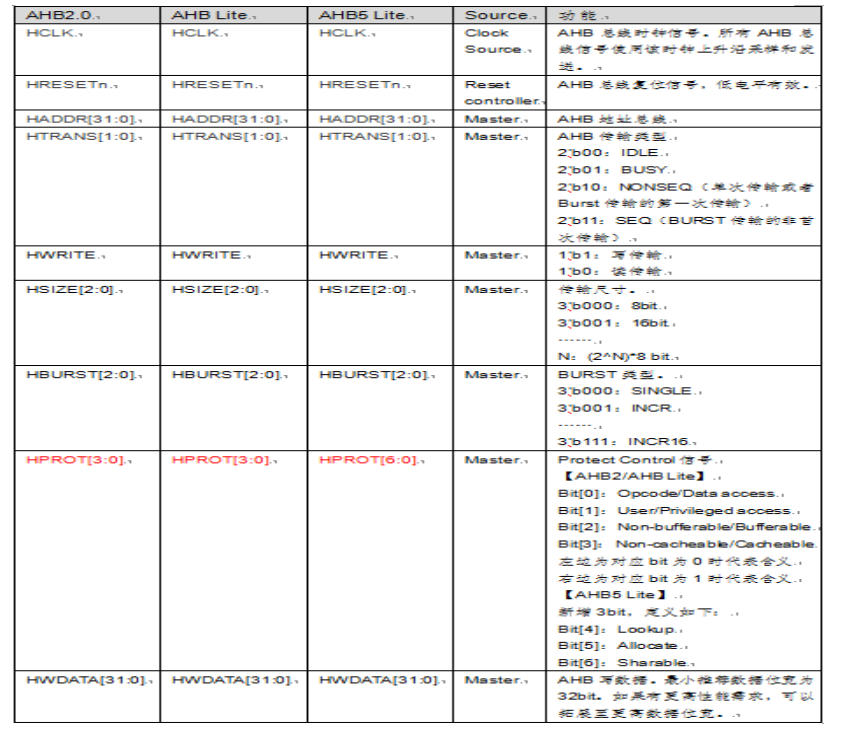

AHB总线信号如表1所示

表1AHB接口信号(1)

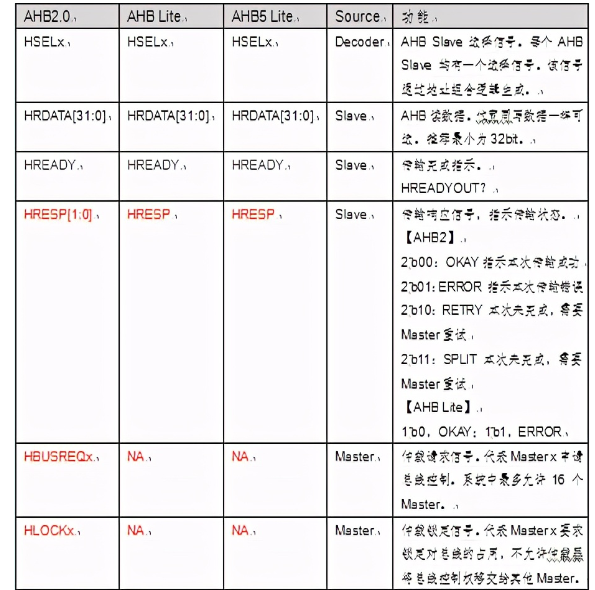

表1AHB接口信号(2)

表中红色字体的信号为AHB总线不同版本之间存在差异的地方。总结如下:

HPROT位宽不同:AHB5Lite为7bit,AHB2和AHBLite为4bit。

HRESP位宽不同:AHB2Response类型分为Okay,Error,Retry,Split四种类型,需要2bit指示。AHBLite/AHB5Lite则将其简化为Okay,Error两种类型。1bit位宽即可指示。

总线拓扑结构不同:AHB2通过Arbiter实现多Master的访问。而AHBLite、AHB5Lite则删除Arbiter仅定义了单Master访问的情形,总线结构如下图所示。

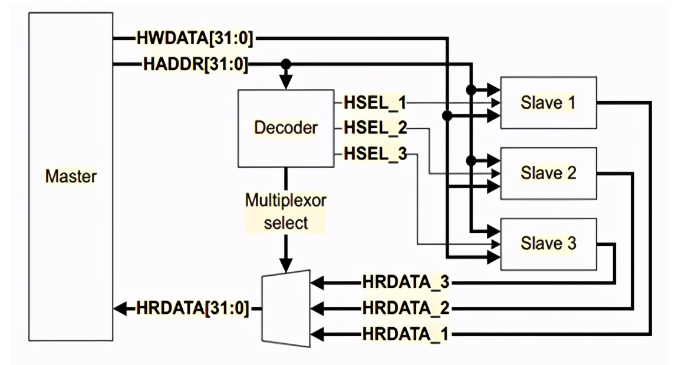

图3AHBLite总线结构

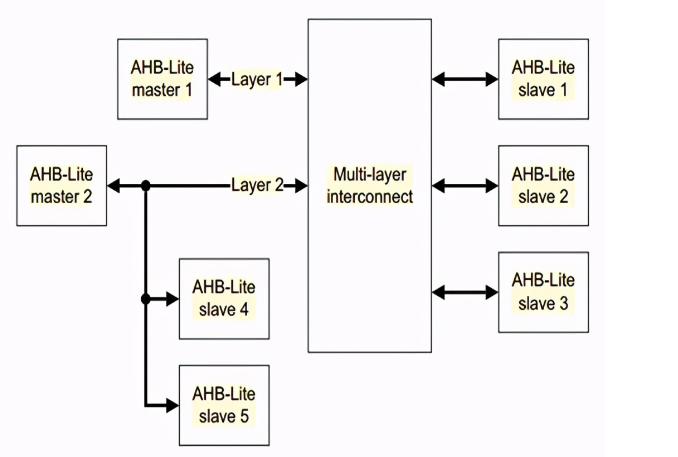

为了解决AHBLite、AHB5Lite多Master应用情形,在AMBA3中,引入Multilayer概念进行多Master扩展。扩展方式如下图所示:

图4AHBLiteMultiLayer总线结构

对MultiLayer感兴趣的同学,可以查阅文末参考资料中的第3个资料。

AHB基础传输

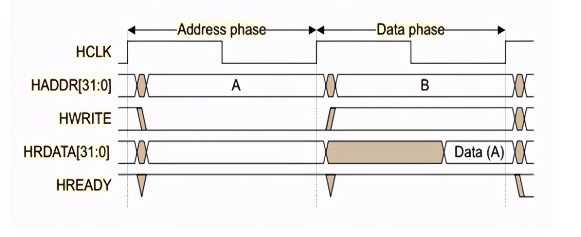

图5AHB基础读传输

AHB传输分为两个阶段:地址阶段,数据阶段。图5为典型的零等待读传输。地址阶段Master向SalveA发读访问,SlaveA在数据阶段返回Data(A)。注意图中细节,在SlaveA数据阶段时,Master同时还发起了SlaveB的写访问。这种Pipeline方式的访问行为就是AHB性能高于APB的原因。

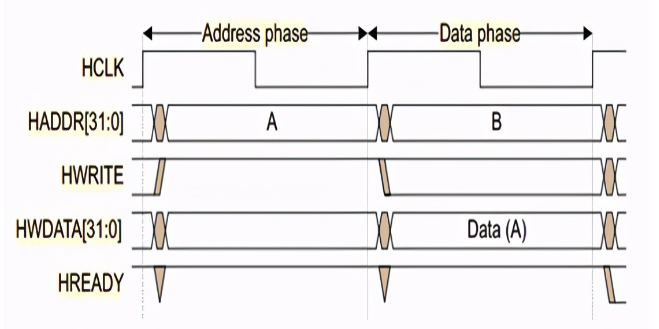

图6AHB基础写传输

图6为零等待写传输,在地址阶段向SlaveA发起写访问,在数据阶段发送写数据。

后记

AHB总线为了提升其性能,相对于APB总线引入了Pipeline的传输模式。这样AHB总线在同频率同数据位宽的情形下,理论性能是可以是APB性能的两倍。AHB总线协议相较APB总线协议复杂很多,本文仅做入门介绍,感兴趣的同学可以查阅本文结尾的参考资料进行深入了解。

责任编辑人:CC

-

USB2.0设备控制器IP核的AHB接口设计实现2019-05-13 0

-

AMBA AHB总线与APB总线资料合集2022-04-07 0

-

AHB总线中的HLOCK信号和HMASTLOCK信号之间有什么关系2022-06-08 0

-

AHB总线传输的时序图分析2022-06-09 0

-

AHB总线接口的一种新实现方案2010-11-11 921

-

CAN总线接口信号隔离收发IC2016-11-18 1223

-

AHB总线应用教程2017-11-15 21899

-

观察PCI Express HIP PIPE接口信号2018-06-22 3843

-

AHB Slave Decoder和AHB Slave Interface接口的使用说明2020-11-11 2180

-

APB总线的应用框图及接口信号2020-11-17 13363

-

HDMI模块接口概念及接口信号定义介绍2022-04-12 1312

-

龙迅HDMI接口信号转换的应用案例2022-06-14 3820

-

聊聊AMBA总线-AHB2023-05-04 1741

-

顺源科技新产品:内置隔离电源的CAN总线通讯接口信号隔离模块2022-02-25 302

-

12芯M16接口信号传输检测方法有哪些2024-05-23 280

全部0条评论

快来发表一下你的评论吧 !