资料下载

×

常用的差分逻辑电平详细介绍

消耗积分:0 |

格式:rar |

大小:0.93 MB |

2021-01-06

本篇主要介绍常用的差分逻辑电平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

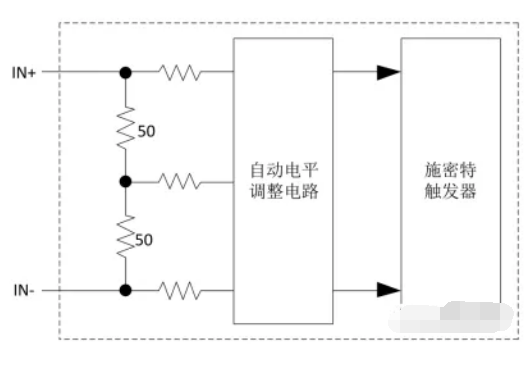

1、LVDS电平

LVDS器件是近年来National Semiconductor公司发展的一种高速传输芯片,它的传输机制是把TTL逻辑电平转换成低电压差分信号,以便于高速传输。与传统的ECL逻辑相比,它采用CMOS工艺,它的电压摆幅更低,只有400mV,ECL为800mV,动态功耗更小,(输出电流3~5mA)只有ECL威廉希尔官方网站 的1/7(相同的数据传输量),低EMI,价格更低,因而具有很大的优势,从97-98年首先在欧洲开始得到应用。

ANSI/TIA/EIA-644是由TR30.2制定的,这个标准定义了收发器的输入输出阻抗,但是这仅仅是一个电气特性标准。其并不包括功能性和协议规格,完全是应用独立的。

ANSI/TIA/EIA-644打算通过使用别的协议来完善整个接口功能。这使的这个标准在很多方面便于实现。在标准中推荐的最大操作速率是655Mbps,理论最大使用速率是1.923Gbps。传输速率与使用的介质损耗有关。这个标准同时也说明了最低的介质要求、接收端的fail-safe威廉希尔官方网站 、多路操作等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章