【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

描述

原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

vitis工程目录为“ps_dp/vitis”

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

软件工程师工作内容

以下为软件工程师负责内容。

1. 接口介绍

DisplayPort v1.2协议,支持4个5.4G的lane,但本控制器只支持两个lane,分辨率最大支持4096*2160@30。

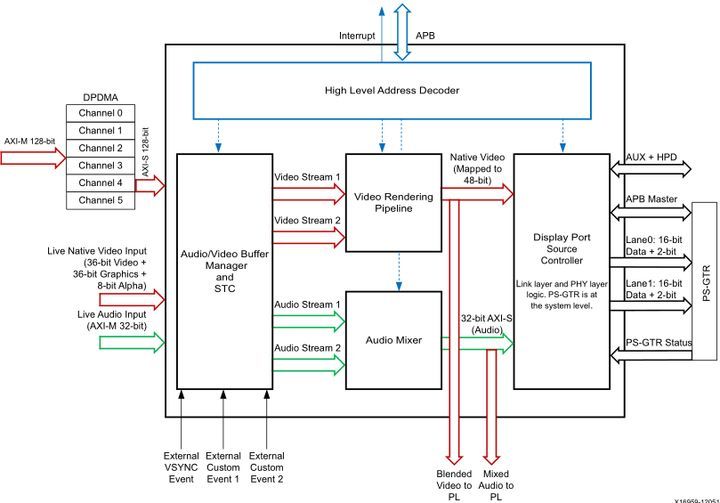

控制器数据接口如下图:

图中,AXI-M用于读取内存中的视频和音频数据,这里叫非实时音视频,DPDMA有六个通道,其中3路用于视频,1路用于图形,2路用于音频。

2. Example工程介绍

-

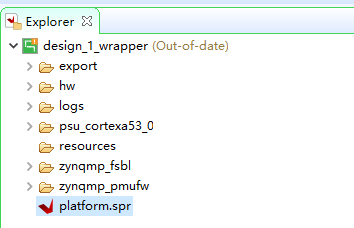

新建platform,过程不再介绍,在”PS端RTC中断实验”中已经介绍过。

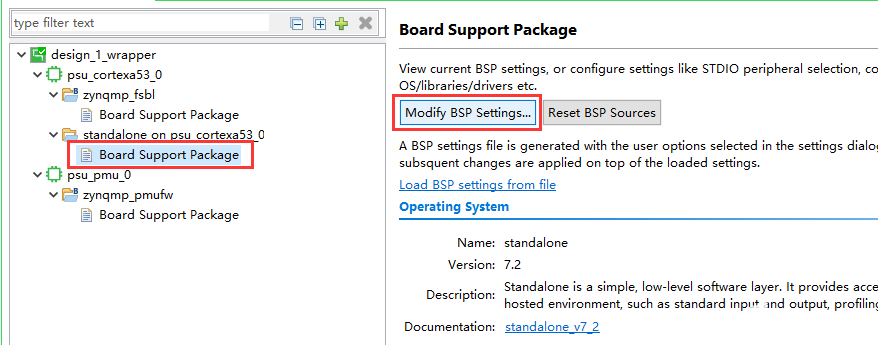

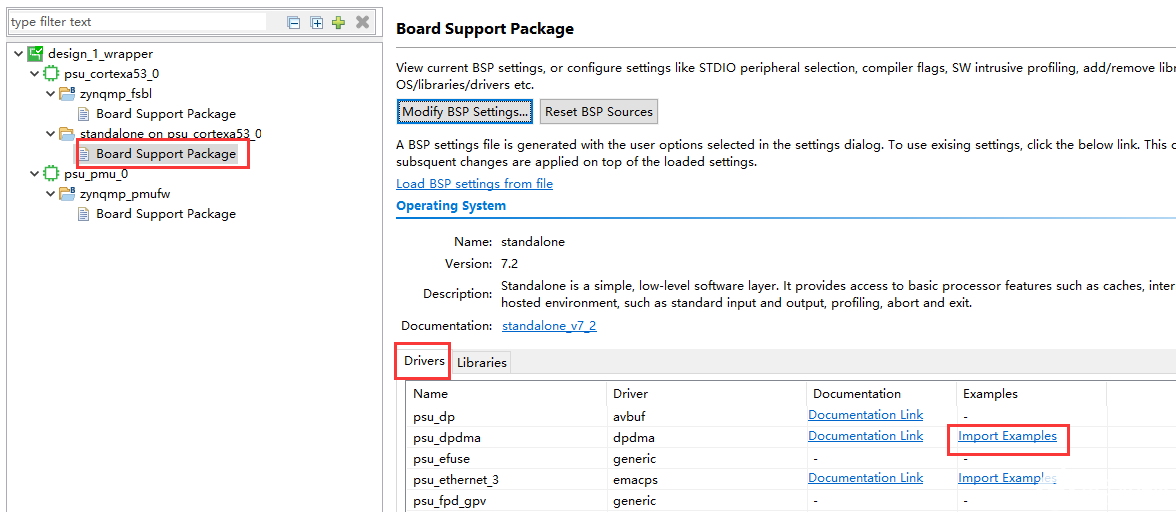

1)配置BSP

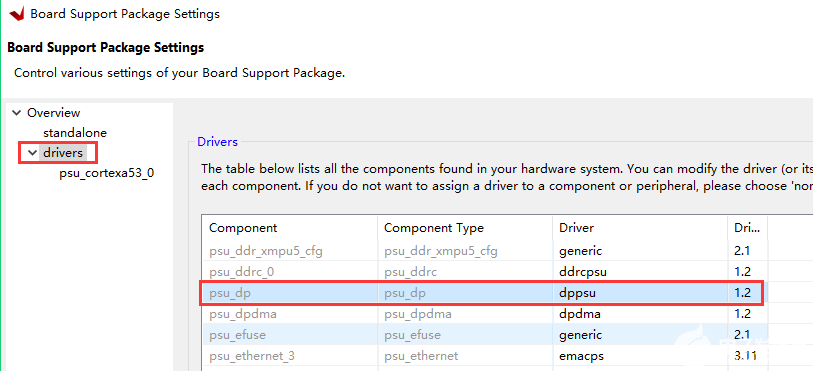

并将psu_dp驱动改为dppsu,然后点击OK

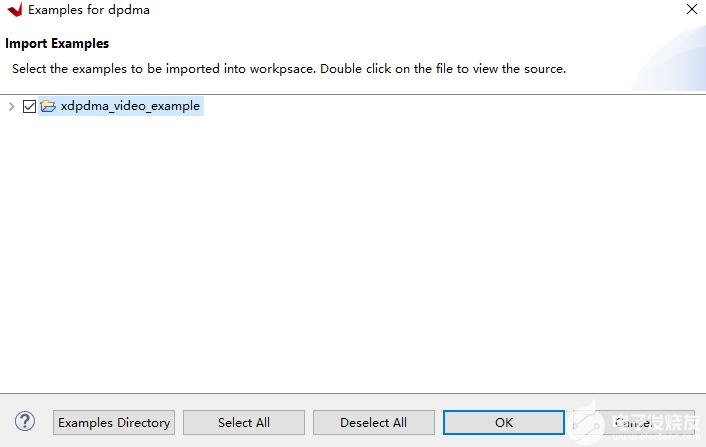

3)导入example工程

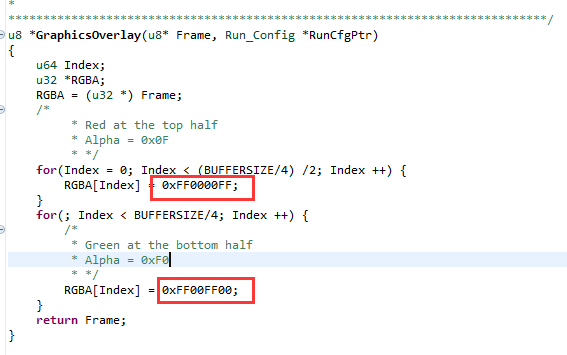

4) 例子默认是1080P,RGBA显示的,可以将RGBA的Alpha值都改成FF,使显示效果更好,保存,并编译工程。

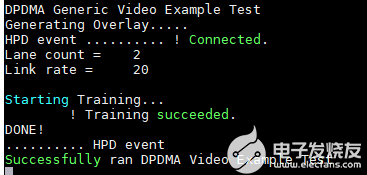

3. 板上验证

连接板上的MINI DP接口

下载后,显示效果如下

在串口工具中可以看到DP口进行了训练并成功运行。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

第二十三讲 异步计数器2009-03-30 12185

-

模拟威廉希尔官方网站 网络课件 第二十三节:乙类双电源互补对称功率放大威廉希尔官方网站2009-09-17 2052

-

闲话Zynq UltraScale+ MPSoC(连载1)2017-02-08 740

-

闲话Zynq UltraScale+ MPSoC(连载5)2017-02-08 730

-

2017中国西部微波射频技术研讨会暨第二十三届国际电子测试测量研讨会2017-07-05 1020

-

Zynq UltraScale+ MPSoC的发售消息2018-11-27 3600

-

米尔科技Zynq UltraScale+ MPSoC技术参考手册介绍2019-11-18 3203

-

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?2021-02-23 1344

-

【正点原子FPGA连载】第二十三章RGB-LCD字符和图片显示实验 -摘自【正点原子】新起点之FPGA开发指南_V2.12021-11-24 593

-

烽火通信光纤技术获“第二十三届中国专利奖”银奖2022-05-05 1289

-

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计2022-11-02 1591

-

Zynq UltraScale+ MPSoC的隔离设计示例2023-09-13 298

全部0条评论

快来发表一下你的评论吧 !