资料下载

×

CY7C1643KV18和CY7C1645KV18静态存储器的数据手册免费下载

消耗积分:1 |

格式:pdf |

大小:0.75 MB |

2021-02-22

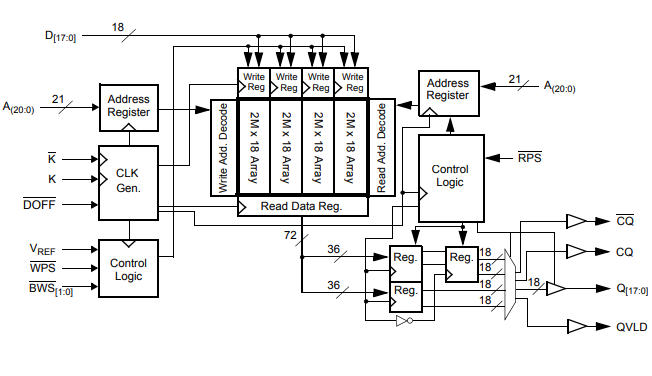

CY7C1643KV18和CY7C1645KV18是1.8V同步流水线SRAM,配备QDR II+架构。与QDR-II体系结构类似,QDR-II+体系结构由两个独立的端口组成:用于访问内存阵列的读端口和写端口。读端口有专用的数据输出以支持读操作,写端口有专用的数据输入以支持写操作。QDR II+体系结构具有独立的数据输入和数据输出,完全无需“周转”与常见I/O设备一起存在的数据总线。每个端口通过公共地址总线访问。读写地址的地址锁存在输入(K)时钟的交替上升沿上。对QDR II+读写端口的访问彼此完全独立。为了最大限度地提高数据吞吐量,读写端口都配备了DDR接口。每个地址位置都与四个18位字(CY7C1643KV18)或36位字(CY7C1645KV18)相关联,这些字依次进入或离开设备。由于数据在两个输入时钟(K和K)的每个上升沿上都被传输到设备中或从设备中传出,因此在通过消除总线“周转”简化系统设计的同时,最大限度地提高了内存带宽。通过端口选择来完成深度扩展,从而使每个端口能够独立运行。所有同步输入通过由K或K输入时钟控制的输入寄存器。所有数据输出都通过由K或K输入时钟控制的输出寄存器。写入是通过片上同步自定时写入威廉希尔官方网站 进行的。有关相关文档的完整列表,请单击此处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章