单片机存储扩展方法与程序控制案例

电子说

描述

单片机内部存储器和I/o口资源有限,多数情况下需要外部扩展。

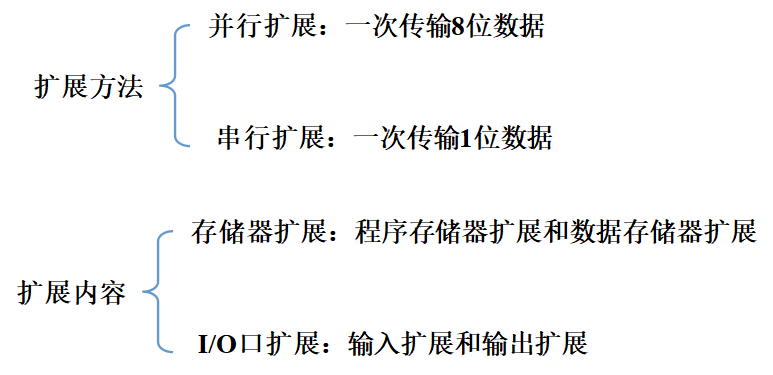

一、扩展方法和内容

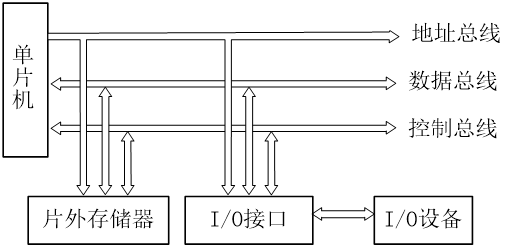

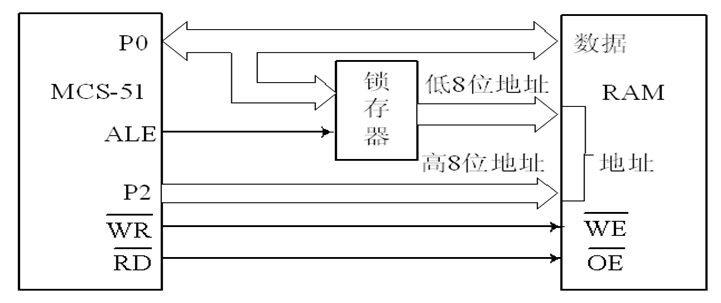

二、总线介绍单片机并行扩展的典型结构是总线结构。

各扩展部件通过总线与单片机连接起来,相当于系统中各部件挂在总线上,分时利用总线与CPU通讯。

当选中某部件时,可对该部件进行读写及控制,而其它部件与总线间处于“高阻态”,相当于与总线断开。

单片机系统的三总线构造方法如下:

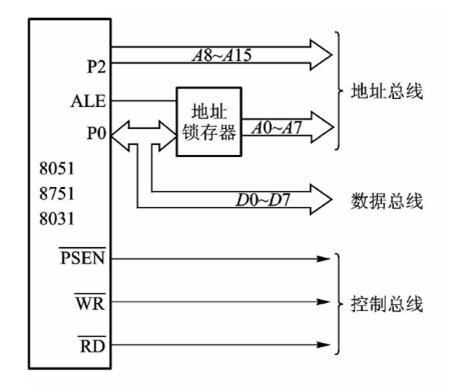

以P0口线作数据总线/低位地址总线4以P2口线作高位地址总线

采用功能引脚形成控制总线

以P0口线作数据总线/低位地址总线:先由P0口线作地址总线,把低8位地址送锁存器,由锁存器提供给系统;然后再将P0口线作数据总线读写数据,从而实现地址总线的低8位地址信号和数据总线共用P0口线而不产生冲突。

以P2口线作高位地址总线:P2口线最多可提供8位高位地址,加上P0口线提供的低8位地址,最多可提供16位地址,可使单片机系统的寻址范围最大达到64KB。

采用功能引脚形成控制总线:由 RD(P3.6引脚)和 WR(P3.7引脚)作为读写选通信号线;由ALE作为地址锁存信号线,以配合P0口实现分时复用;PSEN以作为片外程序存储器读选通信号线;以EA作为片内和片外程序存储器的选择信号。

存储器的基本操作控制包括片选控制和读写操作控制。

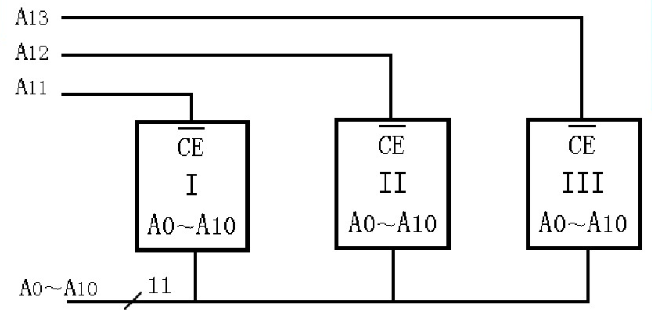

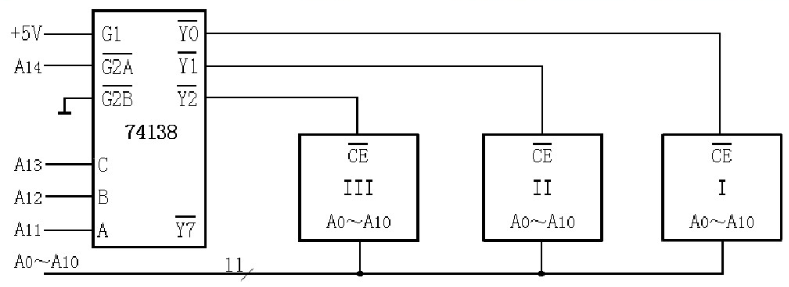

线选法:地位地址线(A0~A10)实现片内寻址,高位地址线线(A11~A13)实现片选。线选法连线简单,但地址空间不连续,适用于扩展容量较小且芯片数目较少的情况。

译码法:通过译码器将高位地址线转换为片选信号。译码法能有效利用存储空间,且地址连续,适用于多芯片下的扩展。常用译码器芯片有74138等。

三、储存扩展

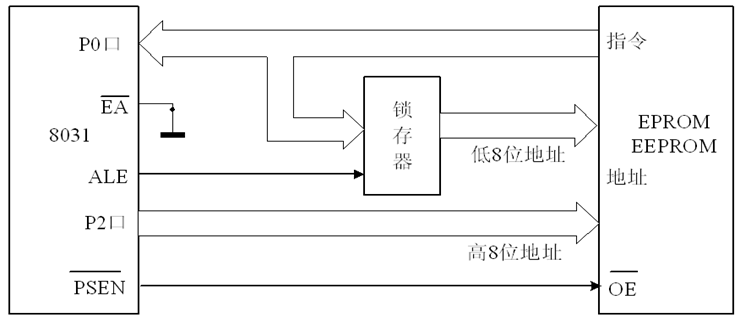

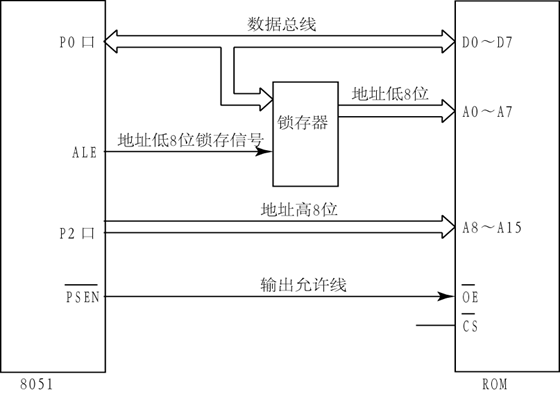

地址线:地址是由P0和P2口提供的。ROM的地址线(A0~A15)中,低8位A0~A7通过锁存器74LS373与P0口连接,高8位A8~A11直接与P2口的P2.0~P2.7连接。

数据线:片外ROM的8位数据线直接与单片机的P0口相连。

控制线:CPU执行ROM中存放的程序指令时,取指阶段就是对ROM进行读操作。读操作控制线有以下几条:

地址锁存信号ALE、片选信号CS、读选通信号OE、片外程序存储器的选用控制信号EA

地址锁存信号ALE:单片机的ALE管脚与锁存器的锁存使能端G相连,用于单片机从片外ROM在读指令时给出低8位地址的锁存信号。

片选信号CS:低电平有效。如果系统中只扩展了一片程序存储器芯片,可将该片选端直接接地,使该芯片一直有效。若同时扩展多片,需通过线选法或译码法来完成片选工作。

读选通信号OE:低电平有效。该引脚接8051的片外ROM读选通信号端PSEN。在访问片外程序存储器时,只要该端出现负脉冲,即可从ROM中读出指令或数据。

片外程序存储器的选用控制信号EA:当EA引脚接高电平时,CPU只访问单片机内部的程序存储器并执行内部程序存储器中的指令,但当程序存储量超过内部程序存储器的最大容量时,将自动转去执行单片机外部程序存储器内的程序。当输入信号引脚接低电平(接地)时,CPU只访问外部程序存储器并执行外部程序存储器中的指令。

在执行片外ROM读指令时,单片机自动进行的操作时序:

(1)首先由PO口和P2口给出16位地址,然后ALE出现下降沿通知锁存器将P0口的低8位地址锁存;

(2)PSEN出现低电平,使片外ROM有效;

(3)根据锁存器和P2口提供的地址取出指令并送P0口,由P0口读入单片机执行。

在上述过程中,数据存储器RAM读写信号端WR和RD一直处于高电平状态,使RAM与总线隔离。

四、控制程序

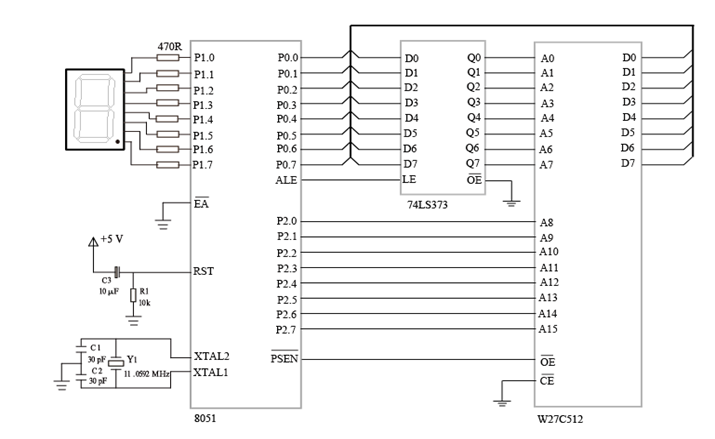

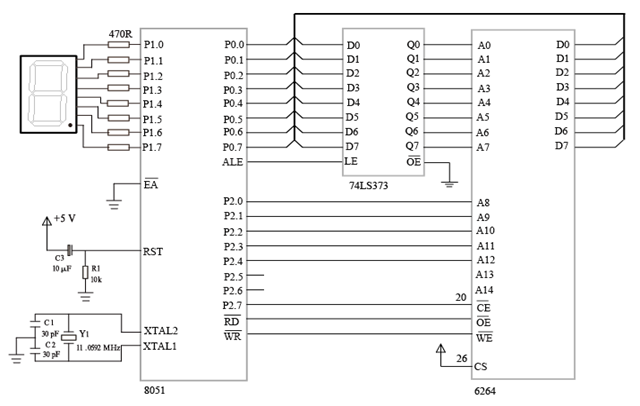

根据下图威廉希尔官方网站 编写程序用数码管显示0-9共10个数字循环显示。

#include 《reg51.h》unsigned char led[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90};//字型码

int main(void){ unsigned char i; while(1) { for(i=0;i《10;i++)//循环显示10个数字 { P1=led[i]; delay();//延时一段时间 } }}

void delay()//延时函数{ int i,j; for(i=0;i《3000;i++) for(j=0;j《5;j++);}

五、数据储存扩展

数据存储器RAM的扩展主要用到以下3个控制信号:

ALE:低8位地址锁存控制信号,通常接地址锁存器的LE引脚;

WR:外部RAM写信号,低电平有效,接数据存储器的WE引脚;

RD:外部RAM读信号,低电平有效,接数据存储器的OE引脚。

在执行片外RAM读写指令时,单片机自动进行的操作时序与读ROM相似:

(1)首先由PO口和P2口给出16位地址,然后ALE出现下降沿将P0口的低8位地址锁存;

(2)在读数据时,RD出现低电平,WR出现高电平,使读片外RAM有效,并根据锁存器和P2口提供的地址取出数据并送P0口,由P0口读入单片机。

(3)在写数据时首先将数据加载到P0口,然后RD引脚出现高电平,WR引脚出现低电平,使写片外RAM有效,并根据锁存器和P2口提供的地址将P0口上的数据写入片外RAM。

六、程序举例

根据图8-4编写程序将数码管显示0-9共10个数字的字型码存储到6264中,然后从6264中循环读出字型码并送数码管显示。

#include 《reg51.h》#include 《absacc.h》unsigned char led[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90};//字型码

int main(void){ unsigned char i; for(i=0;i《10;i++)//存储10个数字字型码 XBYTE[0x8000+i]=led[i]; while(1) { for(i=0;i《10;i++)//循环显示10个数字 { P1=XBYTE[0x8000+i]; delay();//延时一段时间 } } }void delay()//延时函数{ int i,j; for(i=0;i《30000;i++) for(j=0;j《5;j++);}

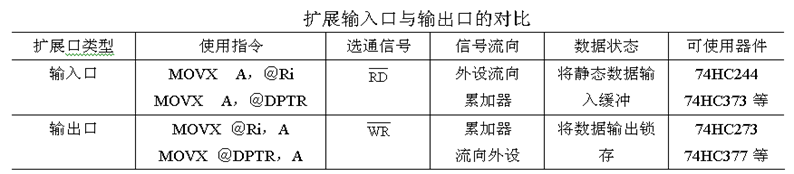

对输入/输出口功能的扩展,可以利用简单的TTL威廉希尔官方网站 或MOS威廉希尔官方网站 ,也可以使用结构较为复杂的可编程接口芯片。

MCS-51单片机将I/O口与片外RAM统一编址,两者合在一起使用同一个64KB的外扩展地址空间,因而,I/O口的输入、输出指令也就是片外数据存储器的读/写指令。

简单输入扩展主要采用三态数据缓冲器实现,目的是使被选通的输入设备能独占数据总线向单片机输入数据,而未被选通的设备与数据总线隔离。常用的三态数据缓冲器芯片有74LS244等。

简单输出扩展主要采用三态数据锁存器实现,目的是使单片机能通过数据总线向被选通的设备输出数据,而未被选通的设备与数据总线隔离。常用的三态数据锁存器芯片有74LS273等。

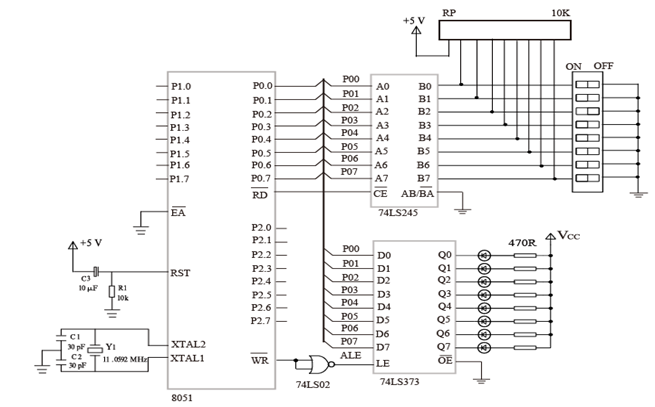

8051单片机使用74LS373和74LS245展I/O口,分别连接发光二极管和拨码开关,要求编写控制程序,通过开关的拨动控制发光二极管的亮灭。

#include 《reg51.h》#include 《absacc.h》 #define PORT XBYTE[0xFFFF] //地址写什么都可以int main(void){ unsigned char temp; while(1) { temp=PORT; //读存储单元操作,即通过74LS245获取开关数据 PORT=temp; //写存储单元操作,即通过74LS373用开关数据控制发光二极管 }}

编辑:lyn

-

MCS-51单片机系统扩展技术2008-12-01 1378

-

单片机存储扩展技术,下载2009-04-28 449

-

单片机I/O口键盘扩展方法2010-07-05 614

-

单片机灯光程序控制器电器威廉希尔官方网站 图2009-06-16 1206

-

单片机系统的扩展2010-06-29 715

-

单片机按键控制程序【汇编版】2015-12-29 821

-

单片机IO扩展(进阶)程序集合【C语言】2016-01-06 719

-

单片机教程之单片机总线与存储器的扩展资料说明2019-02-14 1388

-

单片机入门汇编之扩展中断服务子程序存储空间的办法详细程序资料说明2019-03-05 654

-

使用51单片机进行PWM程序控制智能小车程序免费下载2019-05-28 1251

-

如何对单片机进行片外程序存储器设计2020-03-20 4991

-

使用51单片机实现延时程序控制单灯闪烁的仿真文件免费下载2021-03-03 849

-

使用单片机实现延时程序控制播放歌曲的仿真设计实例2021-03-10 610

-

基于51单片机6264扩展内存仿真设计(proteus仿真+程序)2021-07-22 2036

-

Chapter9:单片机总线与系统扩展:《单片机》笔记2021-11-18 470

全部0条评论

快来发表一下你的评论吧 !