解析FPGA和USB芯片的加密盒设计与实现

电子说

描述

摘 要: 针对网络信息安全领域对数据加密和快速处理的需求,设计了一种基于FPGA和USB2.0芯片的数据加密盒,实现了高安全性的国产SM4对称密码算法。该设备在30个明文分组、10 000次循环的测试条件下数据加密速度可达到126 Mb/s。

0 引言

随着计算机网络技术的发展,黑客袭击事件逐年递增,给用户的数据安全造成很大的威胁。密码技术是实现网络信息安全的核心技术,是保护数据的重要工具[1]。通过在PC上运行软件进行加密的方法占用CPU资源多、处理速度慢、安全性差。近年来,通过采用FPGA、DSP等硬件实现密码算法的技术得到了更多的应用。当前我国的商用密码产品大多数采用PCI、USB接口,PCI接口的产品具有开发周期长、使用复杂等缺点,而USB接口的产品加密性能较差。

针对这些情况,设计了一种以FPGA为核心的USB加密盒,充分利用了FPGA的数据处理能力和控制能力,实现了安全可控的国产SM4对称密码算法。在使用中连接到用户终端,保证重要数据在网络中以密文的方式安全传输,具有加密速度快、灵活等优点,可广泛应用于金融、电信、税控等信息安全领域。

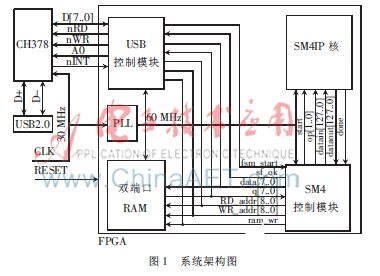

1 系统总体架构设计

加密盒由USB2.0芯片CH378和FPGA构成,系统架构如图1所示。通过Verilog语言在FPGA中设计了USB控制模块、SM4 IP核、SM4控制模块和双端口RAM。其中USB控制模块控制CH378,SM4 IP核实现SM4对称算法,SM4控制模块实现对IP核的控制,双端口RAM作为数据的缓存。CH378使用30 MHz时钟,利用锁相环PLL把时钟倍频到60 MHz作为系统的主时钟。FPGA各模块的时钟都为60 MHz,采用了完全同步的设计方式,可以有效避免毛刺,使系统稳定。

数据的加密过程是:上位机准备好明文分组数据,启动加密操作,USB控制模块控制CH378把数据传输到双端口RAM,数据传输完成后,启动SM4控制模块,把数据传输到SM4 IP核进行加密运算,运算完成后的密文分组数据由SM4控制模块传回到RAM,由上位机取回。数据解密过程完成从密文到明文的转换。

2 USB控制模块设计

2.1 CH378接口设计

CH378是南京沁恒电子公司的USB2.0芯片,支持USB设备方式和主机方式,内置了USB通信协议的基本固件和文件系统管理固件[2]。加密盒采用了USB设备方式、内部固件模式和8位并口的设计方式。CH378与FPGA的接口见图1,其中D是8位数据总线;nRD与nWR分别是读写控制引脚,低有效;A0是命令口与数据口的区分引脚,为高时写命令或读状态,为低时读写数据;nINT是中断输出引脚,低有效。

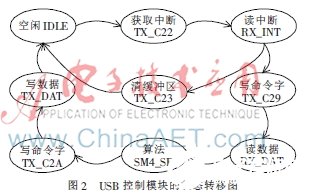

2.2 状态机设计

状态机是数字时序逻辑中重要的设计内容,通过状态转移图设计手段可以将复杂的控制时序以图形化表示,分解为状态之间的转换关系,将问题简化[3]。状态机是USB控制模块的核心,实现对CH378的控制。其状态转移如图2所示,对各状态的编码采用了格雷码,可以有效地防止毛刺,使系统稳定[4]。

系统上电后FPGA首先对CH378初始化,状态机处于空闲状态。采用USB的批量端点进行数据的传输[5],下传时数据由上位机传输到加密盒,端点号为0x02,支持最大包512 B;上传时数据由加密盒传输到上位机,端点号为0x82,最大包也是512 B。CH378完成数据的下传后通过nINT引脚向FPGA发送中断。在TX_C22状态FPGA向CH378写命令字0x22,请求获得中断状态值;状态机在RX_INT状态读取中断状态值,若为0x04表示端点0x02的接收器接收到数据,否则说明未能接收到数据;

在TX_C23状态,状态机释放USB缓冲区;在TX_C29状态,状态机向CH378写入命令字0x29和端点号0x02,使CH378准备从0x02端点缓冲区读取数据块,之后进入RX_DAT状态,依次把从端点缓冲区读取的数据分组长度和数据分组写入RAM,传输完成后CH378释放缓冲区,状态机进入SM4_SF状态,启动SM4控制模块。

SM4模块完成之后状态机进入TX_C2A状态,向CH378写入命令字0x2A和端点号0x82,使CH378做好发送数据的准备,之后进入TX_DAT状态,读取RAM中的运算结果并写入端点0x82的发送缓冲区,由CH378把数据发送到上位机。至此完成了数据的传输过程,状态机回到空闲状态。

3 SM4 IP核设计

3.1 SM4算法简介

SM4算法是由国家密码管理局发布的对称密码算法,分组长度和密钥长度都为128位。加密算法与密钥扩展算法都采用32轮非线性迭代结构[6]。解密算法与加密算法的结构相同,只是解密轮密钥是加密轮密钥的逆序。SM4算法的密钥空间包含2128个密钥,数量十分庞大,破解由SM4算法加密的密文难度极大,算法安全性很高。

3.2 IP核关键逻辑设计

SM4 IP核模块的接口见图1,start是算法启动信号;op是模式选择接口,为0时读入密钥,为1时进行加密操作,为2时进行解密操作;datain是数据输入;dataout是数据输出;done是运算结果输出标志位。

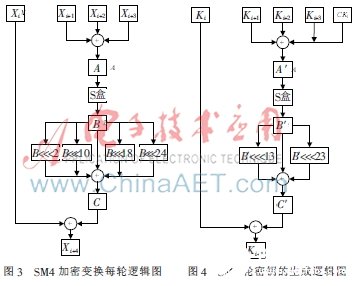

SM4加密算法采用了32轮非线性迭代结构,每轮变换的逻辑如图3所示。初始明文分组为(X0,X1,X2,X3)∈(Z232)4,(Z232)4为4个32 bit字,从端口datain输入,密文是(Y0,Y1,Y2,Y3)∈(Z232)4,轮密钥为rki∈Z232,i=0,1,2,…,31。在每一轮中Xi+1,Xi+2,Xi+3与rki相异或后形成数据A,即A=Xi+1⊕Xi+2⊕Xi+3⊕rki,经过S盒非线性变换成为数据B,即Sbox(A)=B。S盒中的数据采用查找表的结构预先存储于FPGA的ROM中,由16行×16列的字节数据构成。

例如A的低8位数据A[7..0]=0xEF对应于S盒中第E行和第F列的值,经过S盒变换后成为B[7..0]=Sbox(A[7..0])=0x84。A需要经过4个S盒并行运算后成为数据B。对B进行循环移位、异或后形成C,C=B⊕(B《《《2)⊕(B《《《10)⊕(B《《《18)⊕(B《《《24),最后C与Xi异或后形成Xi+4,即Xi+4=Xi⊕C。最终密文(Y0,Y1,Y2,Y3)=(X35,X34,X33,X32),从端口dataout输出。解密变换与加密变换结构相同,加密时轮密钥的使用顺序是:rk0,rk1,…,rk31,解密时轮密钥的使用顺序与加密时相反。

SM4算法的轮密钥由128 bit的加密密钥通过密钥扩展算法生成,设加密密钥MK=(MK0,MK1,MK2,MK3)∈(Z232)4,同样从datain输入。令Ki∈Z232,i=0,1,。。。,35,首先令(K0,K1,K2,K3)=(MK0⊕FK0,MK1⊕FK1,MK2⊕FK2,MK3⊕FK3),其中(FK0,FK1,FK2,FK3)∈(Z232)4为已知的系统参数。轮密钥的逻辑如图4所示,其中CKi是固定参数。经变换后轮密钥rki=Ki+4i=0,1,…,31。

4 SM4控制模块

SM4控制模块的作用是控制SM4 IP核进行数据的加密或解密,核心同样是状态机,其状态转移如图5所示,对状态的编码同样采用了格雷码。

状态机开始处于空闲状态,由fsm_start信号启动后进入RD_LEN状态,读取RAM中的数据分组长度。在RD_FLAG状态读取RAM中的模式选择位,判断执行加密或解密的操作;之后进入RD_KEY状态,从RAM中读取16 B的密钥数据后发送给SM4 IP核;之后进入WAIT1状态,等待IP核读取密钥;状态机进入RD_DAT状态后,依次读取RAM中的16 B明文数据发送给IP核;

进入WAIT2状态后,等待IP核把一个分组的数据处理完成(加密或解密),done信号输出高电平;进入WR_DAT状态后,把IP核运算完成后的128 bit数据分组(密文或明文)写入RAM;进入SF_JUDGE状态后,判断是否处理完所有的数据分组,若未处理完则返回到RD_DAT状态,若处理完所有的数据分组则返回空闲状态。一次USB批量传输可以处理的数据分组是1~30个。

5 双端口RAM模块

双端口RAM的作用是缓存数据,设计RAM的容量为512 B,上位机和FPGA可以对RAM进行独立访问,使设计更加灵活。对RAM的访问顺序如下:

(1)上位机写RAM:上位机把数据传送到端点缓冲区后,CH378把数据写入RAM,WR_addr是RAM的写地址端口,ram_wr是写使能端口,data是数据输入端口。

(2)SM4控制模块读RAM:启动SM4控制模块后,读取RAM中的数据并传送到SM4 IP核,RD_addr是RAM的读地址端口,q是数据输出端口。

(3)SM4控制模块写RAM:当IP核完成数据运算后,SM4控制模块将运算结果通过data端口写入到RAM。

(4)上位机读RAM:CH378读取RAM中的运算结果,传输到USB批量上传端点的发送缓冲区并把数据发送到上位机。

6 实验结果分析

FPGA芯片选用了Cyclone IV系列的EP4CE15F17C8N,I/O引脚数为166,RAM总量为63 KB,逻辑单元LE为15 408个[7]。整个设计在Altera的开发工具Quartus II 11.1中先后完成综合、功能仿真、布局布线后,通过逻辑分析仪并结合上位机软件进行调试。最终综合结果是:占用存储单元3 KB,逻辑单元3 921个。另外,经时序分析所有信号的建立、保持时间无违规路径。图6是调试通过的波形图。

图6显示了一个明文的加密过程,start信号变高后,SM4 IP核从端口datain读入明文,此时信号op=1指示加密过程的开始。运算完成后IP核的done信号变高,dataout端口输出128 bit的密文;之后SM4控制模块通过端口ram_di把密文写入到RAM中,写RAM地址WR_addr实现递增,RAM写使能控制信号ram_wr变为高电平。图中明文、密钥和密文与SM4算法标准数据一致。

上位机软件是结合CH378驱动程序和Visual C++6.0软件在Windows XP环境下开发而成的。对SM4算法的性能进行测试,设置每次批量传输时数据的最大分组为30个,通过10 000次循环测试,测得数据加密(解密)的速率为126 Mb/s。

7 结论

本文基于FPGA和USB2.0芯片的加密盒,通过FPGA实现了国密SM4对称密码算法,应用于工程实践中,满足用户对数据加密的需求。与市场上的密码产品相比,具有集成度高、加密速度快、性能高的优势。作为后续的工作,可以在FPGA中集成多种其他的国产密码算法,使得该加密盒的应用更加灵活和广泛。

参考文献

[1] 罗守山。密码学与信息安全技术[M]。北京:北京邮电大学出版社,2009.

[2] 南京沁恒电子公司.U盘和SD卡高速文件管理控制芯片CH378[Z].2013,5.

[3] 吴继华,王诚.Altera FPGA/CPLD设计(高级篇)[M]。北京:人民邮电出版社,2005.

[4] 夏宇闻.Verilog数字系统设计教程(第2版)[M]。北京:北京航空航天大学出版社,2008.

[5] 萧世文,宋延清.USB 2.0硬件设计(第二版)[M]。北京:清华大学出版社,2006.

[6] GM/T 0002-2012,SM4分组密码算法[S].2012.

[7] Altera Corporation.Cyclone IV Device Handbook[Z].2010.

编辑:jq

-

通过USBN9603/P89C51平台实现USB接口硬件加密2009-09-19 0

-

求实现FPGA模块的加密方法2012-04-18 0

-

fpga加密方法2013-01-01 0

-

加密芯片2014-03-14 0

-

(转)用FPGA实现加密2019-07-09 0

-

如何用单片机实现SRAM工艺FPGA的加密应用?2021-04-08 0

-

请问如何对SRAM工艺的FPGA进行加密?2021-04-13 0

-

通过USB接口实现FPGA 的SelectMap配置2009-05-26 718

-

基于PCI的数据加密系统的设计与实现2009-09-17 447

-

基于加密USB2.0接口芯片的设计及验证2009-12-10 922

-

基于FPGA加密芯片的DPA实现与防御研究2011-12-05 1163

-

RC4加密算法的FPGA设计与实现2016-05-10 1048

-

基于FPGA的安全USB系统的设计与实现李广位2017-03-19 861

-

ARM与FPGA的接口实现的解析2021-07-22 816

全部0条评论

快来发表一下你的评论吧 !