基于DSP+FPGA+ARM的架构实现高速多路数据传输系统的设计

描述

作者:詹必胜;吴斌方;杨光友 来源:电子产品世界

随着集成威廉希尔官方网站 技术的发展,FPGA和DSP以及ARM以其体积小、速度快、功耗低、设计灵活、利于系统集成、扩展升级等优点,被广泛地应用于高速数字信号传输及数据处理,以DSP+FPGA+ARM的架构组成满足实时性要求的高速数字处理系统已成为一种趋势,本文主要研究FPGA在高速多路数据传输中的应用。

系统结构

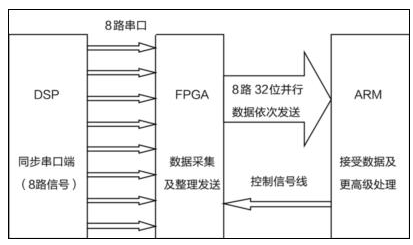

在DSP多路串行数据同时向ARM发送的系统中,因为数据通道有并行要求,应用FPGA硬件并行的特点,由FPGA并行接收多路数据,经过缓冲后再发送至ARM进行数据的高级处理的方案,系统结构图如图1所示。

图1 系统结构图

FPGA处理模块实现

DSP的串口传输方式为同步串口,每组DSP串口有4个端口,分别为:clk , frame. , data_a,data_b[3]。数据端口有两个,本例中只使能data_a,以下统一称为data。

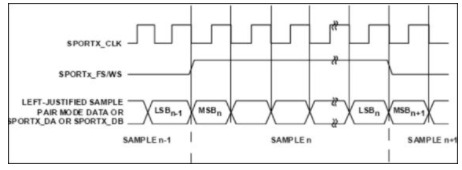

DSP同步串口传输时序如图2所示,当frame为1时,串行数据有效,当frame为0时,一帧数据传输结束。本例中DSP传输的一帧数据为32bit。

图2 DSP同步串口传输时序图

FPGA内部采用异步FIFO解决DSP时钟频率和FPGA时钟频率不匹配的问题,写时钟由DSP输出的同步时钟信号提供,时钟频率为60MHz;读时钟由FPGA的锁相环PLL时钟提供,PLL输出时钟频率为100MHz。

接收模块

由于DSP的8个同步串口同时写入,FPGA数据接收模块一共有8个,每个模块接收到的数据都存放在一个特定的FIFO中,将其称之为R_FIFO。

DSP输出信号为frame,clk, data,FPGA以DSP同步串口的输出时钟clk作为采集数据的时钟。系统上电结束后,FPGA等待ARM发送接收允许指令,接收允许后,FPGA就可以开始接收数据。

当frame信号为高,FPGA即开始接收从DSP发送的串行数据,在每个dsp_clk的上升沿读取一个bit的数据,之后将数据转入移位寄存器中。FPGA引入一个模块,时刻监测frame的下降沿,当frame下降时,即表示一个字的数据发送完毕,移位寄存器的数据放入R_FIFO的数据输入口,将R_FIFO的写使能置高,向R_FIFO发出写入请求,写入此时的数据至R_FIFO中,依次循环。当R_FIFO中的数据个数不为0时,即向FPGA的发送模块发送请求。

发送模块

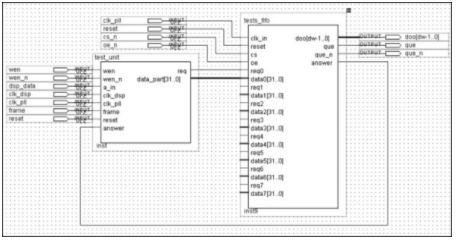

接收模块接收到DSP同步串口数据后,即通过reg与answer信号与FPGA数据发送模块之间进行数据传输,如图3所示。

图3 FPGA接收及发送模块

当接收模块有请求时,发送模块即将接收模块采集到的数据写入发送模块的缓存FIFO中,将其称之为S_FIFO。每轮从R_FIFO中传输的8个数据均依次存入S_FIFO中。

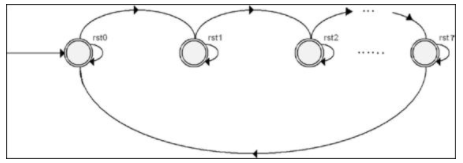

因为DSP的8个同步串口均同时工作,可以认为当有一个输入模块的数据接收完毕时,8个端口的数据均应该接收完毕,保险起见,可以延时若干时钟周期后开始接收数据。从端口0至端口7为一轮,若此时有端口没有数据,即可认为此端口暂无数据输出,用数据0替代,发送模块继续接收下一个端口的数据。用状态机来实现此功能,如图4所示。

图4 S_FIFO写操作的状态机图

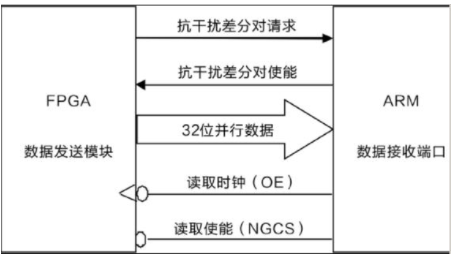

发送模块完成FPGA向ARM的数据传输,当FPGA发送模块S_FIFO中的数据达到一定数量时,FPGA即向ARM发出发送数据请求,ARM即开始对FPGA进行数据的读取。

FPGA中的S_FIFO同样也是异步FIFO。写时钟由锁相环提供100MHz;读时钟由ARM的读取使能信号OE取反得到,读使能由ARM的片选信号NGCS取反得到。ARM读取数据会产生NGCS与OE低电平信号,无操作时置高。每次读取数据时NGCS与OE先后置低,取反接至S_FIFO读端口分别为NGCS_N与OE_N。对S_FIFO读取时,每当读时钟OE_N为上升沿,读使能NGCS_N必为1,完成一次读取操作。

这样实现了ARM与FPGA之间的跨时钟域数据传输。FPGA发送数据采取乒乓操作, ARM可以源源不断的将S_FIFO中的数据读取出来。FPGA和ARM的数据传输原理图如图5所示。

图5 FPGA和ARM的数据传输

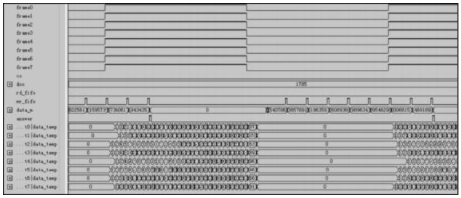

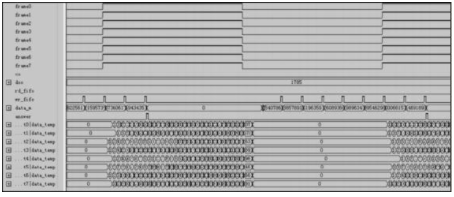

为验证各控制信号的时序逻辑,做如下仿真:FPGA接收及缓存数据。仿真的时序如图6所示。data_temp0~data_temp7为接收模块的移位寄存器,在frame的下降沿时将数据写入各自的R_FIFO中;R_FIFO中的数据依次通过寄存器data_m写入S_FIFO中。8次写入后,一轮缓存即结束,等待下次请求。

图6 FPGA接收及缓存数据时序仿真图

信号抗干扰处理

在FPGA和ARM之间的通讯中利用差分信号传输用于消除信号的干扰。差分对是指两条线路总是传送相反的逻辑电平,差分对信号对外界干扰源产生的噪声不敏感,例如威廉希尔官方网站 板的干扰噪声等。

如图7所示[5],IN引脚连接一个信号源,可以看到,对a噪声毛刺不敏感,但是对于b噪声毛刺,却有可能使其误认为一个脉冲,而这个可能引起FPGA内部的一些不期望的行为,如读出一个错误的值。

图7 差分降噪处理原理

差分对中的两个信号总是传送互补的逻辑值,所以当上图中的IN_P为逻辑1时,IN_N则为逻辑0,反之亦然。并且布线时,差分对的两条线路布线得非常的近,因此噪声对他们的影响都是相同的。接收端只对两个信号的差异感兴趣,若两个信号相同,则对此不敏感。

结语

利用DSP的实时数据处理能力与FPGA优越的硬线逻辑设计相结合,保证了多通道数据采集系统的实时性和精度要求,实现高速数据传输,同时简化系统硬件设计,缩小系统体积,具有极高的性价比。系统的数字部分硬件采用Verilog硬件描述语言实现,便于修改和升级,可根据实际测试应用需求作灵活的改进。本数据采集传输模块已成功实现,并取得了良好的应用效果。

责任编辑:gt

-

基于FPGA和DSP的1394b双向数据传输系统2012-05-14 0

-

基于FPGA的高速LVDS数据传输2014-03-01 0

-

基于ARM的无线数据传输系统设计与实现2015-03-26 0

-

基于FPGA+USB3.0接口的高速数据传输系统设计2018-08-09 0

-

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?2021-05-25 0

-

基于FPGA曼彻斯特码数据传输系统的实现2009-09-16 412

-

基于FPGA的高速多路数据采集系统的设计2009-12-19 518

-

基于FPGA和USB的高速数据传输、记录及显示系统2006-04-16 656

-

基于DSP的USB数据传输系统设计2009-11-20 1316

-

基于FPDP的高速数据传输系统设计2009-12-01 2152

-

USB2.0+FPGA实现多路数据传输系统2011-09-13 739

-

SOPC实现的PCI总线高速数据传输系统2012-02-10 1477

-

于FPGA的高速多路数据采集系统的设计2016-05-10 909

-

基于DSP和USB2_0高速数据传输系统的设计2017-10-19 747

-

基于Zynq-7000的SRIO高速数据传输设计与实现2017-12-21 2420

全部0条评论

快来发表一下你的评论吧 !