采用片上系统技术实现FC协议芯片的方案设计

描述

光纤通道(FC)是一个高性能的双向点对点串行数据通道。光纤通道的标准是由T11标准委员会(美国国家信息技术标准化委员会下属的技术委员会)制定的,它是一个为适应日益增长的高性能信息传输要求而设计的计算机通讯协议。FC集中了IO通道和网络的优点,它既支持IO通道所要求的带宽与可靠性,又支持网络技术的灵活性与连接能力,使得在同一物理接口上运行当今流行的通道标准和网络协议成为可能。目前,FC已被作为未来航空电子统一网络的一种主要联网标准。本文讨论了一种采用片上系统(SOC)技术来设计FC协议芯片的方案,分析了SOC设计方法的特点及其与传统的嵌入式系统设计方法的不同点,为今后在航电系统的设计中推广使用SOC技术奠定了基础。

FC工作原理简介

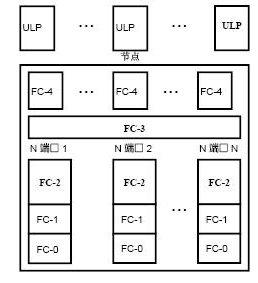

光纤通道所支持的物理介质包括光纤、双绞线、同轴电缆等,本文统称其为光纤。物理上,FC可被看成是称为N端口的多个通信点的连接,这些N端口可以通过交换网进行连接,且通过集线器构成仲裁环路,也可以通过点对点的链路进行连接。如图1所示,FC协议可以分成一系列的功能层次,各功能层次简述如下。

图1 FC的层次结构图

FC-0层

FC-0定义了接口和介质的物理特性,规定了收发器和各种物理媒介的光电参数。按照实现器件的不同,FC可具有不同的数据传输率:133Mbit/s,266Mbit/s,530Mbit/s,1.0625Gbit/s等。

FC-1层

FC-1定义了编解码和传输协议,它采用直流平衡8b/10b码。一个8位字节编码为10位进行传输,然后在接收端再进行解码。一部分具有特殊特性的没有使用的编码点被用来组成特殊字符,以形成信令和帧描述的有序集。

FC-2层

FC-2层是信号传输协议层。它规定了数据传输的规则,提供了数据块从一个端口传输到下一个端口的传输机制,定义了可由FC-4使用的功能和设备,FC-4可以只采用其中的一个子集。这一层描述了如下概念:

(1)节点和N端口及相应的标识符;

(2)通讯模型;

(3)拓扑结构;

(4)服务类;

(5)通用交换网模型;

(6)FC-2的构造块及体系结构;

(7)帧格式;

(8)序列;

(9)交换。

FC-3层

FC-3层为一些高级特性提供了所需要的通用服务,例如:

(1)分类:并行使用若干个N端口来增加带宽,以便通过多重连接传输一个单一信息。

(2)查询组:使数量多于一个的端口能响应相同的别名地址。这一服务通过减少接触到忙N端口的机会来提高效率。

(3)多播:将一个传输发送到多个目标端口,包括发送到一个交换网上的所有N端口(广播),或只发送到交换网上某些N端口。

FC-4层

FC-4层是FC协议的最高层,它规定了上层协议到FC协议的映射。当前映射的协议有:小型计算机系统接口(SCSI)、智能外设接口3(IPI-3)、高性能并行接口(HIPPI)、INTERNET协议(IP)、IEEE802.2、单字节命令码集映射(SBCCS)。另外,FC-AE还描述了一个基于1553B的上层协议映射。

FC-PH的物理模型

FC通路在物理上至少由2个节点组成。每个节点可以由多个N端口组成,每个N端口提供FC-0、FC-1、FC-2的功能。FC-3是可选的,它为多个N端口和FC-4提供通用服务。FC节点的组成如图2所示。

图2FC节点的组成

每个端口由一对光纤组成,一个用于输入,一个用于输出。这一对按相反方向传输的光纤和收发器组成FC链路,完成数据传输。

FC-2层的帧格式

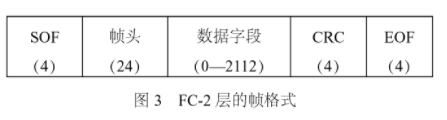

FC-2层的帧格式如图3所示。

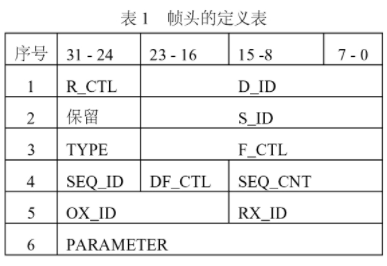

帧起始定界符SOF是一个有序集,4个8b字符,根据不同帧的类型有不同的码字;帧头,24个8b字符,详见表1;数据字段,0–2112个8b字符;CRC,4个8b字符,它对帧头部分和数据字段部分进行校验,其编码多项式是X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X+1;帧结束定界符EOF是一个有序集,4个8b字符,根据不同帧的类型有不同的码字。

FC协议芯片的设计概述

功能概述

FC芯片的功能是实现图1中的FC-PH,即FC-2、FC-1、FC-0层的协议;每个FC芯片支持2个N端口,可构成如图2所示的FC节点;支持的数据传输率为1.0625Gbits/s。

基于SoC的设计考虑

基于SoC的芯片设计和嵌入式模块板的设计有相似之处,但不能把SoC设计简单地理解为对嵌入式模块板的小型化,它们的主要区别如下:

(1)嵌入式模块板的设计是使用现有的CPU芯片和外设芯片来实现的,而SoC设计是由CPU内核与各种功能模块内核实现的。

(2)由上文可知,嵌入式模块板的设计是在已经设定的规则框架中进行的,这些规则就是各种芯片的使用手册,而SoC设计可以根据设计需求,自行设计规则,再设计各种功能模块内核,以满足功能要求并使得资源利用最优化。

(3)嵌入式模块板的设计,由于受到CPU芯片引脚的限制,外设芯片大多挂在CPU的一条外部总线上,难免会有总线争用,而SoC设计原则上芯片内部可以并行工作的总线个数没有限制,应充分利用这个特性,合理确定体系结构,避免总线争用。

(4)嵌入式模块板的设计,其软硬件的设计都有固定的模式,而SOC设计先要根据设计需求,确定软硬件的交会点,确定软硬件协同的规则,才能达到资源利用最优化的目的。

首先,要确定软硬件的交会点。软硬件的交会点放在FC-2层的“序列”上。因为“序列”负责整块数据的收或发,当数据块的长度超过图3所示的数据长度时,要分为若干个相关的数据帧来传输。数据帧的相关性表现在如表1所示的帧头中,只有序列计数字段SEQ_CNT发生改变。因此,软件将负责提供帧头的部分信息和数据,由硬件负责数据成帧和以后的工作。其次,在设计芯片的体系结构时,要充分使用芯片内部的并行工作的总线。最后,为便于本芯片的测试,对上层接口ULP,先考虑使用PCI总线,以便实现基于PCI接口的FC网卡。根据今后实际使用需求,ULP将按需设计。

芯片的结构

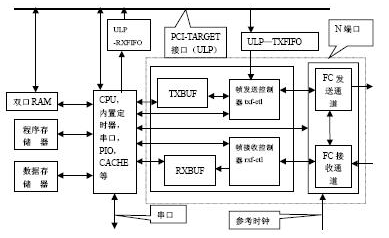

根据3.2节的讨论,FC协议芯片的结构框图如图4所示。FC协议芯片对上层的接口(ULP)采用PCI接口,由芯片内置的PCI-TARGET内核实现。

图4 FC协议芯片的结构框图

图4中虚线方框部分构成了FC的N端口,整个芯片中有2个N端口。每个FC-N端口由“FC收发通道”和“FC帧收发控制器”2层构成。“FC收发通道”与光电接口模块配合可实现FC-0层、FC-1层和FC-2层中数据帧收发的功能。该层为上层接口提供用于数据帧收发的片内FIFO通道。“FC帧收发控制器”实现FC-2层的数据帧打包、开包和检错。另外,通过芯片内嵌的软件模块实现FC-2层的序列和交换协议;同时提供ULP接口。下文对FC通道、帧收发控制器、CPU内核及ULP 接口作分别讨论。

FC收发通道模块的设计

功能概述

该模块主要完成FC-2层帧的收发,包括:完成SERDES(串-并互相转换模块)与光电接口的连接、完成FC-1层的8b/10b编解码、FC-2层帧级的CRC校验和FC有序集码的译码;同时利用内置存储器构成FIFO与FC芯片后端模块进行数据交换的缓冲区。

组成结构

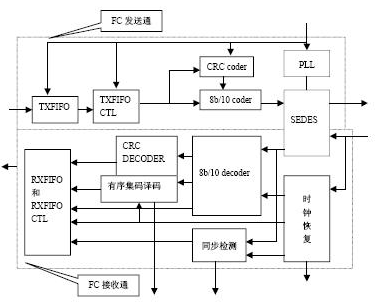

该模块分为“FC发送通道”和“FC接收通道”,如图5所示。在收发通道之间提供多种自环测试的通路(未在图中标出)。

“FC发送通道”主要由以下单元组成:

(1)并-串转化单元;

(2)发送时钟锁相环;

(3)8b/10b编码单元;

(4)CRC校验生成单元;

(5)TX-FIFO发送控制单元;

(6)TX-FIFO数据输入缓冲单元;

(7)自环控制单元。

“FC接收通道”主要由以下单元组成:

(1)串-并转化单元;

(2)接收时钟锁相环;

(3)时钟恢复单元;

(4)同步检测单元;

(5)有序集译码单元;

(6)8b/10b解码单元;

(7)CRC校验单元;

(8)RX-FIFO发送控制单元;

(9)RX-FIFO数据输出缓冲单元;

(10)自环控制单元。

图5FC通道结构框图

数据收发缓冲区的定义

数据缓冲区TX-FIFO、RX-FIFO的定义如表2所示:途中发送缓冲区是33位,低32位是发送的数据,第32位用于表示当前码字是否为有序集码。接收缓冲区是36位,低32位是接收到的数据,高位部分保存FC-2帧的CRC校验结果、8b/10b码的译码校验等信息。

5.1 功能概述

FC芯片中有两路“FC帧收发模块及其数据缓冲器”,它们实现FC-2层协议中的帧打包、开包。它是整个系统的软硬件交会点,是整个系统的核心,其关键在于制定相关的设计规则。

5.2 数据缓冲区的使用规则

根据多路总线并行工作的原则,设置四块独立的数据缓冲区,采用双口RAM,用于在CPU和帧收发器之间交换数据。收发数据缓冲区的使用规则如下:

(1)发送缓冲区TXBUF。根据图3所示的FC-2帧格式,该缓冲区用于存放帧头和有效数据。前24个字节是固定存放帧头的帧头区,后面是有效数据区。发送时,模块TXF-CTL从帧头区取帧头信息发送,根据寄存器中发送起始地址(TXOFFSET)和发送个数(TXCOUNT)的值从TXBUF中连续取数据发送。这里,只设置1个帧头区,是考虑到在“序列”中帧头具有相关性,同时1个帧头区不存在多个区域的切换,简化了硬件实现。

(2)接收缓冲区RXBUF。该缓冲区采用循环队列的方式,由模块RXF-CTL顺序写入数据,数据的存储顺序如图3所示的FC-2帧格式。在完成1帧数据接收后,模块RXF-CTL要在寄存器中表明当前帧在RXBUF中的接收起始地址(RXOFFSET)和接收到的个数(RXCOUNT)。CPU读取寄存器RXCOUNT后,该寄存器自动清零。上述使用规则是整个系统进行SoC设计的要点。

工作过程

数据的发送过程发送:

(1)CMD_RESET。模块TXF-CTL复位,进入空闲态。

(2)CMD_TEST:由CPU直接控制数据的发送,模块TXF-CTL进入空闲态。

(3)CMD_START_TX1:在空闲态并且CMD_TEST和CMD_START_TX2都无效时,进入按帧发送数据的状态,模块TXF-CTL发出SENDING信号。模块TXF-CTL先向FC发送通道的TX-FIFO发送有序集码lDLE(K28.5D21.4D21.5D21.5);根据SOF码型寄存器发送相应的SOF;然后从TXBUF的帧头区取数据依次发送;以后,如果数据从TXBUF取,则根据寄存器发送起始地址(TXOFFSET)和发送个数(TXCOUNT)从TXBUF中取出对应的数据发送;发送完有效数据后,再根据EOF码型寄存器发送相应的EOF;最后再发一个有序集码IDLE(K28.5D21.4D21.5D21.5)。一帧数据发完后,将SENDING信号清零,CMD_START_TX1清零,发中断信号INTTXi,然后回到空闲态。发送过程只有CMD_RESET可以中断。

(4)如果数据来在ULP-FIFO,则读发送个数(TXCOUNT),从ULP-FIFO中取数发送,若发送个数(TXCOUNT)大于FC-2帧规定的长度,则按2112字节的长度分多帧发送,每帧完毕,自动修改帧头中的帧记数值,并且自动选择相应的SOF和EOF定界符;若发送的过程中ULP-FIFO空,则自动结束这一帧的发送,并启动超时定时器,等待ULP-FIFO中的数据。当发送个数(TXCOUNT)规定的数据发完后,或者超时,则将SENDING信号清零,CMD_START_TX1清零,发中断信号INTTXi,然后回到空闲态。发送过程只有CMD_RESET可以中断。

(5)CMD_START_TX2:在空闲态当CMD_START_TX2有效时,模块TXF-CTL按有序

集码寄存器和有序集码参数寄存器的定义发送有序集码。

数据的接收过程

数据的接收有两种方式:由CPU直接控制;由RXF-CTL按FC-2帧格式接收数据。CPU可通过FC-2帧收发控制器的寄存器向模块RXF-CTL发命令来控制数据发送:

(1)CMD_RESET。模块TXF-CTL复位,进入空闲态。

(2)CMD_TEST:由CPU直接控制数据的接收。

(3)CMD_START_RXi:在空闲态并且CMD_TEST无效时,进入按帧接收数据的状态。模块RXF-CTL从FCSET-A的RX-FIFO中收到有序集码SOF后,发出RECEIVE信号,表示已经开始1帧数据的接收。模块RXF-CTL将收到的数据依次写入循环缓冲区RXBUF。再收到任一个有序集码后,1帧数据接收结束,将RECEIVE信号清零。更新寄存器接收起始地址(RXOFFSET)和接收到的个数(RXCOUNT)。如果接收到的CRC码无效或者最后一个有序集码不是EOF,则将接收有错(RXERR)置‘1’,否则发出INTRXi中断信号,表示收到1帧正确的数据。继续下一帧的数据的接收。在1帧数据接收的过程中,只有CMD_RESET可以中断;如果尚未开始接收1帧数据,则CMD_TEST可使其回到空闲态。CPU读寄存器RXOFFSET、RXERR和RXCOUNT可知道接收到的数据存放的地址和个数以及数据帧是否有效。

另外CMD_START_Rxi还用来控制FC接收通道中的RX-FIFO控制器。CMD_START_Rx1控制FC接收通道按FC-2帧接收数据存入RX-FIFO;CMD_START_Rx2控制FC接收通道接收所有数据(除了连续的IDLE有序集码之外)存入RXFIFO。

内置CPU的配置及ULP的设计

内置CPU通过嵌入的软件完成FC-2层的序列和交换的协议,同时实现ULP与上层的通讯。

CPU外设的配置

CPU配置的外设和总线接口定义如下:

(1)两个RS232串行口。

(2)看门狗定时器:WATCHDOG-TIMER。

(3)两个FC-2层通讯用的定时器:FCTIMER1,FC-TIMER2。

(4)接收两路FC-2帧收发控制器中断的PIO:INTFRAME-PIO。两个接受来自RX-FIFO的有序集译码的PIO:ORDERSET-PIO1,ORDERSETPIO2。两个内总线接口,用于操作两路FC-2帧收发控制器。可根据操作功能需要,对FC-2帧收发控制器的各寄存器进行定义。

(5)四个独立的连接收发数据缓冲区的内总线接口。

(6)三条独立的存储器总线接口:双口RAM、程序存储器和数据存储器。

(7)与ULP交换数据的ULP-RXFIFO接口。

(8)与ULP握手的ULP-PIO接口。

ULP的数据通道

如图4所示,FC芯片对ULP提供了两种数据通道:双口RAM和FIFO。双口RAM通道:可根据ULP的需要划分成若干分区,ULP可通过PCI接口对它存取数据。FC芯片的内置CPU从双口RAM中读数据,放到TXBUF中,然后启动“帧发送模块”打包发送;接收数据时,CPU从RXBUF中读取数据,存到双口RAM的相应的数据分区中,通知ULP来取数据。这种数据通道对需要确认,出错要重传的消息比较有效。

FIFO通道:ULP将数据通过PCI接口写到ULP-TXFIFO中,CPU设定“帧发送模块”从ULP-TXFIFO中取数据,“帧发送模块”在数据打包时,从ULP-TXFIFO中取数据;接收数据时,CPU从RXBUF中读取数据,存到ULP-RXFIFO。这种数据通道对视频数据等实时性要求高的消息比较有效。

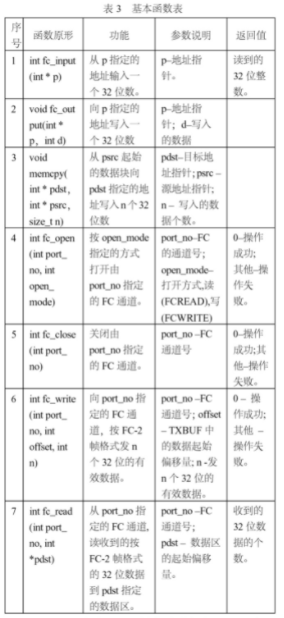

FC芯片嵌入软件的基本操作函数

FC芯片的嵌入软件要完成FC-2层的交换、序列、帧收发、差错控制、流量控制等功能。它们需要调用的基本操作函数如表3所列。这些基本操作函数是与硬件平台相关的函数,在平台上所作的其他函数将与硬件平台无关。这样,有利于软硬件协同开发,互相隔离错误。这是SOC设计的又一个重要原则。

结论

目前,高端的FPGA中已内嵌了适应高速传输的收发器、锁相环和大量的存储器,本文讨论的FC协议芯片可以在这类FPGA上实现原型样机。光纤通道以其传输速度高、兼容性好等特点在未来的航空电子统一网络中将得到广泛的应用,本文讨论的FC协议芯片将为这一应用奠定物质基础。本文以FC协议芯片的设计为例,介绍了基于SoC设计的思考重点和SoC设计的基本原则,它将有助于在航电系统的设计中推广使用SoC技术。

责任编辑:gt

-

519.soc片上系统小凡 2022-10-04

-

基于FPGA的AFDX端系统协议芯片的设计与实现2010-05-13 0

-

使用FPGA来实现FC协议的方法?2020-08-17 0

-

基于FPGA单芯片实现ARM系统设计解决方案2021-07-12 0

-

ADSL收发器片上系统芯片的设计与实现2010-01-26 1167

-

基于PSoC片上系统芯片的非接触式感应按键界面设计2010-09-14 1102

-

片上芯片SoC挑战传统测试方案2012-01-28 2019

-

基于MCGS的货物分拣系统监控方案设计与实现_耿瑞芳2017-03-18 867

-

采用最新片上系统,实现电机控制方案2018-03-08 9529

-

基于片上系统的SOC设计验证方案2018-06-01 1530

-

SOC片上系统的解决方案2018-06-26 5833

-

基于ZigBee无线技术的城市路灯照明系统解决方案设计2023-10-26 219

-

片上系统soc芯片技术介绍2024-03-28 770

-

片上系统代表芯片吗2024-03-28 691

全部0条评论

快来发表一下你的评论吧 !