数字集成威廉希尔官方网站 芯片的设计流程详解

电子说

描述

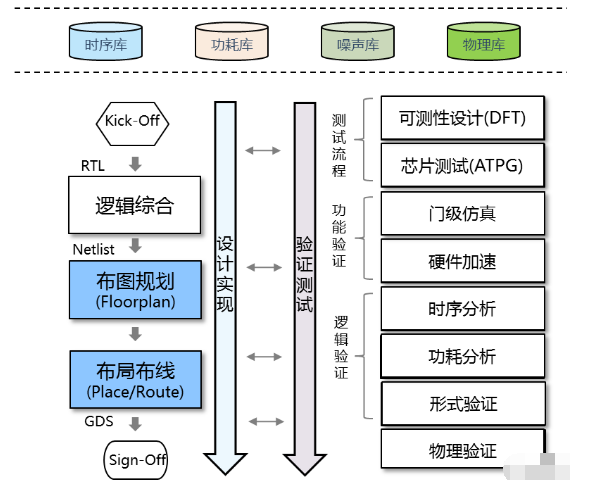

数字集成威廉希尔官方网站 芯片的设计流程由一系列的设计实现和验证测试过程组成(图1)。首先是功能定义,它描述了对芯片功能和性能参数的要求,我们使用系统设计工具设计出方案和架构,划分好芯片的模块功能。然后是代码设计,我们使用硬件描述语言(HDL,如Verilog)将模块功能表示出来,形成电脑能理解的代码(行为级、RTL级)。经过仿真验证后,进行逻辑综合,把代码翻译成低一级别的门级网表,它对应于特定的面积和参数,并再次做仿真验证。这两个仿真可以是用威廉希尔官方网站 模型验证逻辑功能(逻辑仿真),也可以用FPGA硬件威廉希尔官方网站 来验证(原型仿真),其速度更快,与实际威廉希尔官方网站 更接近。设计和仿真验证是反复迭代的过程,直到验证结果完全符合规格要求。验证还包括静态时序分析、形式验证等,以检验威廉希尔官方网站 的功能在设计转换和优化的过程中保持不变。可测性设计(DFT、ATPG)也在这一步完成。下一步就是数字威廉希尔官方网站 后端实现中最为关键的布局布线,它实现威廉希尔官方网站 模块(如宏模块、存储器、引脚等)的布图规划、布局,实现电源、时钟、标准单元之间信号线的布线。在布局布线过程中及完成之后,需要对版图进行各种验证,包括形式验证、物理验证,如版图与逻辑威廉希尔官方网站 图的对比、设计规则检查、电气规则检查等。最终输出GDS数据,转交芯片代工厂,在晶圆上进行加工,再进行封装和测试,就得到了我们实际看见的芯片。

图1数字威廉希尔官方网站 设计验证流程

本文所指的后端实现工具主要是指布图规划(Floorplan)和布局布线(Place&Route)两个阶段所使用到的工具集合。目前芯片设计公司使用的主要软件有SynopsysICC2/FusionCompiler,CadenceEncounter/Innovus,MentorGraphicsNitro-Soc等。

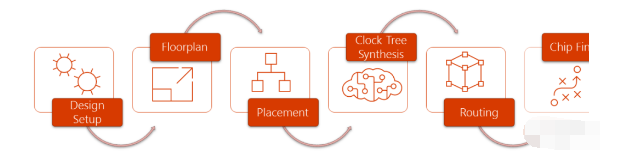

图2数字后端实现过程

数字后端的设计过程,是把逻辑综合映射后的威廉希尔官方网站 网表转换为GDS的过程,也就是把威廉希尔官方网站 从逻辑网表转换为几何版图的过程。业界各个工具系统的实现大同小异,一般可以细分为设计环境建立、布图规划、布局、时钟树综合、布线、调试完善等步骤(图2)。

1.设计环境建立

设计环境的建立是把后端设计所需的数据读入到数据库,然后检查数据的完整性与一致性。后端设计的输入数据包括门级网表、设计约束和工艺库文件三部分。其中,门级网表(GLN,GateLevelNetlist)是逻辑综合工具把设计从RTL(RegisterTransferLevel)映射到GLN所得,它同时满足时序、面积、功耗等约束。设计约束SDC(SynopsysDesignConstraints)则描述了时钟、延迟、电源、面积、设计规则、工作条件等等对芯片的约束条件。工艺库主要是时序库文件和模型库文件,如物理抽象库文件LEF、物理详细库文件GDS/OASIS、时序库文件.lib、RLC模型文件.rlc、EM规则文件、DEF文件等等。

2.布图规划Floorplan

布图规划是后端实现中需要手工活的惟一阶段,其它阶段都是通过修改脚本和约束,然后让工具自动完成的。布图规划的好坏,直接决定了后续布局布线的收敛、芯片的面积性能功耗。Floorplan一般都是由经验丰富的设计师来完成。现在Cadence、谷歌也在探索使用AI来实现Floorplan。它包括初始化、布放宏模块和布放输入输出脚等过程。我们需要根据设计前端所给的数据流向,了解设计中各个模块之间的交互、各个时钟之间的关系等信息,以规划模块的位置和模块接口的位置。模块形状与设计类型相关,也影响到绕线资源的使用,这在前端中只考虑逻辑功能不同,需要仔细规划。低功耗设计则需要提前规划好各个电源域的划分区域、隔离岛等。在布放电源地时,需要根据芯片功耗估算,添加芯片核心的电源地;根据SSO、ESD、EM估算,添加输入输出脚的电源地。输入输出脚添加完成后,根据宏模块、IP、IO的面积就可以估算出芯片的面积了。

3.电源及电源网络分析

在现代低功耗芯片设计中,电源设计是非常重要的一步,包括分析计算所有单元的功耗、静态IRDrop和电迁移EM分析。它可以在多个阶段进行,如布图后、电源地布线后、全局布局后、详细布线后等。它分析电源设计是否合规。分析计算过程包括线网活动因子计算、电源分析、电源网分析、电网电阻分析、阻抗失配分析、IRDrop分析、EM分析等等。

4.静态时序分析

通过建立和使用静态时序分析器,以验证设计符合所有的设计约束,如满足在所有要求操作条件下的建立和保持时间,或者识别出违反时序的原因所在。静态时序分析主要包括数据准备、分析条件设置、生成时序报告、分析报告。所需要的数据(威廉希尔官方网站 网表、时序库、约束文件、寄生模型及外部寄生文件)在第一步已经读入到数据库中,这里也可以补充读取。分析条件则是在一个或多个模式下,考虑PVT、RCX、OCV、CRPR等诸多因素进行设置。根据分析所需,控制分析器执行适当的命令,得到时序分析报告。对报告进行分析后,执行相应的操作。例如,从时序路径分析报告中,可以看到设计的关键路径,进而执行增量式的修改以符合时序需求。

5.定义电源结构

这一步是为电源的绕线创建禁区,创建电源带、电源环、标准单元rail等,定义如何连接到宏模块的电源脚等,完成电源的绕线,报告电源的状况。

6.布局及优化设计

这一过程包括为布局和优化作准备(布局指南和布局分组)、进行无优化的布局、插入备用单元(为ECO做准备)和Tap单元、管理扫描链(重排或拆分)、进行布局和优化、分析布局和优化结果,决定是否需要迭代。传统的时序驱动的布局算法通常会留下很多时序违反,因为它们不能仅仅由布局修正。时序违反由布局后优化工具找到后,它就会做很多修改,以符合时序约束的要求,如修改单元尺寸、插入缓冲、分解驱动等,这些操作会逐步降低原始布局的质量。因此,为满足时序和拥挤约束的目标,需要进行多次布局迭代和优化。我们工具的布局和优化引擎是并行的,从宏固定的预布局开始,就能得到一个最好时序质量和最低拥挤程度的全布局。布局和设计优化也能在一个布局好的设计上增量式地进行。

7.时钟树综合

布局之后,就是布线工作。我们要首先完成时钟网络的布线,因为它们比普通数据通路上的线网更重要。在数字威廉希尔官方网站 中,时序元件的数据传输是由时钟控制的。时钟频率决定了数据处理和传输的速度,时钟频率也就决定了威廉希尔官方网站 的最终性能。决定时钟频率的主要因素有两个,一是组合逻辑部分的最长威廉希尔官方网站 延时,二是时序元件内的时钟偏斜(clockskew)。组合逻辑部分可以优化的延时不多,时钟偏斜成为影响威廉希尔官方网站 性能的制约因素。时钟树综合的一个主要目的就是减小时钟偏斜。时钟信号是数字芯片中最长最复杂的信号,从一个时钟源到达各个时序元件的终端节点,能形成了一棵树状的结构。从时钟源的扇出很大,负载很大,需要一个时钟树结构,通过一级级的器件去驱动最终的叶子节点。时钟树综合的另一个目的,就是要使同一个时钟信号到达各个终端节点的时间相同。采用的办法也很简单:在时钟信号线网上插入buffer或者inverter来平衡信号的延迟。时钟树综合的准备包括标记可用于时钟树的buffer/inverter、定义时钟结构规则(如绕线、时钟单元周边间距、buffer等)、生成时钟skew约束(即定义各种skew组和时序约束),然后综合时钟树,再对综合结果进行分析和优化,如修复setup时间违反、额外的功耗和面积收复等等。

8.布线及设计优化

这一步虽然是一个自动化进行的步骤,但也需要创建布线指南,以指导布线器的运作。过程包括全局布线、总线布线、详细布线、手动优化、添加防护、金属填充、天线效应修复、光刻修复、绕线到bump等等。

9.工程改动要求ECO(EngineeringChangeOrder)

ECO是在一个完成或接近完成的设计上,进行一个增量式的改变。可能是对设计网表、布局或绕线作一个小的改变,而设计的主体部分中不变的部分无须重建。ECO可能涉及到所有层的改变,或者仅仅涉及到金属层的改变。假若修改的门数不到整体的5%,那么ECO是值得的。另外,使用usefulskew来进行手工的时钟树ECO,也是一项重要的技能。

10.时序调试

时序调试的目的,是找到一个方法去修复所有约束违反。我们需要用不同的选项去运行时序分析器,分析各种时序报告,识别可能的时序问题,在GUI和版图上同时查看关键路径,提升设计的时序。时序的优化贯穿着整个数字威廉希尔官方网站 后端设计全过程。

11.数据导出

设计的最后一步,就是威廉希尔官方网站

版图数据GDS的导出。GDS描述了晶体管大小和物理位置、连线的宽度和位置等制造芯片所需的全部信息。对GDS的要求是功能与RTL一致、性能满足指标、规格满足代工厂要求、功耗性能面积(PPA)优良。EDA工具强调的是A,Automation,也就是自动化。这在数字集成威廉希尔官方网站

后端设计工具中表现尤为突出。要处理规模大至数十亿晶体管的威廉希尔官方网站

,对所涉及算法的性能、效率、资源占用等都有极高的要求。目前,我们正在努力探索在数字芯片全流程中应用最新的AI技术、云计算技术等,以满足各种现代芯片的设计要求。

责任编辑人:CC

- 相关推荐

- 集成威廉希尔官方网站

- 数字集成威廉希尔官方网站

-

数字集成威廉希尔官方网站 速查2011-01-31 0

-

数字集成威廉希尔官方网站 -威廉希尔官方网站 、系统与设计 免费下载2009-02-12 0

-

数字集成威廉希尔官方网站 设计流程.ppt——独家资料2011-11-22 0

-

数字集成威廉希尔官方网站 应用+制作 PDF+22016-09-26 0

-

什么是数字集成威廉希尔官方网站 IC2021-03-03 0

-

CMOS数字集成威廉希尔官方网站 是什么?CMOS数字集成威廉希尔官方网站 有什么特点?2021-06-22 0

-

数字集成威廉希尔官方网站 设计教学大纲2010-09-20 1102

-

数字集成威廉希尔官方网站 简介2006-04-16 2502

-

数字集成威廉希尔官方网站 的类别2009-09-19 1518

-

数字集成威廉希尔官方网站 _什么是数字集成威廉希尔官方网站2011-10-28 4263

-

数字集成威廉希尔官方网站 版图提取2011-10-28 1460

-

数字集成威廉希尔官方网站 实验2016-05-10 667

-

数字集成威廉希尔官方网站 设计透视资料下载2021-11-03 985

-

数字集成威廉希尔官方网站 测试流程2023-05-26 4008

-

音响集成威廉希尔官方网站 是数字集成威廉希尔官方网站 吗2024-09-24 337

全部0条评论

快来发表一下你的评论吧 !