优化信号链的电源系统 — 第2部分:高速数据转换器

电源/新能源

描述

作者:ADI公司 John Martin Dela Cruz 和 Patrick Errgy Pasaquian

简介

在“电源系统优化”系列文章的 第1部分 ,我们介绍了如何量化电源噪声灵敏度,以及如何将这些量值与信号链中产生的实际影响联系起来。有人问到:高性能模拟信号处理器件要实现出色性能,真正的噪声限值是多少?噪声只是设计配电网络(PDN)时的一个可测量的参数。如 第1部分所述,如果单纯只是最小化噪声,可能需要以增大尺寸、提高成本或者降低效率为代价。优化配电网络可以改善这些参数,同时将噪声降低到必要的水平。

本文在阐述高性能信号链中电源纹波的影响的基础上进一步分析。我们将深入探讨如何优化高速数据转换器的配电网络。

我们将对标准PDN与经过优化的PDN进行比较,了解在哪些方面可以实现空间、时间和成本优化。后续文章将探讨适合其他信号链器件(例如RF收发器)的特定优化解决方案。

AD9175双通道12.6 GSPS高速数模转换器的电源系统优化

AD9175 是一款高性能、双通道、16位数模转换器(DAC),支持高达12.6 GSPS的DAC采样速率。该器件具有8通道、15.4 Gbps JESD204B数据输入端口、高性能片内DAC时钟倍频器和数字信号处理功能,适合单频段和多频段直接至射频(RF)无线应用。

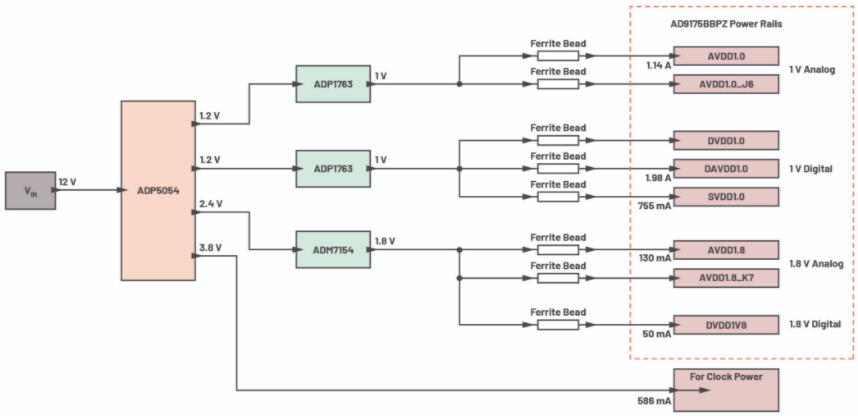

图1.集成在现成评估板上的AD9175高速DAC的标准PDN。

我们来看看如何为这个双通道高速DAC优化PDN。图1显示安装在现成评估板上的AD9175高速DAC的标准配电网络。该PDN由一个ADP5054分立式四通道开关和三个低压降(LDO)后置稳压器构成。旨在验证是否可以改进和简化该PDN,同时确保其输出噪声不会导致DAC性能大幅下降。

AD9175需要8个电源轨,可以分为4组,分别是:

·1 V模拟(2个电源轨)

·1 V数字(3个电源轨)

·1.8 V模拟(2个电源轨)

·1.8 V数字(1个电源轨)

分析:噪声要求

在我们实施优化之前,必须先了解这些电源轨的电源灵敏度。我们将重点讨论模拟电源轨,因为相比数字电源轨,它们对噪声更加敏感。

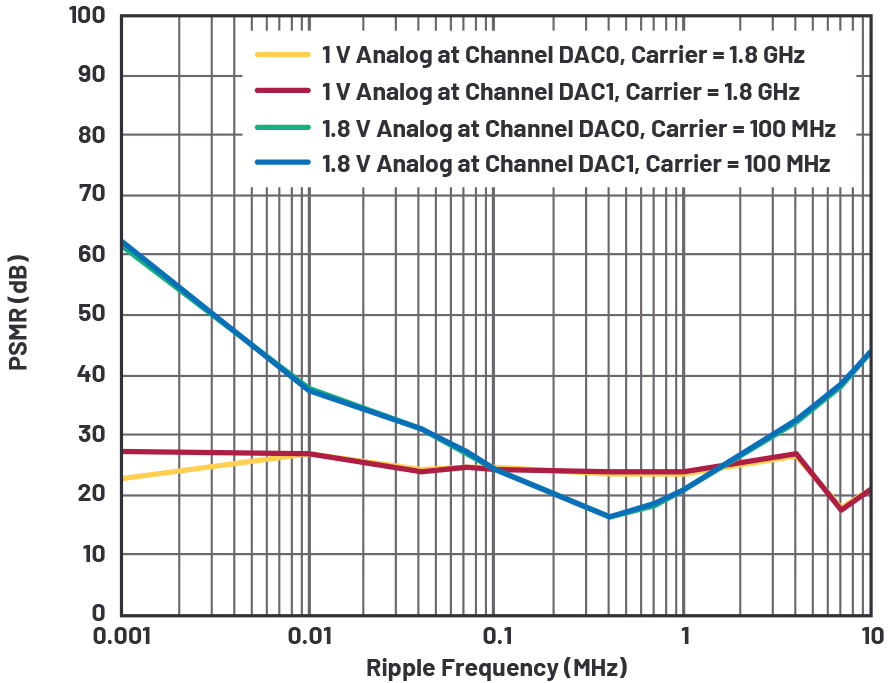

模拟电源轨的电源调制比(PSMR)如图2所示。注意,1 V模拟电源轨在1/f频率区域内较为敏感,而1.8 V模拟电源轨在开关转换器的工作频率范围(100 kHz至约1 MHz)内更敏感。

图2.1 V模拟电源轨和1.8 V模拟电源轨上的AD9175高速DAC PSMR。

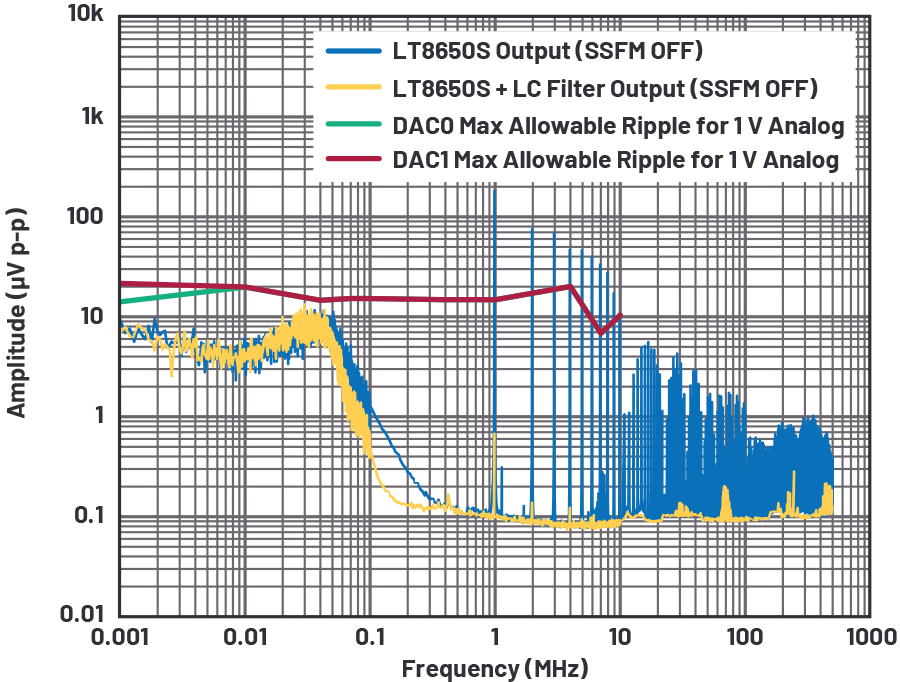

一种优化方法是使用带有LC滤波器的低噪声开关稳压器。图3显示 LT8650S Silent Switcher®稳压器(带和不带LC滤波器)在展频(SSFM)模式关闭时的传导频谱输出。如 第1部分所述,SSFM可以降低开关频率噪声幅度,但会因为三角调制频率在1/f区域产生噪声峰值。由于1/f噪声已小幅偏离该阈值,增加的噪声可能超过此电源轨的最大允许纹波阈值。因此,不建议在这种情况下使用SSFM。最大允许电压纹波阈值代表电源纹波电平,当超过该值时,DAC载波信号中的边带杂散将出现在DAC输出频谱的1 µV p-p本底噪声上方。

从这些结果可以看出,开关稳压器的1/f噪声没有超过1 V模拟电源轨的最大允许纹波阈值。此外,LC滤波器足以将LT8650S的基本开关纹波和谐波降至最大允许纹波阈值以下。

图3.LT8650S传导频谱输出与1 V模拟电源轨的最大允许纹波阈值之间的关系。

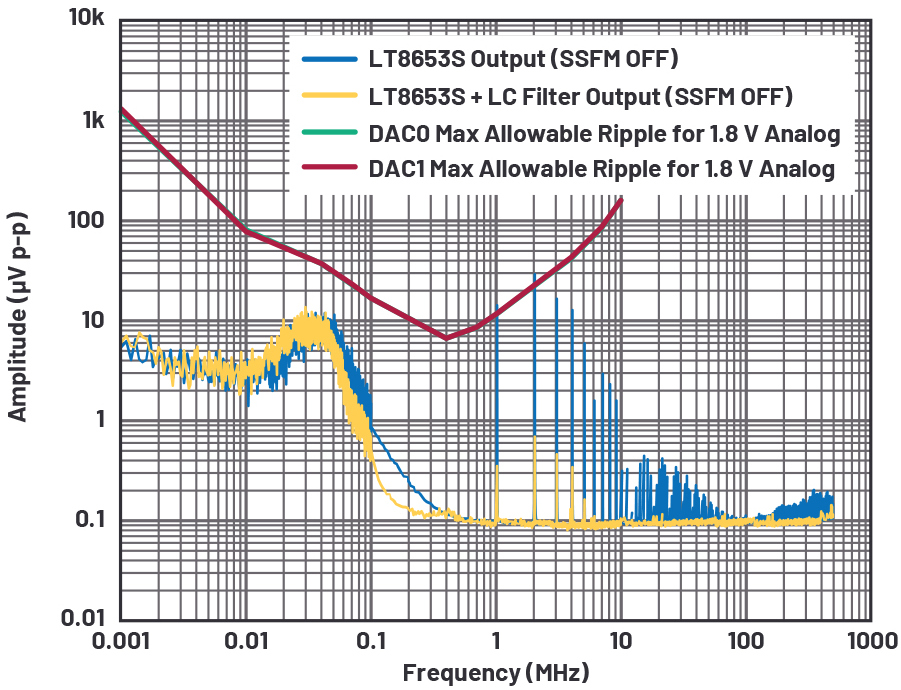

图4显示 LT8653S (带和不带LC滤波器)的传导频谱输出。如图所示,1.8 V电源轨的最大允许电压纹波不会在AD9175输出频谱的1 µV p-p本底噪声内产生杂散。可以看出,LT8653S的1/f噪声没有超过最大允许纹波阈值,LC滤波器足以将LT8653S的基本开关纹波和谐波降至最大允许纹波阈值以下。

图4.LT8653S传导频谱输出与1.8 V模拟电源轨的最大允许纹波阈值之间的关系。

结果:优化PDN

图5显示AD9175的优化配电网络。旨在提高效率,降低空间要求以及图1中PDN的功率损耗,同时实现AD9175出色的动态性能。噪声目标是基于图3和图4所示的最大允许波纹阈值。

优化的配电网络由LT8650S和LT8653S Silent Switcher稳压器,以及模拟电源轨上的LC滤波器构成。在这个PDN中,1 V模拟电源轨由LT8650S的VOUT1供电,LT8650S后接LC滤波器;1 V数字电源轨直接由同一个LT8650S的VOUT2供电,其后无需连接LC滤波器。对于AD9175,其数字电源轨对电源噪声不太敏感,因此可以在不降低DAC动态性能的情况下直接为这些电源轨供电。带有LC滤波器的LT8653S直接为1.8 V模拟和1.8 V数字电源轨供电。

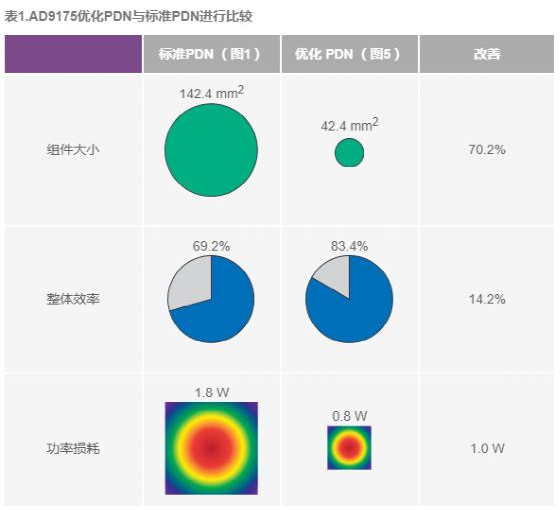

表1比较了优化PDN和标准PDN(如图1所示,由一个四通道降压开关和三个LDO稳压器构成)的性能。从组件大小来看,优化后的解决方案比标准解决方案减小70.2%。此外,效率从69.2%提高到83.4%,整体节能1.0 W。

图5.AD9175高速DAC的优化PDN。

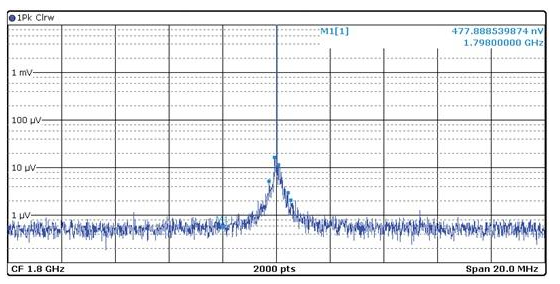

为了验证优化PDN的噪声性能是否足以满足高性能技术规格要求,对AD9175进行相位噪声评估,并检测载波周围边带杂散的DAC输出频谱。1如表2所示,相位噪声检测结果在数据手册技术规格规定的限值内。AD9175输出频谱的载波频率很干净,没有可见的边带杂散,如图6所示。

图6.使用优化PDN的AD9175输出频谱(1.8 GHz、–7 dBFS载波)。

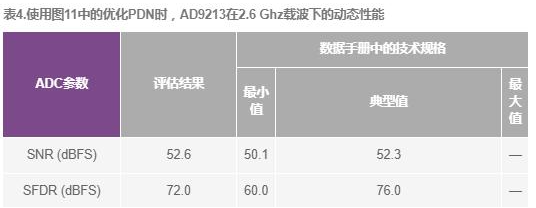

表2.使用图5中的优化PDN时,AD9175在1.8 GHz载波下的相位噪声

AD9213 10.25 GSPS高速模数转换器的电源系统优化

AD9213是一款单通道、12位、6 GSPS或10.25 GSPS、射频(RF)模数转换器(ADC),具有6.5 GHz输入带宽。AD9213支持高动态范围频率和需要宽瞬时带宽和低转换误差率(CER)的时域应用。AD9213具有16通道JESD204B接口,以支持最大带宽能力。

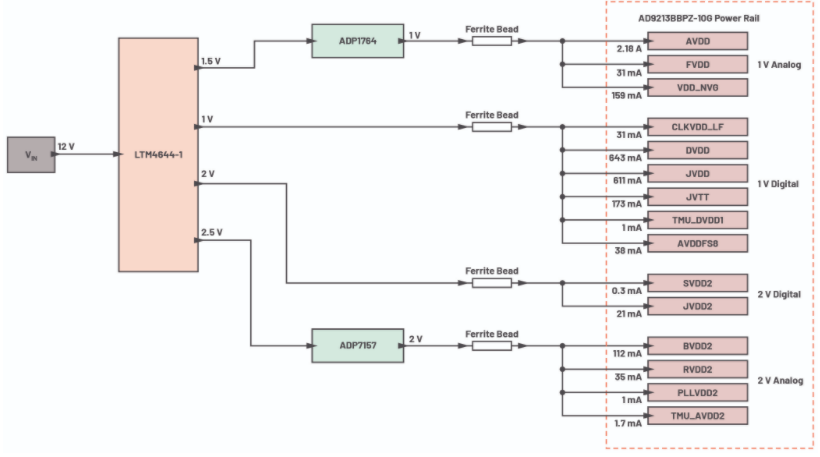

图7显示现成评估板上AD9213高速ADC的标准配电网络,由一个 LTM4644-1 µModule® 四通道开关和两个线性稳压器构成。 该解决方案的大小和能效都较为高效,但它还可以改进吗?如本系列文章所述,优化的第一步是量化AD9213的灵敏度——即实际设置PDN输出噪声的限值,以免导致ADC性能大幅下降。在这里,我们将介绍使用两个µModule稳压器的另一种替代PDN解决方案,并比较该方案与标准现成解决方案的性能。

AD9213 10 GSPS ADC需要15个不同的电源轨,这些电源轨可以分为4组:

·1 V模拟(3个电源轨)

·1 V数字(6个电源轨)

·2 V模拟(2个电源轨)

·2 V数字(4个电源轨)

图7.集成在现成评估板上的AD9213高速DAC的标准PDN。

分析:噪声要求

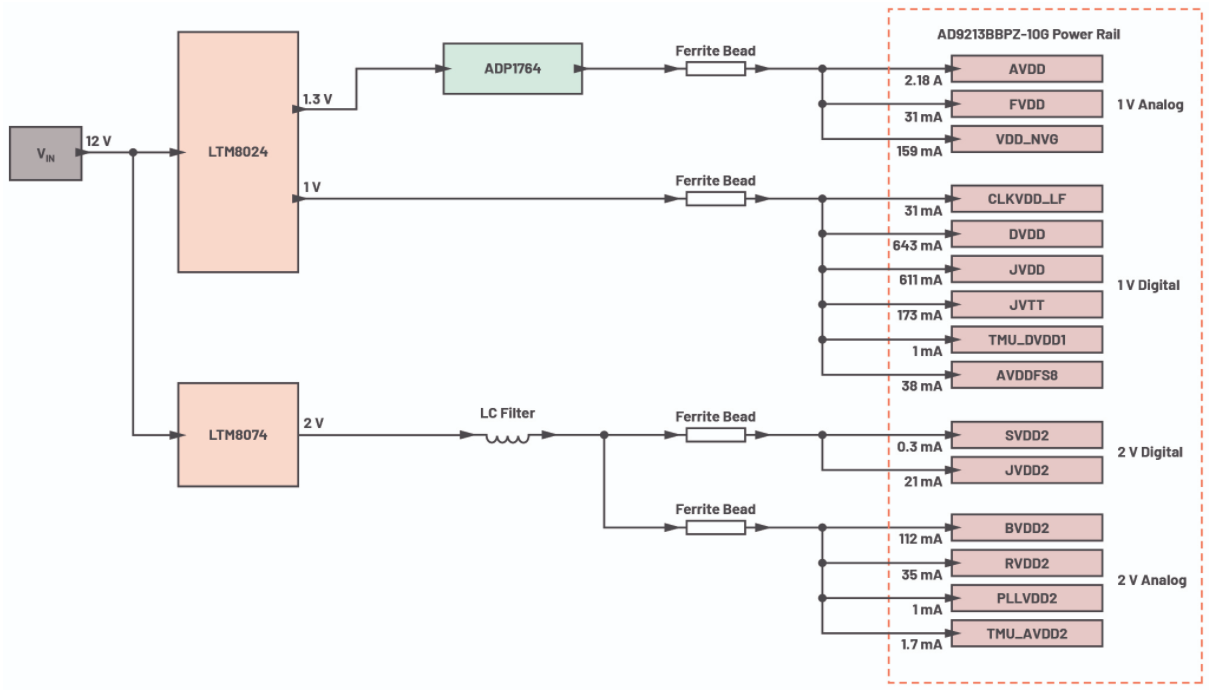

我们探讨的优化解决方案使用两个µModule稳压器(LTM8024和LTM8074)和一个LDO后置稳压器取代LTM4644-1 µModule四通道开关和两个线性稳压器。

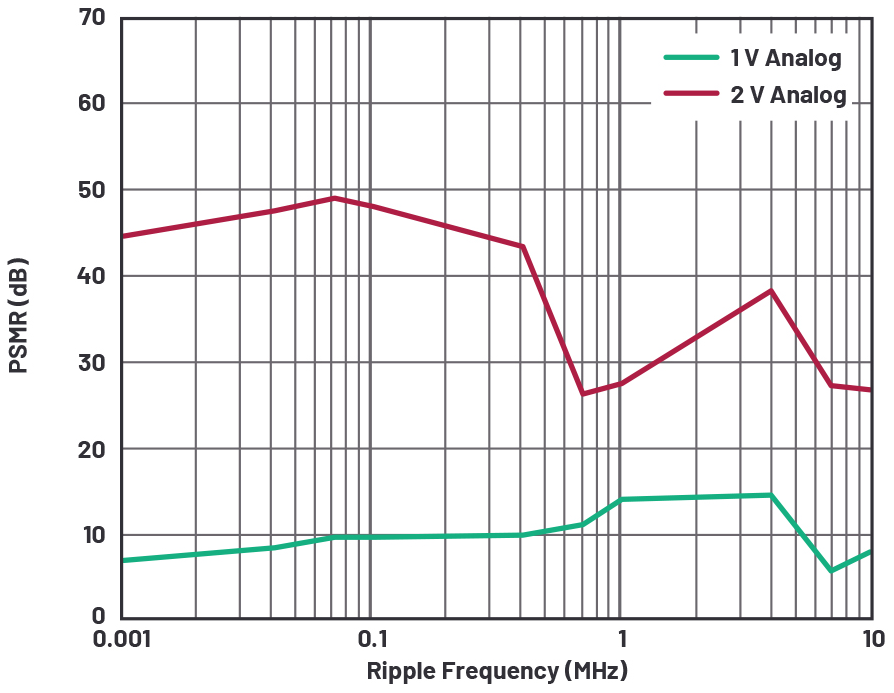

图8.在2.6 GHz载波频率下,AD9213高速ADC的1 V模拟电源轨和2 V模拟电源轨的PSMR。

图8显示在2.6 GHz载波频率下,AD9213的1 V模拟电源轨和2 V模拟电源轨的PSMR结果。1 V模拟电源轨的PSMR比2 V模拟电源轨更低,所以它更加敏感。

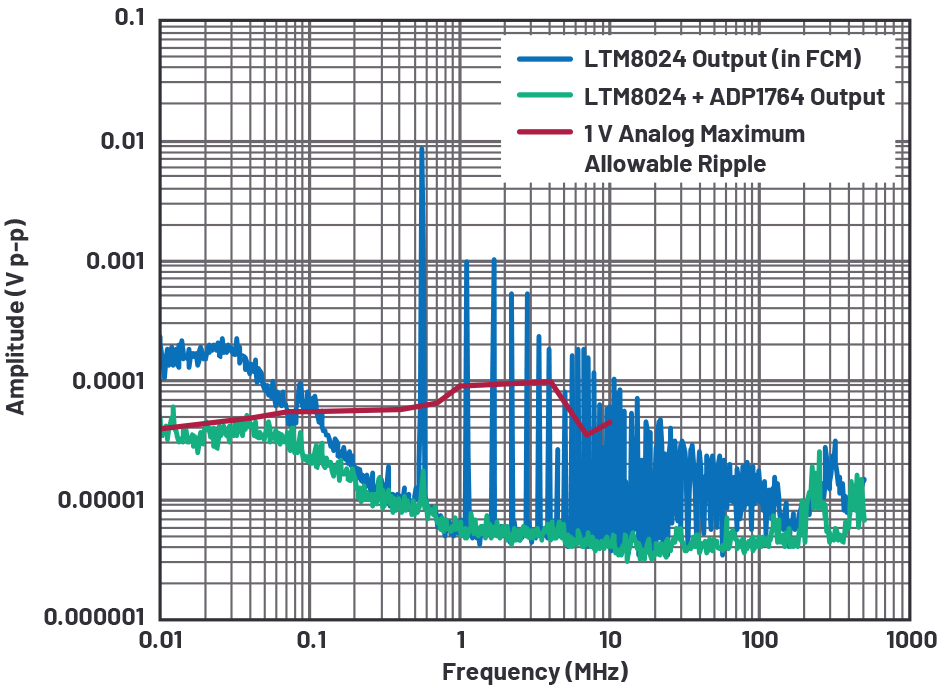

图9显示LTM8024(带和不带LDO稳压器)在强制连续模式(FCM)下的频谱输出。图中还显示最大允许电压纹波阈值的叠加不会在AD9213输出频谱的–98 dBFS本底噪声中产生杂散。直接为1 V模拟电源轨供电时,LTM8024输出中未经滤波的1/f噪声和基波开关杂散超过了最大允许纹波阈值。

为LTM8024添加 ADP1764 LDO后置稳压器可将1/f噪声、基本开关纹波及其谐波降低至最大允许纹波阈值以下,如图9所示。 需要在线性稳压器输入端提供一些裕量电压。在本例中,从LTM8024输出1.3 V至后置稳压器的输入。这个300 mV符合LDO稳压器的推荐裕量电压规格,同时能够最大限度降低其功率损耗;比标准解决方案使用的500 mV更为合适。

图9.LTM8024频谱输出与1 V模拟电源轨的最大允许纹波阈值之间的关系。

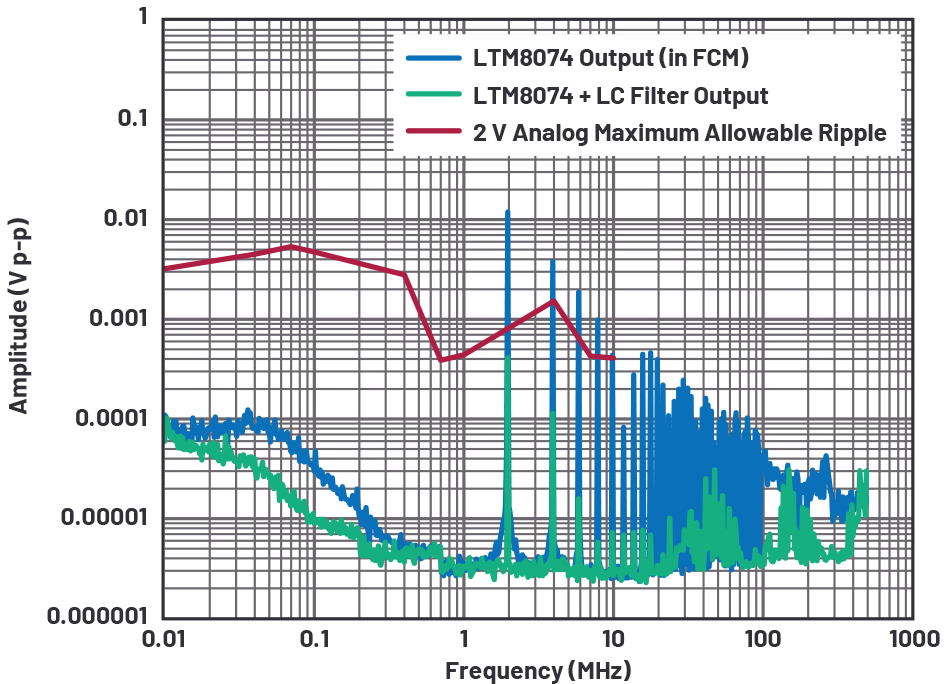

对于2 V电源轨:图10显示LTM8074 µModule稳压器(带和不带LC滤波器)在强制连续模式下的频谱输出。图中也显示了最大允许电压纹波阈值。此阈值代表电源纹波电平,当超过该值时,DAC载波信号中的边带杂散将出现在AD9213输出频谱的–98 dBFS本底噪声上方。这里,与1 V模拟电源轨类似,直接为2 V模拟电源轨供电时,稳压器开关杂散会超过最大允许纹波阈值。但是,不需要LDO稳压器,而是由LTM8074输出端的LC滤波器将开关杂散降低至最大允许纹波阈值以下。

图10.LTM8074频谱输出与2 V模拟电源轨的最大允许纹波阈值之间的关系。

结果:优化PDN

图11显示根据电源灵敏度评估结果得到的优化配电网络。与标准解决方案一样,它使用三个功率IC;在本例中,分别是LTM8024、LTM8074和ADP1764。在该解决方案中,LTM8024 µModule稳压器VOUT1由ADP1764进行后置调节,以便为相对敏感的1 V模拟电源轨供电。1 V数字电源轨直接由LTM8024的VOUT2供电。与AD9175 DAC类似,AD9213的数字电源轨对电源噪声不太敏感,因此可以直接为这些电源轨供电,并且不会降低DAC动态性能。带有LC滤波器的LTM8074为2 V模拟和2 V数字电源轨供电。

图11.AD9213高速ADC的优化PDN。

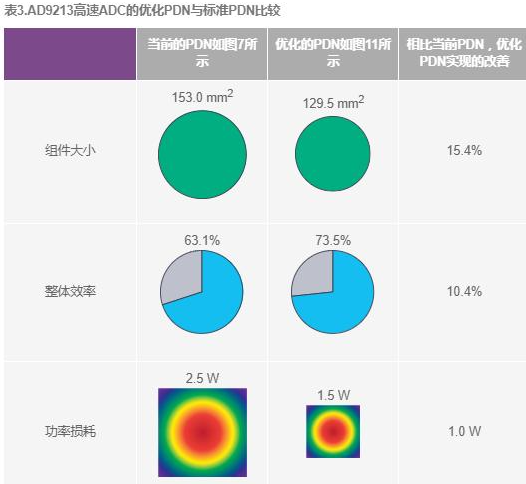

表3比较了优化PDN与现成标准PDN的性能。如图7所示,标准PDN使用一个四通道降压开关和两个LDO稳压器。组件大小减小15.4%,效率从63.1%提高到73.5%,整体节能1.0 W。

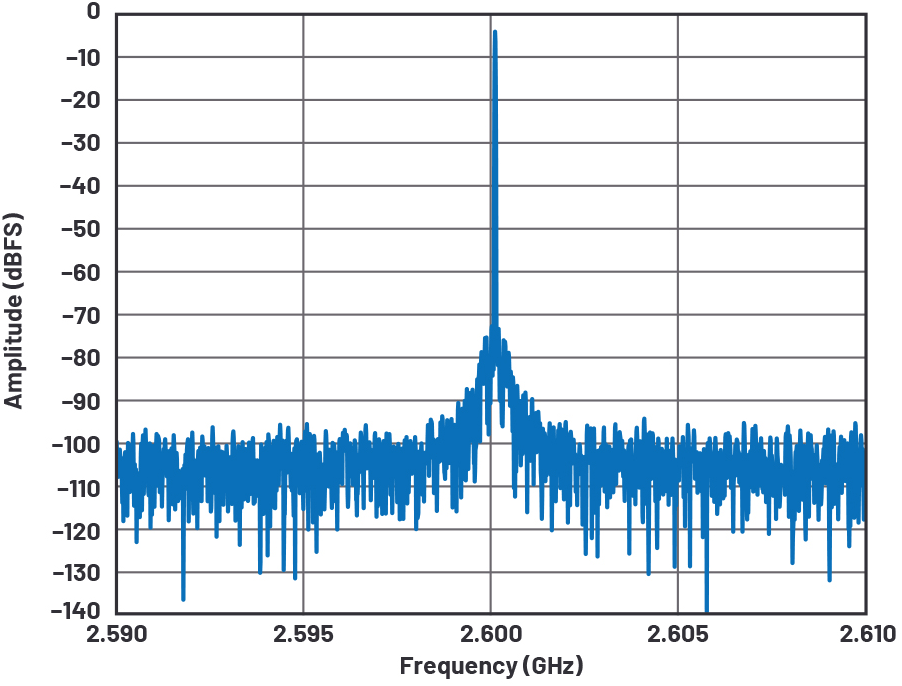

为了验证优化PDN的性能,从SFDR和SNR两个方面对AD9213进行评估,并检查载波周围边带杂散的FFT输出频谱。结果显示,SNR和SFDR的性能在数据手册给出的技术规格限值范围内,如表4所示。图12显示AD9213的FFT输出频谱,其载波频率很干净,没有可见的边带杂散。

图12.使用图11中的优化PDN时,AD9213的FFT频谱(2.6 GHz、–1 dBFS载波)。

结论

高性能数据转换器的现成评估板中包含配电网络,旨在满足这些信号处理IC的噪声要求。即使这些评估板在设计时经过了仔细考量,配电网络仍有改进的空间。本文研究了两种PDN:一种适用于高速DAC,一种适用于高速ADC。与标准PDN相比,我们的优化方案在空间要求、效率,尤其是重要的热性能方面都有所改进。通过使用替代设计,或当前不可用的器件,可以进一步改善某些参数。请继续关注“电源系统优化”系列文章,包括RF收发器的PDN优化。

参考威廉希尔官方网站

1 Patrick Errgy Pasaquian and Pablo Perez, Jr。“优化信号链的电源系统 — 第1部分: 多少电源噪声可以接受?” 模拟对话,第55卷第1期,2021年3月。

Delos, Peter。“电源调制比揭秘:PSMR与PSRR有何不同?” ADI公司,2018年12月。

Delos、Peter和Jarrett Liner。“改进的DAC相位噪声测量支持超低相位噪声DDS应用” 模拟对话,第51卷第3期,2017年8月。

“数据转换基本指南” ADI公司。

Umesh Jayamohan。 “为GSPS或RF采样ADC供电:开关与LDO” ,ADI公司,2015年11月。

Limjoco、Aldrick、Patrick Errgy Pasaquian和Jefferson Eco。 “Silent Switcher µModule稳压器为GSPS采样ADC提供低噪声供电,并节省一半空间” ADI公司,2018年10月。

Eco, Jefferson和Aldrick Limjoco。“铁氧体磁珠揭秘” 模拟对话,第50卷第1期,2016年2月。

Umesh Jayamohan。 “高速ADC电源域非常见问题解答” 模拟对话,第52卷第2期,2018年5月。

作者

John Martin Dela Cruz

John Martin Dela Cruz于2020年10月加入ADI公司,担任电源应用工程师。他主要负责航空航天和防务(ADEF)电源系统。他毕业于菲律宾大学(位于菲律宾奎松市迪里曼),获电子工程学士学位。

Patrick Errgy Pasaquian

Patrick Errgy Pasaquian已在ADI公司工作七年。他于2014年加入ADI,目前担任航空航天和防务(ADEF)电源系统部电源应用工程师。他曾担任过应用开发、设计评估、ADEF信号链连接电源和EngineerZone及Who’s who的客户支持等工程职务。他撰写过多篇论文并在ADI综合技术大会(GTC)、亚洲技术研讨会(ATS)和ADI菲律宾技术研讨会(ADTS)上展示了多个项目。他毕业于菲律宾伊洛里奥市菲律宾中部大学,获电子工程学士学位。

-

使用高速转换器时,有哪些重要的PCB布局布线规则?(第1部分)2018-10-30 0

-

使用高速转换器时,有哪些重要的PCB布局布线规则?(第2部分)2018-10-30 0

-

使用高速转换器时,有哪些重要的PCB布局布线规则?(第3部分)2018-10-30 0

-

高速转换器如何简化RF信号链?2018-10-31 0

-

电源设计#6 高频谐振转换器设计注意事项,第2部分2020-08-02 0

-

电源系统优化——深入解读优化高速数据转换器的配电网络2021-07-17 0

-

混合信号系统接地揭秘之第二部分2013-08-26 1698

-

电压基准如何影响ADC性能,第2部分2018-05-15 1088

-

优化信号链的电源系统 — 第3部分:RF收发器2021-12-06 2983

-

如何优化信号链的电源系统2022-01-21 2088

-

信号链电源系统优化方案2022-02-07 2098

-

DC/DC转换器的高密度印刷威廉希尔官方网站 板(PCB)布局,第2部分2022-11-03 416

-

基于热敏电阻的温度检测系统—第1部分:设计挑战和威廉希尔官方网站 配置2023-06-13 905

-

电源设计方法-第2部分2024-09-06 142

全部0条评论

快来发表一下你的评论吧 !