一文解析Vivado的三种封装IP的方式

描述

Vivado提供了三种封装IP的方式:(1)将当前工程封装为IP;(2)将当前工程中的BD(IPI 设计)封装为IP;(3)将指定的文件目录封装为IP。

IP Packager支持的输入文件HDL综合文件;HDL仿真文件;说明文档;HDL测试平台;例子工程;约束文件;驱动;GUI定制文件;BD文件可以看到这里没有.dcp文件,所以设计中如果包含.dcp文件,那么是无法封装为IP的。

IP Packager输出文件component.xml文件;用于定制IP界面的.tcl文件(位于封装IP指定目录下的xgui文件夹下);其他在封装IP时用户指定包含的文件。

IP Packager对顶层文件的要求IP Packager要求设计顶层必须是VHDL或Verilog文件。如果当前设计顶层为SystemVerilog,要先将其封装为Verilog或VHDL文件。 IP Packager对约束的要求IP Packager支持三种约束文件:

(1)用于综合和布局布线阶段的.xdc;

(2)仅用于布局布线阶段的.xdc;

(3)仅用于OOC(Out-of-context)综合的.xdc 默认情形下,。

创建工程后调用IP,然后对IP采用OOC的综合方式,此时就会用到仅用于OOC综合的.xdc。在这个约束文件里,通常会包含时钟周期约束(create_clock创建的约束)。建议在封装IP时,要提供此约束文件。可将文件以“xx_ooc.xdc”的方式命名,同时设置其USED_IN的属性值为out_of_context。其实,Vivado IPCatalog自带的IP在生成时都会看到一个《ip_name》_ooc.xdc的约束文件。

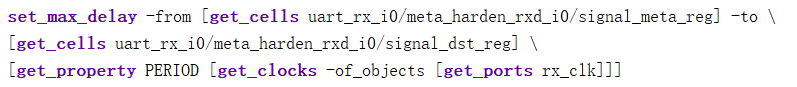

如果设计中有其他约束依赖于create_clock创建的约束,如下图所示,set_max_delay创建约束时需要用到时钟周期PERIOD,此时应将这类约束单独写在一个.xdc文件里,并将其PROCESSING_ORDER值设置为LATE。这将表明该约束文件里的约束依赖于外部约束,其实就是顶层约束文件。

编辑:jq

-

三种SMA接口pcb封装2016-01-25 0

-

基于 FPGA vivado 2017.2 的74系列IP封装2017-12-20 0

-

Vivado IP核锁定的解决办法分享2021-01-08 0

-

vivado有哪几种常用IP核?如何去调用它们2021-07-29 0

-

STM32的三种开发方式分享2021-12-01 0

-

了解Vivado中IP核的原理与应用2017-11-15 9145

-

关于Vivado中三种操作Debug的方式2020-11-11 10857

-

伺服电机的三种控制方式该如何应用2020-12-14 5358

-

函数宏的三种封装方式2020-12-22 3680

-

如何应用伺服电机的三种控制方式2021-01-22 1737

-

关于Vivado三种常用IP核的调用详细解析2021-04-27 24127

-

伺服电机的三种控制方式2022-08-17 7107

-

FPGA应用之vivado三种常用IP核的调用2023-02-02 3541

-

Redis实现限流的三种方式分享2023-02-22 1079

-

继电保护的三种状态解析2023-09-27 2831

全部0条评论

快来发表一下你的评论吧 !