瑞苏盈科Zynq UltraScale+ MPSoC开发套件助您大幅缩短FPGA设计导入时间

可编程逻辑

描述

FPGA技术对于许多应用来说是一种可行的选择,并提供了很多潜力,但许多人认为入门门槛很高,编程非常复杂和费力。然而,得益于Enclustra瑞苏盈科的FPGA和SoC核心板模块,使用FPGA技术从来没有像现在这样容易,也因此更有吸引力。使用Enclustra设计套件,基于工业级核心板模块的开发可以即刻开始,有助于缩短产品上市时间,并将特定产品的开发成本和风险最小化。

得益于Enclustra的FPGA和SoC模块,使用FPGA技术从来没有像现在这样容易。

FPGA正在征服越来越多的应用领域,考虑到其巨大的并行性能、灵活性和可扩展性,这不足为奇。从简单的接口设备到集成ARM处理器和千兆接口的可编程芯片系统开发——FPGA的可能性几乎是无限的。使用标准FPGA或SoC模块(无论是基于Intel或Xilinx的FPGA或SoC),结合久经验证和优化的IP核,进入FPGA技术快速而容易。Enclustra打造的设计套件提供了一个现成的解决方案,可以即刻启动任何基于FPGA的项目的开发。

进入FPGA技术的世界比你想象的要容易

FPGA特有的技术复杂性可以用强大的标准FPGA或SoC核心板模块封装,这使硬件设计甚至比使用传统的微控制器或DSP要简单得多。对于中小批量产品,使用FPGA或SoC核心板模块特别有优势;对于大批量产品它也值得考虑——不仅仅是在原型开发过程中。

不要第二次发明轮子

采用FPGA和SoC核心板模块做底板相比购买芯片自行整体设计有很多优势。高产量的FPGA或SoC核心板模块现货降低了它们的成本,同时久经验证的产品保证了高可靠性。由于Enclustra不同的核心板模块Pin-to-Pin兼容,因此一个产品后续可以很容易地配备更强大的核心板模块,甚至在开发过程的后期临时更换核心板模块。由于FPGA核心板模块的高功能密度,也降低了底板的复杂性,使其开发速度更快,成本更低。

安装并开始

采用核心板模块可以显著降低上市时间和项目风险。基于Xilinx Zynq UltraScale+ MPSoC的Enclustra水星XU5是一个完整而强大的嵌入式处理系统,面积比信用卡还要小。将其插入一个针对特殊应用的底板就可以工作了。

Enclustra提供基于Intel和Xilinx的FPGA和SoC的广泛的核心板序列。标准FPGA SoC核心板(System on Module, SoM)中的一款是水星XU5,它将Xilinx Zynq UltraScale+ MPSoC器件和快速DDR4 ECC SDRAM、eMMC flash、quad SPI flash、双Gigabit Ethernet PHY、双USB 3.0相结合形成了一个完整而强大的嵌入式处理系统。这个实用的嵌入式处理平台为用户提供了一个功能强大且随时可用的系统,而不必担心特定技术的细节。支持的操作系统为Linux和VxWorks(Wind River Helix Virtualization Platform)。该模块有宽温级和工业级型号,由单个5~15V电源供电,这进一步简化了底板的开发。该核心板甚至可以为底板上的威廉希尔官方网站 供电,最大限度地减少对电源转换器的需求。

利用开发套件即刻开始

这款Enclustra开发套件包含您开始开发需要的一切,包括2个视觉AI Demo。

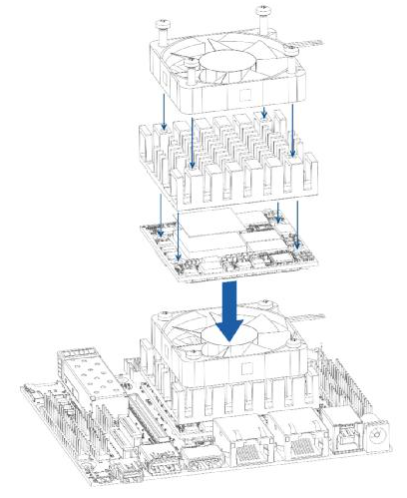

为了进一步缩短基于 Xilinx Zynq UltraScale+ MPSoC的任何应用的开发时间,Enclustra提供2款开发套件,基于水星XU5和火星XU3。这两款开发套件可以即刻运行视觉AI Demo,它们都包含您开始开发需要的一切:

·Xilinx SoC核心板

·底板

·USB摄像头

·散热器

·线缆及电源

·Micro SD card

广泛而详细的文档使得组装套件和编译AI Demo变得轻而易举。

包含所有资源的2个示例demo:

·AI人脸检测

·图像分类

它们基于ResNet50和Xilinx Vitis AI。要运行它们,只需要几个简单的步骤:

1.装配套件并将其连接到PC和显示器

2.打开连接到开发套件的串口

3.以root/root登陆

4.以此命令运行demo:facedetect

5.USB摄像头的实时视频显示在显示器上

通过资料了解

开发套件用户手册详细说明了如何从源代码中编译示例demo,并为您自己的项目提供了基础。为了进一步缩短上市时间,Enclustra为其产品提供广泛的设计支持和全面的生态系统,提供所有所需的硬件、软件和支持材料。详细的文档和参考设计使入门变得容易。Enclustra提供了用户手册、原理图、3D模型、PCB封装、差分I/O净长度表和基于Linux的Board Support Package (BSP)。

下列资料和软件可供用户下载:

- ✔ 开发套件快速使用手册

- ✔ 开发套件用户手册

- ✔ 核心板和底板的用户手册

- ✔ 参考设计

- ✔ PetaLinux board support package (BSP)

- ✔ 基于Buildroot的Linux BSP

- ✔ Module pin connection guidelines

- ✔ Master pinout

- ✔ Footprints

- ✔ 3D模型(STEP)

- ✔ IO净长

- ✔ 原理图

- ✔ Altium design文件(底板)

- ✔ 应用笔记

瑞苏盈科开发套件有助于缩短任何基于Xilinx Zynq UltraScale+ MPSoC 的应用的上市时间,无论是图像处理、机器视觉、测试和测量、通信或医疗:有了瑞苏盈科核心板,开发时间可以减半。所以,使用瑞苏盈科开发套件即刻开始您的项目吧!

IP方案使项目开发更高效

DSP系统,仅需几次点击

通用DSP库为最常见的数字信号处理组件提供高效的FPGA实现,如FIR和CIC滤波器、混频器、CORDIC和函数逼近。它还提供将DSP系统连接在一起所需的必要的胶合逻辑,如多路复用器、流分配器、缓冲区、TDM并行转换器和定点格式转换器。

流缓冲控制器简化数据传输

Enclustra瑞苏盈科的FPGA Manager IP解决方案通过USB 3.0、千兆以太网或PCI Express实现了主机PC和FPGA之间简单而高效的数据传输。该解决方案包括一个主机软件库(DLL)和一个用于FPGA的IP核。用户应用程序通过一个简单的API与FPGA通信,该API使用隐藏底层协议复杂性的读/写命令。支持流访问和内存映射访问。

运动控制

模块化的通用驱动控制器IP核包括控制频率超过200kHz的8个轴(即电机)所需的一切:从A/D转换器接口到位置、速度和电流控制器,通过编码器或解析器的位置检测,功率级的控制逻辑。支持直流,无刷直流和2或3相步进电机。磁场定向控制可用于无刷直流电机(BLDC),支持步进电机的等步细分控制。

虚拟FIFO

流缓冲控制器IP核为FPGA而优化,并实现了一个多功能的流到内存映射DMA桥,最多有16个独立的流。IP核允许外部内存设备中的数据缓冲,以提供高达4兆字节内存大小的虚拟FIFO能力。它为每个写和读数据流提供了一个AMBA AXI4-Stream接口。一个公共内存映射主接口(AXI4或Avalon)可用于访问外部内存设备。

IP核高度可配置,如每个流的操作模式、缓冲区大小和缓冲区地址。配置是通过内存映射的从接口完成的,可以通过嵌入式CPU、FPGA管理程序或VHDL中的特定的应用程序流配置控制器完成。

-

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器2021-01-07 0

-

ZYNQ Ultrascale+ MPSOC FPGA教程2021-02-02 0

-

Zynq UltraScale+ MPSoC的视频处理功能演示2018-11-29 3194

-

Zynq UltraScale+ MPSoC的发售消息2018-11-27 3601

-

Zynq UltraScale+ MPSoC的ZCU102开发套件的开发流程2018-11-27 4877

-

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?2021-02-23 1344

-

米尔电子zynq ultrascale+ mpsoc底板外设资源清单分享2022-01-07 616

-

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计2022-11-02 1591

-

瑞苏盈科Xilinx Zynq UltraScale+ MPSoC无人机控制器2022-04-08 1012

-

Zynq UltraScale+ MPSoC:软件开发者指南2023-09-14 343

-

Zynq UltraScale+ MPSoC中的隔离方法2023-09-13 372

-

Zynq UltraScale+ MPSoC的隔离设计示例2023-09-13 298

-

Zynq UltraScale+ MPSoC验证数据手册2023-09-15 328

全部0条评论

快来发表一下你的评论吧 !