Aurora 8B/10B IP核(二)—时钟、复位与状态指示

电子说

描述

写在前面

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?黑盒子就是你看不到里面的东西,你只能看到外面的接口。也就是说IP是某类可以不了解内部构造,仅仅需要对对外接口操作即可以使用的某类特定功能模块。

封装成黑盒子的好处是显而易见的-----你无需对复杂的内部结构了如执掌,只要能做到如何使用即可。可能有人会说了:那这岂不是不符合我们从小学习的“知其然,知其所以然”?不好意思,你是工程师,你不是科学家。老板只关心你把东西做出来、做好,不会关心这个东西你到底懂不懂。

说了这么多的意思就是。Aurora IP核这个东西我们会用就行了,不用纠结它具体是怎么实现的(当然知道肯定更好,无非就是个时间性价比的问题)。那么具体到一个FPGA IP类的黑盒子,我们需要了解哪些对外接口才能把它给用起来呢?无非就是三类:

- 时钟:对于一个系统,时钟架构是必不可少的,根据其复杂程度,时钟数量、种类也会不同

- 复位:一个稳健的系统,各类复位信号也是不可缺少的(要能把IP初始化成功)

- 指示:辅以数个指示信号,可以实现更好的操作、调试等交互功能

1、时钟

时钟看手册好像很多,实际上真的与我们密切相关的无非就是4个。

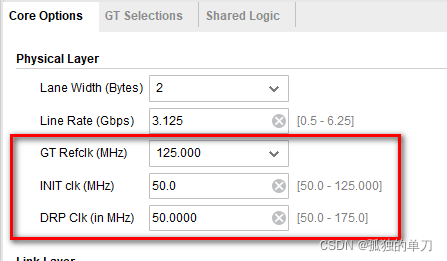

首先我们打开IP定制界面的第一页Core Options,可以看到3个时钟:

- GT Refclk :Aurora IP核是基于GT作为物理层实现的,所以时钟GT Refclk就是GT的参考时钟。GT的时钟参考只能使用外部的差分时钟,所以具体的值取决你板卡的硬件设计。默认125Mhz。

- INIT CLK :初始化阶段的时钟 ,在上电初始化阶段,可以使用该时钟来驱动一些逻辑。默认值:50Mhz。

- DRP CLK : DRP时钟,动态重配置,一般没用,默认值:50Mhz(通常一个内部模块需要进行配置,使用两种方法:端口控制和配置参数控制。一个常见的应用就是线速率切换。这时候就需要利用DRP端口来调整部分参数的值,然后复位GTX,使GTX工作在不同的线速率下。)。

上面这三个时钟,是IP核工作所需要的时钟,也是我们需要提供给IP核的。此外,还有一个时钟是IP核提供给我们的:user_clk。这个时钟,是IP核根据设置的线速率及Lane的位宽计算出来的用户时钟,用户需要传输的数据必须是该时钟域下的数据,否则会存在亚稳态风险。关于user_clk值的计算我们在下一章节再讨论。

基本就能总结了:1、GT Refclk的值根据对应硬件设计的来;INIT CLK 和DRP CLK可以用PLL或者MMCM生成;3、user_clk是用户时钟域,我们的数据收发接口应该工作在此时钟域下。

2、复位

复位信号一定要好好了解,不然你的IP为什么起不来你都不知道咋回事!

复位信号用于将Aurora 8B/10B核心设置为一个已知的启动状态。在复位时,IP核停止任何当前操作并重新初始化一个新通道。在双工模块上,复位信号复位通道的TX和RX两侧。

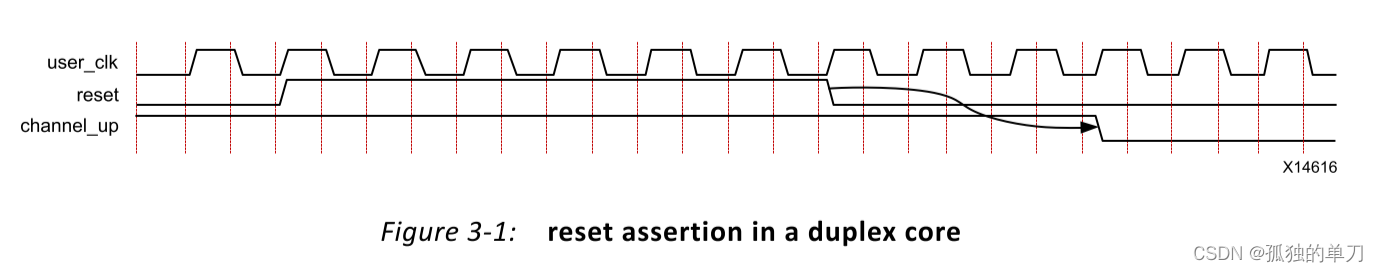

复位案例1:双工模式下的reset复位

复位信号reset需要至少维持6个时钟周期,然后3个周期后,channel_up信号被拉低,表示传输通道建立失效

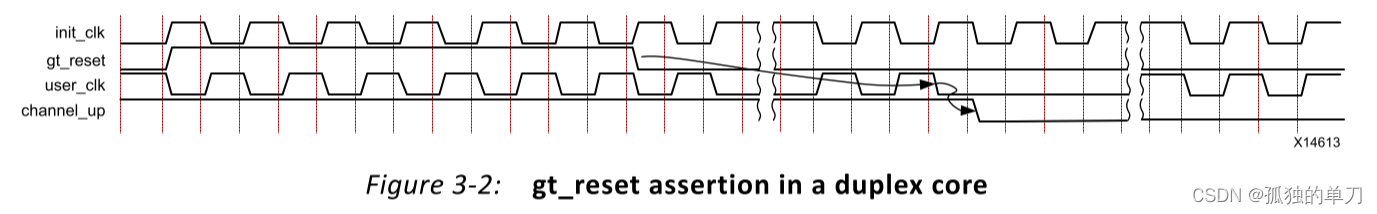

复位案例2:双工模式下的gt_reset复位

复位信号gt_reset需要至少维持6个时钟周期,然后一段时间后,user_clk也会失效(这是因为user_clk的时钟来源是GT,gt_reset复位会从最底层的物理层复位),随后channel_up信号被拉低,表示传输通道建立失效

单工模式的复位步骤就不讲了,请参考手册。

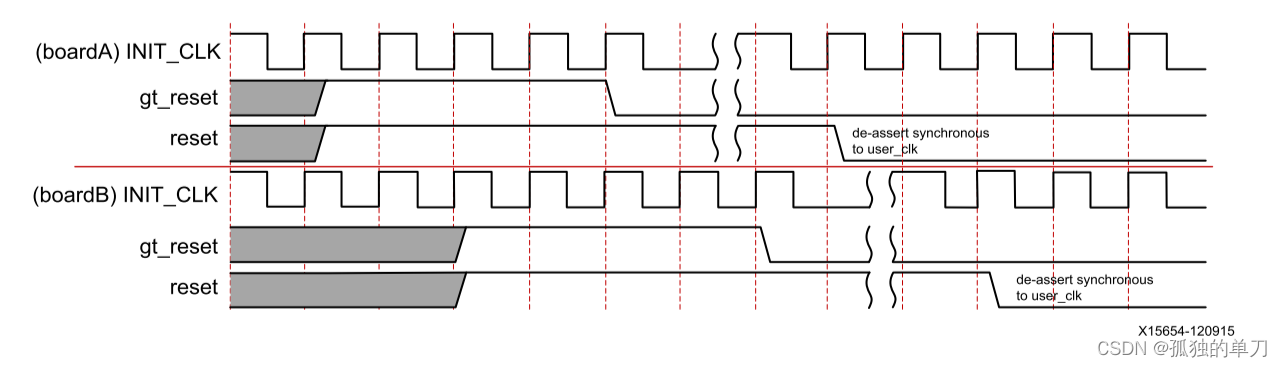

双工模式下的上电时序

双工模式下,给FPGA上电时,gt_reset和reset信号都必须保持为高电平,与此同时GT的参考时钟gt_clk和初始化时钟init_clk都必须保持稳定。

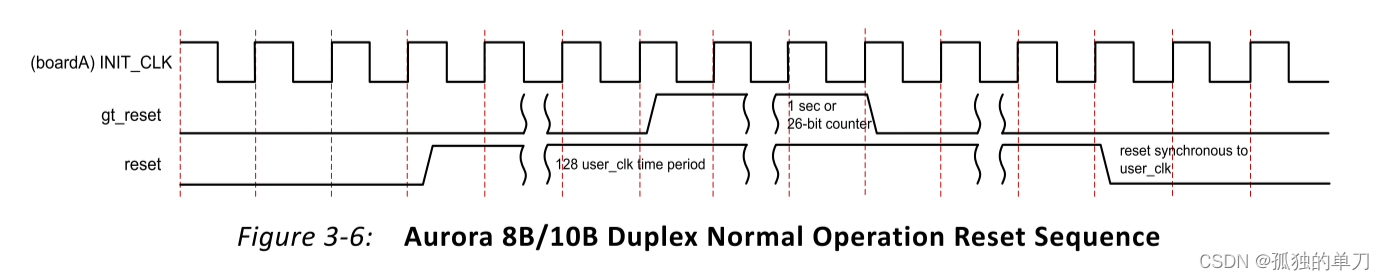

双工模式下的正常操作复位时序

1. 在gt_reset断言之前,reset信号必须稳定保持128个user_clk时钟周期的断言

2. gt_reset断言保持一段时间(图中所示为1s)

3. 在gt_reset取消断言一段时间后,reset取消断言

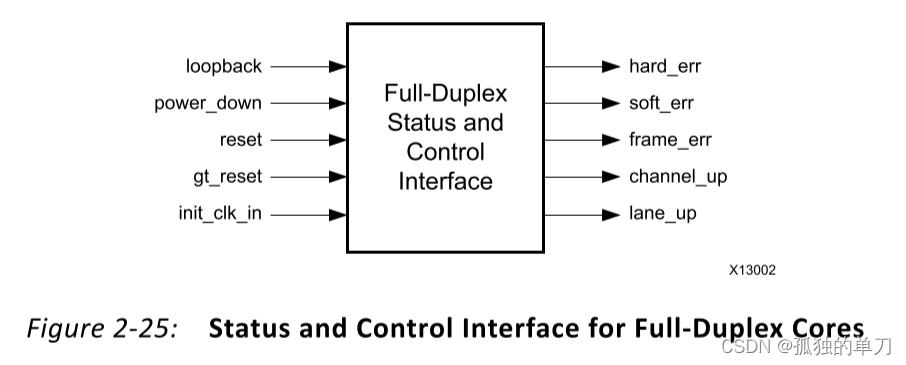

3、状态指示

Aurora IP还提供了一系列的指示接口出来,方便我们进行调试:

- loopback:回环模式,实际使用一般接到0

- power down:高电平有效。当其为高时,GT会进入非工作、低功耗的模式(类似睡眠模式)。我们使用的时候一般直接拉低。

- lane_up:当对应的Lane初始化完成后,会断言对应的lane_up

- channel_up:当Auroa 8b/10b 初始化完成后,并且当前已经可以进行数据的传输时,会断言该信号

- hard_err:错误表征应信号,主要是硬件类错误

- soft_err:错误表征应信号,主要是软件类错误

- frame_err:错误表征应信号,主要是帧类错误

4、其他

其他

除了上述部分外,还有一些不太常用的功能(自己看手册吧):

- 流控:Flow Control(Native Flow Control、User Flow Control)

- 加扰/解扰:Scrambler/Descrambler

- 循环冗余校验:Cyclic Redundancy Check,CRC

预告

下一节我们再来一起学习下Aurora IP核的example design(两种接口一起)。

参考

Aurora 8B/10B Protocol Specification

Aurora 8B/10B v11.1 LogiCORE IP Product Guide

审核编辑:符乾江

-

8b10b编码verilog实现2024-03-26 0

-

Aurora 8b/10b IP核问题2015-03-09 0

-

8b/10b编解码的控制字问题2019-01-02 0

-

收发器向导中启用8b/10b编码器的方法是什么?2020-08-04 0

-

用于26Km光缆的Aurora IP v11.0通道上行/上行故障的解决办法?2020-08-06 0

-

如何使用Aurora 8B / 10B建立仅传输?2020-08-14 0

-

怎么禁用Aurora IP Core 8B / 10B中的时钟补偿功能?2020-08-18 0

-

高速接口8B/10B的作用?2022-01-18 0

-

基于FPGA的8B/10B编解码设计2011-05-26 3841

-

USB3.0中8b/10b编解码器的设计2011-11-30 3267

-

基于PRBS的8B/10B编码器误码率为0设计2017-11-06 1775

-

基于Virtex-6 的Aurora 8B/10B,PCIe2.0,SRIO 2.0三种串行通信协议分析2017-11-18 12231

-

高速串行通信常用的编码方式-8b/10b编码/解码解析2021-09-26 8905

-

Aurora 8B/10B IP核(一)—Aurora概述及数据接口2022-02-16 8306

-

一文详解8b/10b编码2022-11-12 14157

全部0条评论

快来发表一下你的评论吧 !