电荷积分放大器AD8488简介及工作原理

电子说

描述

XRAY项目--电荷积分放大器AD8488介绍

一、项目背景

明德扬(MDY)为中科院某所研制一款X射线采集和处理设备,该设备采用了AD8488和AD9244两款芯片进行X射线的采集,采用FPGA进行处理,并通过网口上送至上位机处理。

本文介绍了AD8488和AD9244的原理,下一篇文章将介绍X射线采集中遇到的问题,希望能对大家有所帮助。明德扬专注于FPGA方面的项目研发以及相关元器件销售,有相关需求的,可联系我们。

二、AD8488简介

AD8488是一款128通道模拟前端,为高性能数字X射线系统而设计。它的模拟通道由一个积分器和增益可选的单端转低阻抗差分输出组成。该模拟通道将X射线或光电二极管检波器收集的电荷转换成电压信号。通道由CMOS晶体管组成,这些晶体管采用典型高输入阻抗的CMOS门。该设备的积分器采用一系列可选电容值,产生与电荷有关的电压,可适应广泛的输入电荷值。单端输入转差分输出电压放大器位于积分器之后,在这里偏移和低频噪声电压从输入电压中减去。一条128:1通道差分MUX位于缓冲器之后,驱动模拟输出缓冲。同时还提供开关驱动器和某些数字计时功能;这些功能全部集成在255引脚BGA基板上。全部128通道的电荷转换是同步进行的,之后便采用7位地址编码生成顺序电压输出读数。一共两次序列,对全部128通道进行采样。逻辑控制输入CS_A和CS_B分别选择通道地址的下限和上限64模块。

三、电荷积分放大器

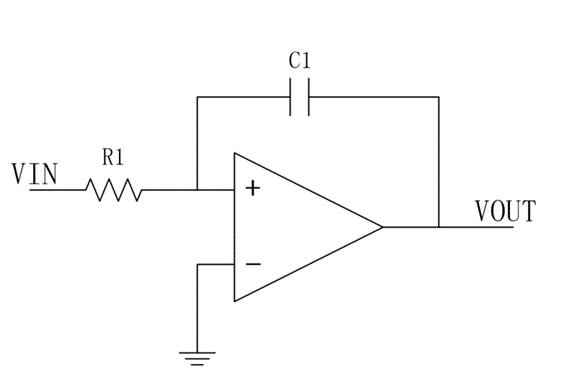

图1为运放积分放大器的威廉希尔官方网站 图

图1:理想积分放大器威廉希尔官方网站 图

根据运放虚短可知,反向端与同相端电压相等,又由虚断可知,通过R1的电流与通过C1的电流相等。通过R1的电流为:

由此可得,运放的输出电压等于对输入电压在时间上的积分。若输入端为电荷采集装置的话,那么运放的输出与输入端的电荷量成正比。两部分组合起来就是电荷积分放大器。

四、AD8488工作原理

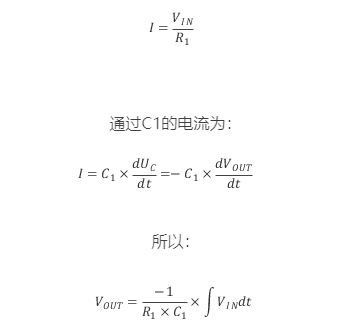

AD8488威廉希尔官方网站 结构如图2所示:

图2:AD8488威廉希尔官方网站 结构图

如图所示,AD8488主要由四部分构成。分别为前置电荷量转换器、差分输出选择器、输出缓冲器和时序/控制部分。

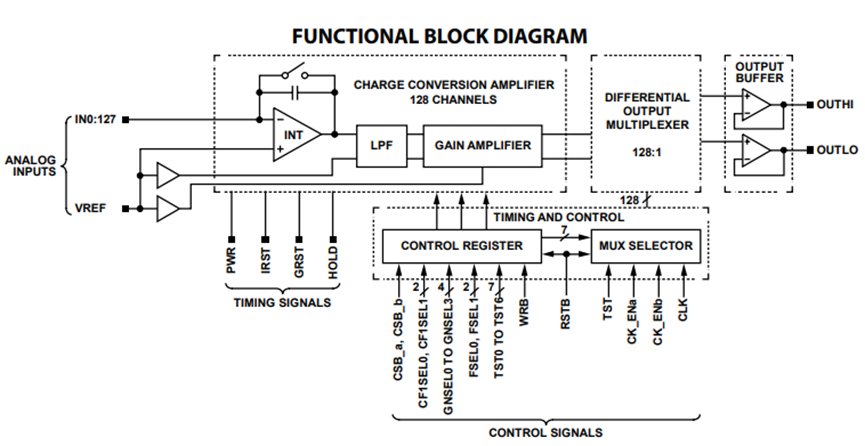

前置电荷量转换器为128通道电荷积分放大器,每一个通道由一个放大器,一个低通滤波器和一个二级放大器构成。威廉希尔官方网站 结构图如图3所示:

图3:电荷量转换器结构图

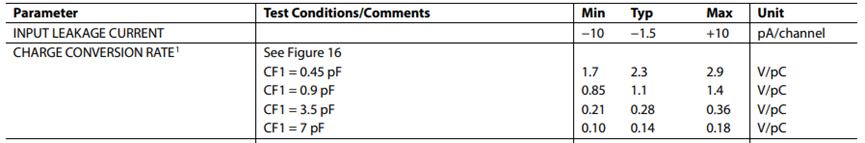

前端采集到的电荷信号通过第一级积分放大器进行转换,共有四档可选。各档位转换参数如图4所示:

图4:电荷积分放大器转换参数

这四档分别由四种不同容值的反馈电容(CF1)控制。当CF1=0.45pF时,输出典型值为2.3V/pC(单位为伏特每皮库伦,指每积分1皮库伦,输出为1V。1pC==10-12c);当CF1=1.1pF时,输出典型值为1.1V/pC,以此类推。CF1容值越大,增益越低。

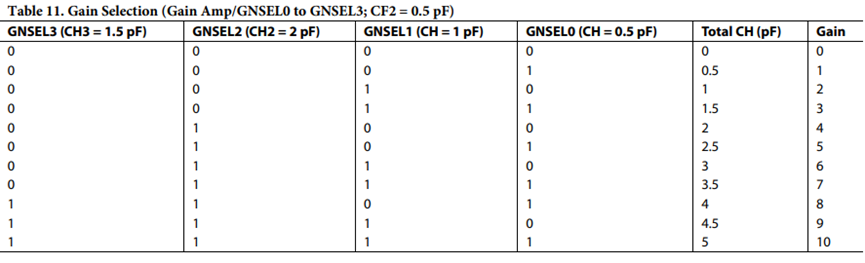

第二级低通滤波器实际上是一个保持装置,由一个电阻R1和一个电容CH构成。第一级放大器输出的电压信号通过R1给电容CH充电,以便于第二级放大器对CH进行积分放大。因此相当于一个低通滤波器。CH的参数由GNSEL[3..0]选择,参数如图5所示:

图5:CH参数选择表

注:GNSEL[3..0]寄存器只能选择CH的容值,并不代表增益。上图中所表示的增益实际上是当二级放大器的反馈电容为0.5pF是,不同的CH容值下对应的增益。

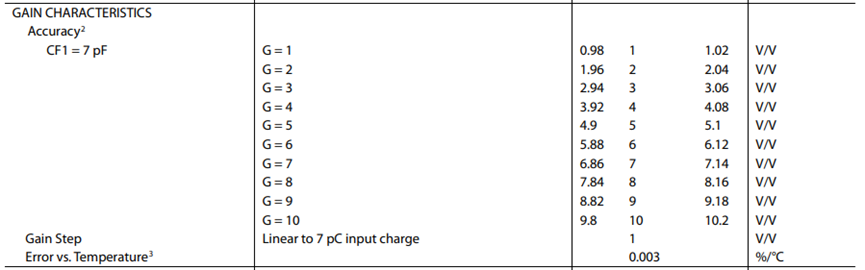

第三级放大器与第一级相同,也是一个电荷积分放大器。只不过第一级输出的电压信号是对芯片输入的电荷量的积分,然后该电压信号对第二级的CH电容进行充电,之后通过第二级放大器对CH的电荷量积分,最终输出新的电压信号,形成二次放大的效果。第二级积分放大器增益由CF2控制,共有10档,增益单位为V/V。注:因为第一级放大器已经将电荷信号转换为电压信号,因此第二级放大器的电压为伏特每伏特。增益表如图6所示:

图6:第二级积分放大器增益表

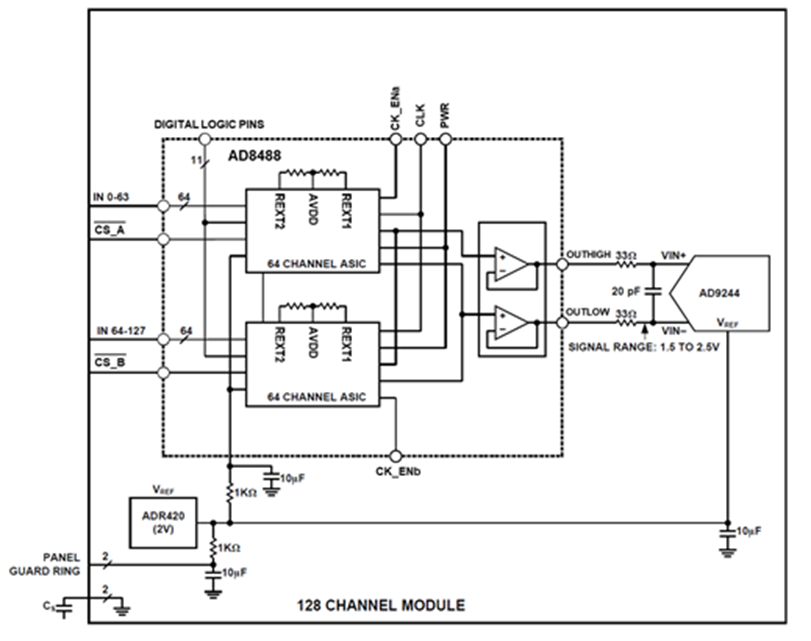

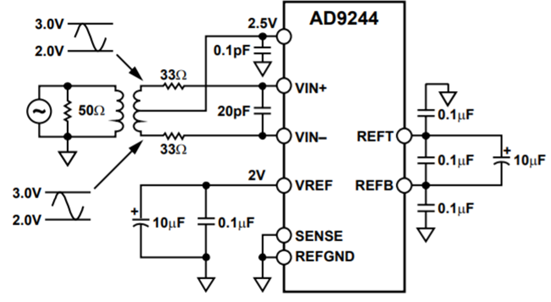

AD8488采集的信号经过两级放大后,经数据选择器选通通道后,再由一个缓冲器输出差分信号。该信号的幅度范围为1.5V至2.5V。官方推荐使用AD9244这款ADC芯片进行模拟信号转换,推荐威廉希尔官方网站 如图7所示:

图7:AD8488与AD9244连接示意图

AD8488与AD9244共用一个2.048V的电压参考。AD9244的差分输出范围为0~2.048V,偏置电压为2.5V。

五、模数转换部分

模数转换芯片选用ADI公司的AD9244,是一个14BIT,最高采样率为65MHz的高速ADC芯片。它由+5V模拟电压供电,也可以在+3.3V或+5V的数字电压下正常工作。

AD9244可专门用来处理峰峰值为1~2V的模拟小信号。它的输入信号和时钟信号都可以采用差分输入形式,以使系统获得最好的性能。14位数字输出信号可以表示为直接二进制的形式,也可以是二进制补码的形式。一位溢出表示位(OTR)可以用来输出溢出信号,将这一位信号和14位信号中的最高位用一定方式组合起来判定输入信号是上溢出还是下溢出。

VIN+,VIN-:模拟信号输入端。采用单输入形式时,在VIN+端接输入信号,VIN-端接地;采用差分形式输入模拟信号时,VIN+,VIN-分别接差分信号的两端。差分输入的形式对于高精度高速度的应用更容易获得好的效果。一般情况下,输入信号都是单路形式,因此经常采用1:1变压器或者专用差分转换芯片来实现单路信号到差分信号的转换。

CLK+,CLK-:时钟信号输入端。和VIN+、VIN-相似,输入时钟也可以采用单输入和差分两种输入形式,不过在AD9244的内部最终都会把单输入的时钟信号变为差分形式。输入时钟信号的质量对模数转换的效果有很大的影响,因此应尽量保证时钟信号的纯净和准确,并尽量避免对时钟输入信号的干扰。

DUTY:时钟稳定信号。该端接高电平时,可以在内部对外部输入时钟的占空比进行调整,以产生占空比准确为50%的时钟信号。

REFSENSE,VREF,REFGND:内部参考电压脚。这三个管脚的不同连接可以产生1V~2V的内部参考电压,在这三个管脚之间连接适当的电阻还可以随意产生1V与2V之间的任意电压参考。

REFT、REFB:ADC内部参考电压去耦管脚。这两个管脚的输出电压是AD9244内部实际的参考电压值。它们之间应该用10μF的电解电容去耦,同时应并联一个0.1μF的小电容,这样效果可能会更好。每个管脚都必须用0.1μF的电容接地。

CML,VR:AD9244内部使用的模拟偏压点,通常该端会产生大于300μA的电流,因此必须用0.1μF的电容接地以进行去耦。

OEB:输出允许管脚。AD9244有三态输出功能。如果OEB接地,那么AD9244的输出驱动器就会激活,并输出转换后的数字信号;而如果OEB接高,输出信号管脚则输出高阻态。

DB0~DB13:数据输出脚,其中DB0为最低位。

OTR:电压溢出指示管脚。当OTR输出为1时,表示输入电压超过AD所能转换的电压范围。OTR和DB0进行简单的逻辑组合可以准确地判断输入电压是上溢出还是下溢出。

DFS:输出数据形式选择管脚。当DFS接数字地时,输出数据为直接二进制形式;当DFS接数字电源时,输出数据为二进制补码形式。

本设计中的AD9244有以下几点设计要点:

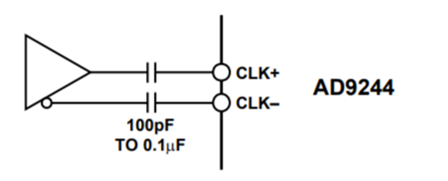

1)时钟采用差分的方式驱动。由于时钟信号和ADC的输出信号在一根排线内,ADC输出的并行数据会对时钟产生十分严重的影响,因此用差分的方式传输时钟。差分时钟在控制板上分别由FPGA和AD9517产生,在调试时做二选一,用于验证两种时钟对采样时序以及信噪比的影响。时钟与ADC的连接方式如图8所示:由于控制板产生的时钟信号为LVDS,因此在AD9244时钟输入端做交流耦合即可。

图8:AD9244差分时钟输入(交流耦合)

2)信号输入方式采用差分模式、直流耦合。AD8848的输出为差分信号,因此采用差分的形式与AD9244相连,AD9244信号输入端威廉希尔官方网站 如图9所示:同时,ADC的VREF采用外部参考电压2.048V,因此单边信号输入的范围为1Vpp,差分信号的输入范围为2Vpp。又因为供电电压为5V,因此输入共模电压为2.5V。

图9:AD9244信号输入威廉希尔官方网站 (直流耦合)

3)AD9244模拟供电电压为5.0V,数字供电电压为3.3V,这样就可以省掉电平转换器,将ADC输出信号直接与FPGA相连。参考电压与AD8488共用一个芯片,为2.048V。由于使用了外部参考电压,所以需要将SENSE脚接高。

AD9244为14位ADC,有效位数约为12BIT,因此在测试时,当差分输入正负两端相连,ADC上随机跳动的比特位应该是2bit,而输出的数值应该在8192附近跳动。当差分输入信号峰峰值为2Vpp是,ADC刚好打到满幅状态,超过这个电压,OTR为1,ADC溢出。

审核编辑:汤梓红

-

请问电荷积分放大器是对电流的积分,还是电压的积分?2024-08-19 0

-

谁有DLF-6电荷电压滤波积分放大器的工作原理的介绍资料?2016-01-02 0

-

请问有像AD8488一样的电荷放大芯片吗?2018-08-06 0

-

电荷放大芯片选型:电荷量为2.2*10-17~6.6*10-16C量级2019-01-23 0

-

XRAY项目--电荷积分放大器AD8488介绍2022-02-17 0

-

B类放大器工作原理2012-06-15 16690

-

放大器的工作原理2016-04-15 725

-

电荷放大器工作原理2018-02-12 35756

-

AD8488 128通道数字X射线模拟前端2019-02-22 475

-

Ad8488笔记:积分电荷放大器原理2022-10-21 7645

-

电荷放大器和电压放大器各有何特点2023-02-21 5137

-

运算放大器的工作原理和工作模式2023-05-11 4320

-

电压放大器与电荷放大器的区别2023-06-02 4974

-

电荷放大器的工作原理?电荷放大器输出的电压信号属于数字信号吗?2024-02-05 2682

-

电荷放大器的反馈元件是什么 电荷放大器的反馈电容怎么计算2024-02-05 1628

全部0条评论

快来发表一下你的评论吧 !