明德扬PCIE高速传输解决方案

明德扬PCIE高速传输解决方案

今日头条

描述

明德扬在PCIE高速传输方案积累了丰富的技术,传输的带宽利用率可达到90%以上,延迟可达到理论的最低延迟值。

明德扬能够根据客户的需求(需求、延迟和应用等),为客户提供定制的PCIE解决方案,欢迎您与我们联系,沟通洽谈。

下面是我司为客户定制的方案介绍,该方案已经应用到航天航空、雷达等领域,经受住客户和市场的检验。

一、 高效率传输方案

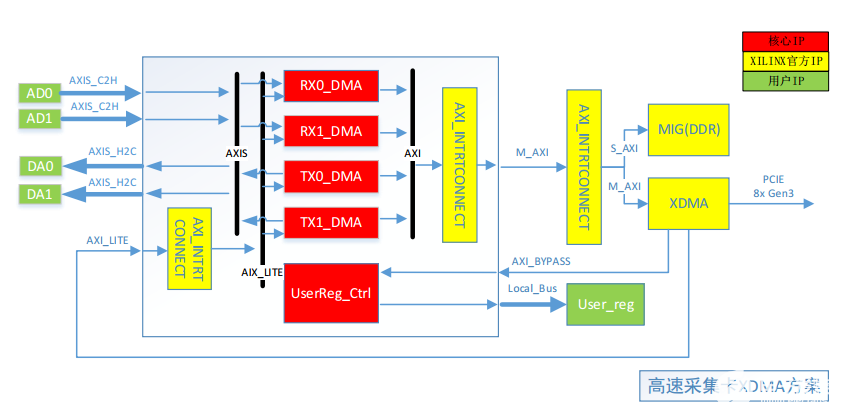

该采集方案 Demo 基于 VC709 开发板,使用 XILINX 官方 XDMA IP 核配合板载高速 DDR3,可对前端 ADC 产生的不大于 4.5GB/s 的连续或非连续数据进行实时采集,同时该采集卡具备数据发送功能,可以将用户文件或者内存中的数据写到 FPGA 的发送 FIFO 中,速率约为4.5GB/s,该采集卡具备上位机读写 FPGA 用户寄存器的功能,读写接口为 local bus 接口,方便易用。

1. 系统结构图

方案一

2. 采用此方案的某项目性能

1) 支持 4 通道 AD 数据同时上行,支持 4 通道 DA 数据同时下行;

2) PCIE 链路为 8x Gen3 时, 数据传输带宽大于 4GB/s,误码率低于 10-14;

3) 使用最新 XILINX 官方 XDMA 驱动,稳定可靠;

4) 支持 16 路用户中断;

5) 支持 XILINX 7 系列以上的全系 FPGA;

6) 5.支持 Windows/Linux 系统;

二、 低延迟采集方案

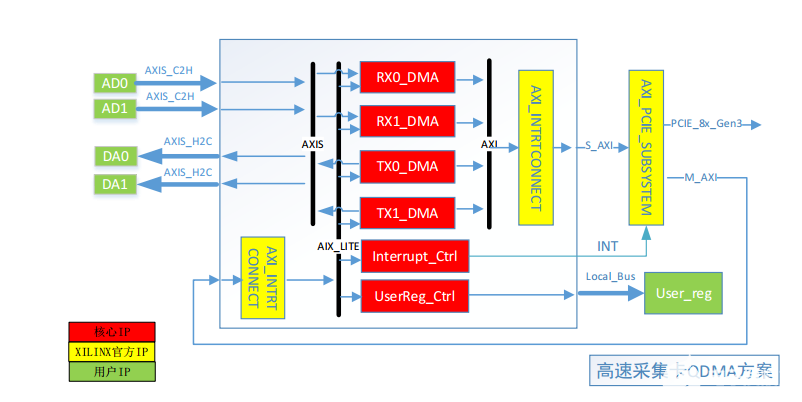

该采集方案 Demo 基于 KU115 开发板,使用自研 QDMA IP 核,无需板载 DDR, 可对前端ADC 产生的不大于 6GB/s 的连续或非连续数据进行实时采集,同时该采集卡具备数据发送功能,可以将用户文件或者内存中的数据写到 FPGA 的发送 FIFO 中,速率约为 5.5GB/s,该采集卡具备上位机读写 FPGA 用户寄存器的功能,读写接口为 local bus 接口,方便易用。

1. 结构框图

方案二

2. 采用此方案的某项目性能

1) 最高支持 8 通道 AD 数据同时上行,最高支持 8 通道 DA 数据同时下行;

2) PCIE 链路为 8x Gen3 时,数据传输带宽大于 5.7GB/s,误码率低于 10-14;

3) 驱动采用类 DPDK 架构,通过轮询模式, 内存零拷贝机制,可达到理论最低延迟。

4) 支持 16 路用户中断;

5) 支持 XILINX 7 系列以上的全系 FPGA;

6) 支持 Windows/Linux 系统;

三、 方案价格

真实的价格取决于方案的技术指标、项目周期等因素,欢迎洽谈了解。

审核编辑:汤梓红

-

明德扬FPGA知识大串讲分享2015-08-11 0

-

明德扬PCIE开发板系列XILINX-K7试用体验-第二篇2023-11-29 3305

-

明德扬分享--点拨FPGA视频2015-10-12 0

-

FPGA快速入门——明德扬科教2015-11-04 0

-

明德扬点拨FPGA课程分享---第八章 明德扬模板2015-11-27 0

-

明德扬点拨·FPGA知识大串讲2016-02-22 0

-

明德扬——点•拨FPGA课程之网络班2016-06-01 0

-

【明德扬】倾情分享海量FPGA设计技巧学习资料 转2017-03-27 0

-

明德扬FPGA设计模板分享(1)2017-04-26 0

-

明德扬至简设计法资料大全2017-07-27 0

-

明德扬FPGA设计技巧--gVim模板分享22017-11-29 0

-

插值滤波器设计-明德扬至简设计与应用FPGA2019-08-16 0

-

PCIE高速传输解决方案FPGA技术XILINX官方XDMA驱动2021-05-19 0

-

今天分享 PCIE高速接口XILINX.ISE教程2022-02-14 0

-

PCIe解决方案再掀高速传输技术浪潮2015-08-07 3699

全部0条评论

快来发表一下你的评论吧 !