首颗支持PCIE 5.0的时钟发生器CLG52147系列芯片

描述

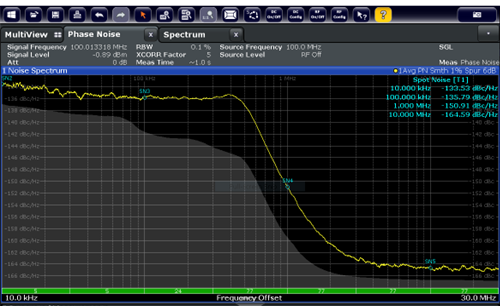

核芯互联发布首颗支持PCIE 5.0的时钟发生器CLG52147系列芯片,PCIe Gen 5 Jitter<15fs。

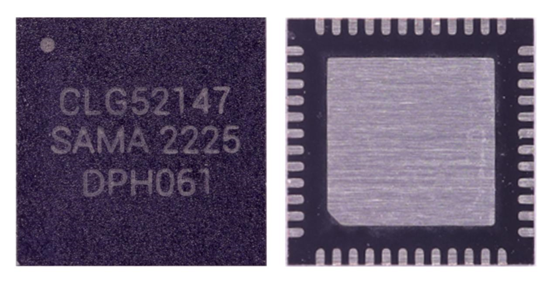

CLG52147 QFN-48封装

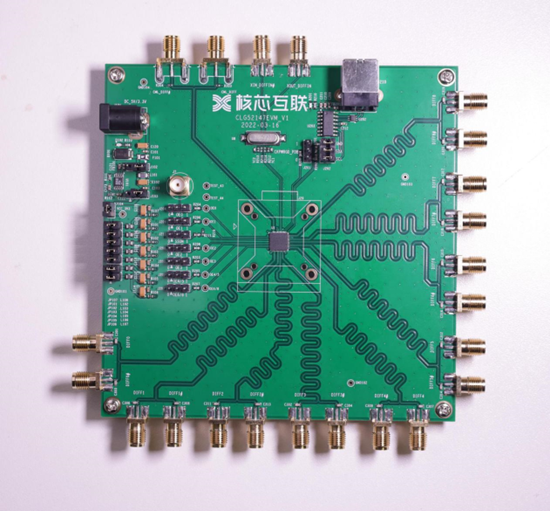

业界领先的时钟IC供应商核芯互联发布了满足新一代PCI Express(PCIe)5.0规范的时钟发生器芯片CLG52147,配合之前发布的时钟Buffer CLB53156系列,可以为用户提供完整PCIE时钟解决方案组合。

核芯互联的CLG52147系列和CLB53156系列可以提供同类型产品领先的抖动性能,具有显著的设计余量,具有出色的频率灵活性和可配置的交流电参数对信号完整性进行优化,可以工作在全工业温度范围内,满足PCI Express (PCIe) Gen 1/2/3/4/5 的时钟抖动要求,支持SSC(展频),使用推拉式 HCSL 输出端能够确保最低的功耗,同时接受威廉希尔官方网站

板空间和外部终端电阻,从而提高 BOM 整合。

基础概念

Jitter,时钟抖动,是对于同一时钟而言的, 是时钟源引起的,用来描述被测时钟与理想时钟在时域的偏差(单位为 ps RMS,皮秒均方根)。时钟抖动越小越好。

Skew,时钟偏斜,是对于多个时钟线而言的,是时钟树不平衡引起的。时钟偏斜越小越好。

频率稳定性,用来描述被测时钟频率与理想时钟频率的偏差(单位 ppm,百万分之一)。频率越稳定(ppm越小)越好。

PCIe Serdes 在时钟驱动下收发串行数据流。Serdes 所用时钟由 PHY 内的 PLL 生成,PLL 的参考时钟由外部提供或从接收数据流中恢复出来。 PCIe 协议指定标准的参考时钟为 HCSL 电平的 100 MHz 时钟,Gen1~Gen4 下要求收发端参考时钟精度在 ±300 ppm 以内,Gen5 要求频率稳定性 ±100 ppm。一颗性能优秀的参考时钟是整个PCIe系统成功的基础。

CLG52147核心指标

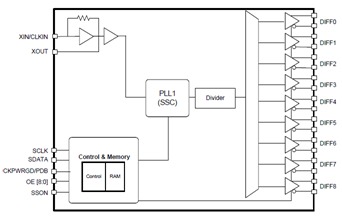

CLG52147是一颗高性能的PCIe参考时钟发生器,使用25MHz晶振或时钟输入,采用3.3V供电,符合PCIe Gen1/2/3/4/5规范,支持SRNS和Common Clock架构,支持SSC以降低EMI。CLG52147具有业界领先的抖动指标,PCIe Gen 5 Jitter < 15fs。CLG52147有9个独立的控制引脚用来开启或关断输出以降低功耗。

CLG52147采用QFN48封装,可以输出9路时钟。

CL52147已经开放样品申请,请联系对口销售或核芯互联授权代理。

审核编辑 :李倩

-

符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器2020-08-27 0

-

Silicon Labs扩展其PCIe时钟发生器和时钟缓冲器产品组合2012-02-02 1568

-

Microchip基于MEMS的时钟发生器2018-06-07 4838

-

介绍MEMS时钟发生器的特点及应用介绍2018-07-08 4217

-

Diodes推出PCIe 5.0时钟发生器与缓冲器为服务器、IPC、网络、数据中心等应用提供前向兼容性2020-03-10 1134

-

如何选择合适的时钟发生器2020-11-22 2978

-

Cypress时钟发生器的分类,它有哪些应用2022-04-22 1042

-

9ZXL1951D PCIe 时钟发生器评估板用户指南2023-03-21 213

-

核芯互联高性能通用时钟发生器CLG5908概述2023-04-23 1202

-

极景微发布超小封装PCIe5.0时钟发生器2023-02-02 1641

-

核芯互联推出支持PCIe Gen 6的时钟发生器CLG4402024-01-16 974

-

核芯互联发布高性能时钟发生器CLG4402024-01-16 1235

-

核芯互联发布时钟发生器芯片CLG0841和CLG08512024-03-29 651

-

核芯互联发布支持PCIe Gen 6的时钟发生器芯片CLG0841/CLG08512024-03-29 856

全部0条评论

快来发表一下你的评论吧 !