HPC处理器的多核架构挑战

电子说

描述

随着半导体设计团队竞相利用“超越摩尔”,新的架构选择和挑战层出不穷。以超大规模硬件为例,其中一系列工作负载——数据库分析、人工智能、微服务、视频编码和高复杂性计算算法——需要一系列处理器解决方案。性能、功耗和成本仍然至关重要,但现在架构师自己交付。没有一种“最好”的架构;处理器必须设计为最好地服务于特定类别的工作负载和价格/性能配置文件。

多核架构挑战

AWS Graviton2 有 64 个 Arm Neoverse N1 内核,它们平铺在单个芯片上的连贯网状网络中。其他设计已经扩展到多芯片,芯片之间具有缓存一致的连接。多芯片实现为进一步增长和降低不太先进工艺成本的潜力开辟了空间。虽然这些新架构选项扩展了可能性,但它们也带来了新的设计挑战。在众多选择中,哪些架构真正能够以合适的价格为合适的工作负载提供更高的吞吐量?

这里的一个问题是,应如何针对目标类应用程序的物理内存对相干网状网络中的分布式系统缓存进行分区。优化这些选择,甚至优化哪些 CPU 内核最能满足需求,都需要以周期级精度运行实际工作负载。高级模型根本不足以达到此目的。

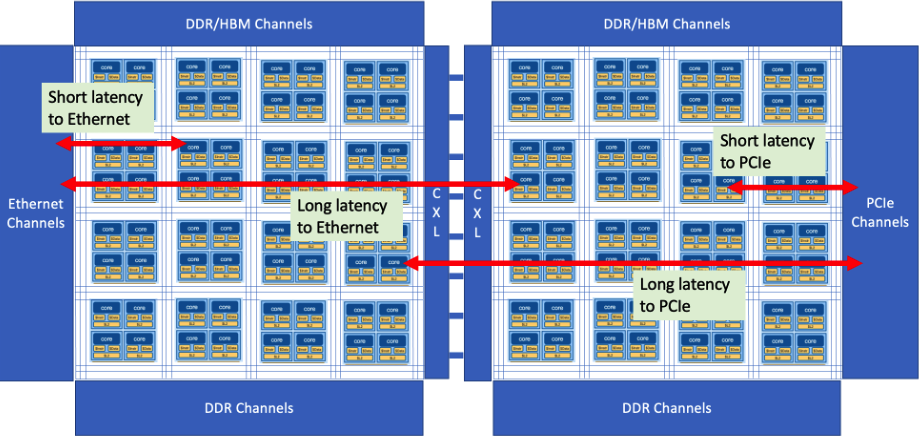

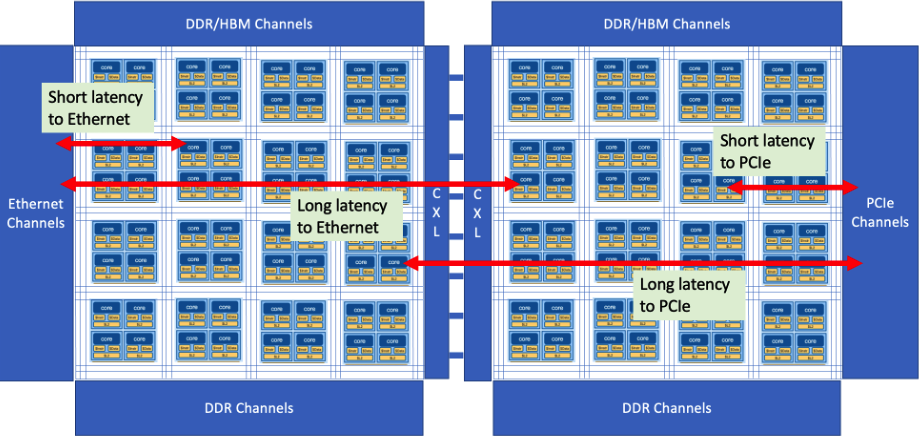

图:多芯片实现中不同的 I/O 延迟。(来源:Cadence)

连贯网格中的处理器阵列之间的通信延迟在单个裸片内将相对一致,但在多裸片实现中裸片之间的延迟可能会有很大差异(见图)。因此,设计发展出多种架构,可在未来使用——全连接网格、集线器和辐条内存系统或其他 2D 和 3D 结构,其中一个小芯片提供大系统缓存和主内存访问。此外,堆栈中的其他小芯片相互通信,并通过集线器与主存储器通信。

有效探索所有这些选项在很大程度上取决于针对实际工作负载准确建模性能。建模和分析只能在 RTL 域中使用仿真和原型进行探索。

SystemReady 合规性

服务器架构师面临的另一种问题是操作系统兼容性。您可以直接在大多数笔记本电脑上启动任何 Linux 发行版、虚拟机管理程序或 Windows。要在基于 Arm 的服务器上启动,此责任由服务器制造商和 Arm 分担。

Arm 开发了一个名为 SystemReady 的合规套件,以标准化一组最低要求,以解决这个问题和其他合规问题。PCIe 合规性是一个特别重要的组件,因为它直接为许多服务器接口协议提供或作为主要 I/O 的基础,以实现快速存储、快速网络和芯片外连贯接口。这里特别重要的是通过 PCIe 进行远程服务器引导。Arm 将此合规套件作为在 UEFI (BIOS) 层上运行的软件提供。Cadence 与 Arm 合作了几年,旨在将测试缩减为具有 PCIe 流量生成库的最小裸机测试套件,该库的仿真速度比 UEFI 测试套件更快,可以快速调整硬件调试。

服务器开发人员面临的另一个挑战是 PCIe 使用强排序的内存模型。Arm 支持标准允许的松散排序的内存模型。但只有强排序才能保证没有死锁。在松散订购下,硬件/固件开发人员必须提供该保证。不幸的是,这无法通过合规性检查。集成商必须再次在仿真器或原型系统上通过广泛的用例测试证明设计是死锁安全的。

使用 Cadence System 验证 IP 的方法使工程师能够在半天内启动并运行系统级测试套件,该套件可以根据 SystemReady 要求验证 PCIe 集成。此方法还可用于演示从连接到 PCIe 的闪存设备模型引导 SUSE Linux 和 Windows,这引起了高级服务器社区的极大兴趣。

不仅适用于服务器

Arm Neoverse 平台不仅是为高端服务器设计的。该家族已经开始进入其他云应用程序和通信基础设施,一直到边缘。在其中一些应用程序中,多核架构已经很重要。在大多数此类应用程序(例如汽车)中,对一系列开放和商业操作系统的开箱即用支持是必不可少的。

我相信用于自动生成系统级内容和验证系统级目标合规性的工具将在许多市场中具有广泛的适用性。EDA 行业需要超越传统的单接口单协议验证 IP (VIP) 范围,走向多接口多协议系统级 VIP 的新时代。

-

数字信号处理器重新采纳多核架构2009-04-09 0

-

多核处理器的优点2019-06-20 0

-

多核处理器SoC设计怎么才能满足嵌入式系统应用?2019-08-01 0

-

如何通过LabVIEW图形化开发平台有效优化多核处理器环境下的信号处理性能2021-04-26 0

-

一种对多核处理器架构上程序时间测量的全新技术介绍2021-12-14 0

-

多核处理器架构及调试2010-08-26 1335

-

多核处理器中的超越函数协处理器设计2017-01-07 775

-

多核处理器会取代FPGA吗?2017-02-11 1040

-

第1章 多核处理器基础2017-04-11 790

-

多核处理器成最新潮流,多核处理器几大特点你都知道吗?2017-04-24 1890

-

多核处理器架构及调试方案2017-10-25 818

-

基于FPGA的NoC多核处理器的设计2017-11-22 4704

-

处理器关于多核概念与区别 多核处理器工作原理及优缺点2017-12-08 31496

-

浅议多核处理器技术2021-03-29 926

-

多核处理器的挑战,多核处理器结构与分类2022-12-05 1053

全部0条评论

快来发表一下你的评论吧 !