页表如何支持多任务并行

描述

在大多数使用ARM处理器的系统中都会有很多应用或者任务同时运行,其中每个任务都在物理内存中拥有自己独立的页表。

每当应用程序启动时,操作系统都会为其分配一个页表,页表中的页表项将应用程序即将使用到的指令和数据映射到物理内存。如果应用程序映射到了未分配的物理空间,操作系统会完成相应页的分配,然后任务就可以进行下去。

多个任务可以同时运行,因为它们使用的是不同的VA-PA映射关系,而这些映射关系能够同时存在于物理内存中。当任务完成并且相应的页表映射不再需要时,该页表所处的物理空间可以被重新分配,删除相应的页表项(置成无效)并invalid TLB cache。

Address Space ID

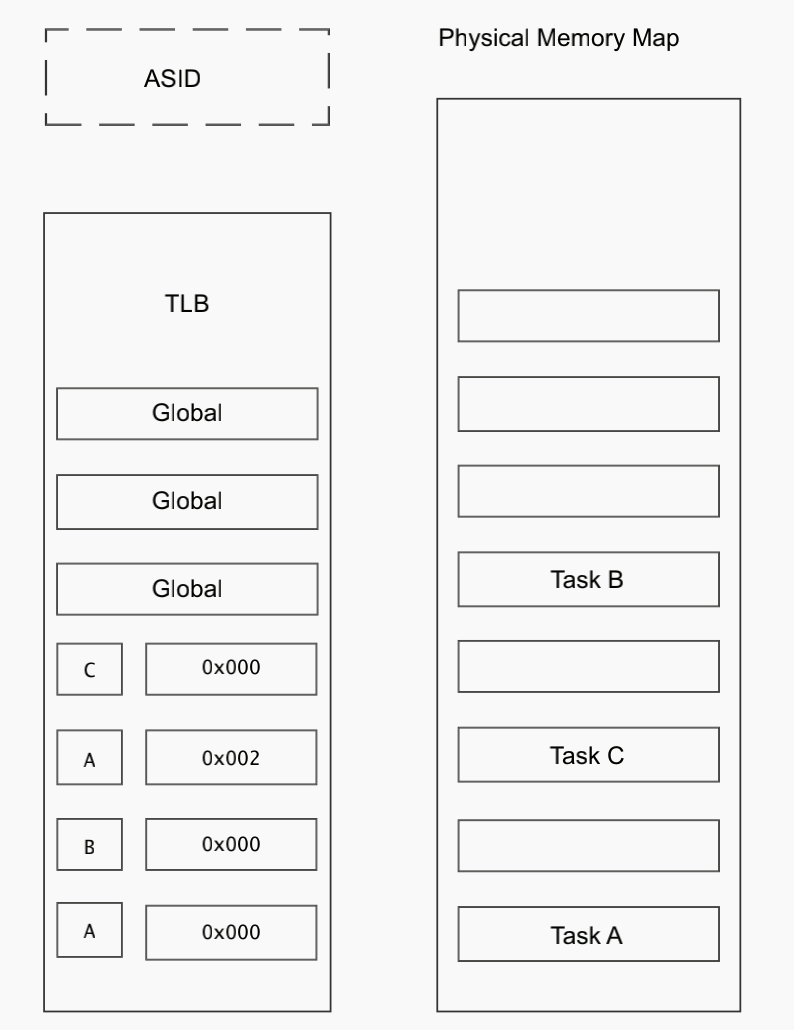

在页表中有一个nG(non-global)比特位。如果某个页设置了nG ,那么该页只与特定的应用或者任务相关联。当MMU执行VA-PA时,会同时用到VA和ASID(操作系统分配给每个任务的编号)。

作为页表内容的cache,TLB中的tag除了存储了VA,还有相应的ASID。在做TLB的hit-miss-check时,只有VA和ASID同时匹配才算hit。

上下文切换

所以,TLB中可能存放着多个相同VA对应的页表项。这些页表项具有不同的ASID,当某个ASID对应的任务完成或者这个任务的页表发生更改时只需要invalid某个ASID的TLB cache。这种操作叫context switches(上下文切换)。只针对特定ASID进行上下文切换,能够降低页表修改带来的性能开销,因为它避免了刷新全部的TLB。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

labview多任务构架2014-08-18 0

-

STemWin多任务的实现(工程支持IAR和MDK,使用μCOS-III实现多任务)2016-10-19 0

-

求一种基于比特表的实时多任务新调度算法2021-04-28 0

-

实时多任务操作系统(RTOS)2021-08-24 0

-

RTOS中的多任务切换的相关资料分享2021-12-06 0

-

多任务系统与单任务系统分别是指什么2021-12-22 0

-

多任务编程多任务处理是指什么2021-12-22 0

-

ZMC运动控制器多任务编程一2023-11-07 0

-

基于任务链的实时多任务软件可靠性建模2009-03-03 365

-

一种基于比特表的实时多任务新调度算法2009-05-15 415

-

苹果iPhone 4.0软件将支持多任务处理2010-03-12 463

-

iPhone 4.0多任务切换方式曝光2010-04-02 319

-

基于页的8051多任务模型2010-09-25 973

-

ABB机器人怎样多任务?ABB机器人多任务使用方法步骤详解2018-06-11 32257

-

浅谈RTOS中的多任务切换(基于UC/OS iii)2021-11-23 429

全部0条评论

快来发表一下你的评论吧 !