SiC VJFET的动态威廉希尔官方网站 模型

今日头条

描述

在与电子仪器相关的行业中,与传统的硅基半导体相比,宽带隙半导体的创新已被证明是有利可图且有效的。碳化硅 (SiC)宽带隙半导体是最先进的半导体之一,具有显着的相关性。这些半导体在各种参数(如高温、频率、电压和其他几个参数)上表现相当出色。

通过其成熟的制造工艺,碳化硅 (SiC) 具有无与伦比的电气特性,使其能够融入下一代器件制造。SiC-JFET 凭借其快速的开关速度和较低的导通电阻而吸引着市场,使其成为电子行业不断上升的商业市场中的高需求材料。

隶属于突尼斯莫纳斯提尔大学和法国里昂大学的一组研究人员开发了 JFET 的多维结构,以提高性能并通过对论文中已经提出的模型 进行测试来验证它,“A Multi -具有横向通道的 VJFET 的物理模型”[2]。

JFET的布局和特点

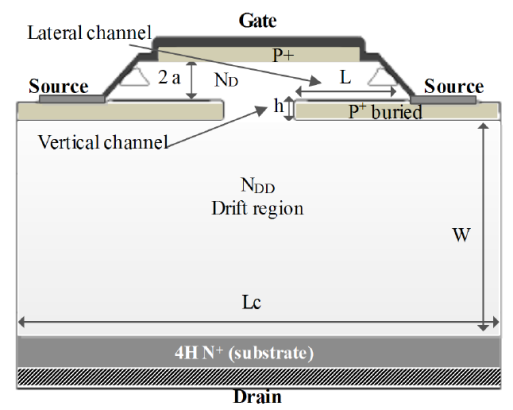

图 1:SiC JFET 的半电池横截面

JFET 是一种单极器件,具有两个串联的通道——横向通道和垂直通道。1200V SiC JFET采用SiCED/INFINION(TO220封装)制造,裸片尺寸为2.4×2.4mm 2,导通电阻为300mΩ,阈值栅极电压为-20V,饱和电流为20A。

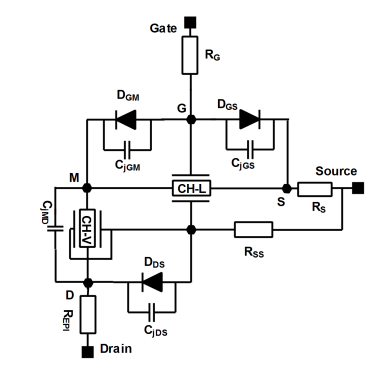

图 2:JFET 的静态和动态威廉希尔官方网站

模型

In the static and dynamic circuit model of JFET, we can see three physical capacitances: between gate and source (CjGS), gate and point M (CjGM), and drain and source (CjDS), with an additional capacitor between drain and point M (CjMD). To plot the C-V (Capacitance-Voltage) characteristics, the static and dynamic circuit model undergoes blocking conditions, which means there will be no static current flow in the channel. When the model is under prescribed conditions, the operating frequency is set to 300 kHz, which results in the impedance of the capacitors being greater than all the resistances present in the model circuit.

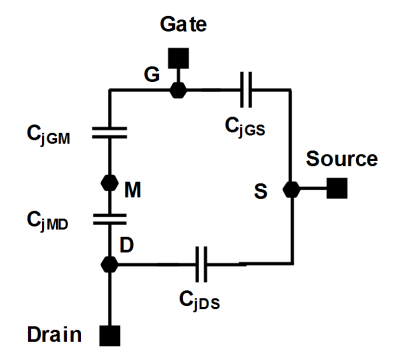

It is clear in the resultant circuit model shown in figure 3 that the capacitors will only affect the characteristics because the resistances are low in comparison to the capacitors. Taking the total capacitance between each terminal of the JFET, we get CGS, CDS, and CGD. [Note: Two capacitors between gate and drain are in series, hence they are taken as per the formula for resultant (total) capacitance between the two points.

CGS= CJGS

CDS = CjDS

1/CGD = 1/CjGM + 1/CjMD

Figure 3: Dynamic circuit model of a SiC JFET in blocking conditions

Numerical simulation

The researchers decided to use ISE TCAT Software for 2D numerical simulation of the SiC-JFET under predefined parameters, which are available in the research paper.

To start the simulation, a negative gate bias of -20 V is applied to make sure that the JFET is set to the off state. The capacitances can be extracted in the numerical simulations with a small AC signal analysis superimposed on the DC bias voltage when the lateral channel is completely blocked.

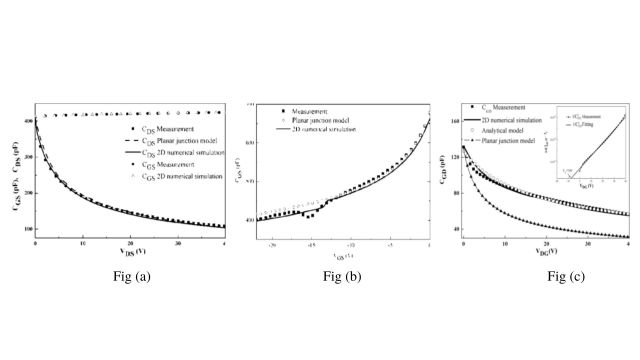

下图显示了作为测量特性的 C DS (V DS )、C GD (V GD )、C GS (V DS ) 和 C GS (V GS )与从二维数值获得的特性之间的比较模拟和分析模型。

图 4:C DS (V DS )、C GD (V GD )、C GS (V DS ) 和 C GS (V GS ) 的模拟

数值模拟分析

在数值模拟之后,分析了电容 CGD、CGS 和 CDS 的结果和测量值,电容值与相关空间电荷 (SCR) 宽度有关。以下标准将应用于 SCR 边界的计算。

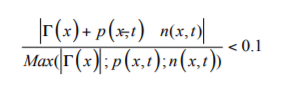

等式 1:计算 SCR 的边界

由上式可知,Г(x) 是净掺杂浓度,p(x,t) 是净空穴浓度,n(x,t) 是电子浓度,其中 x 和 t 分别是空间和时间变量。

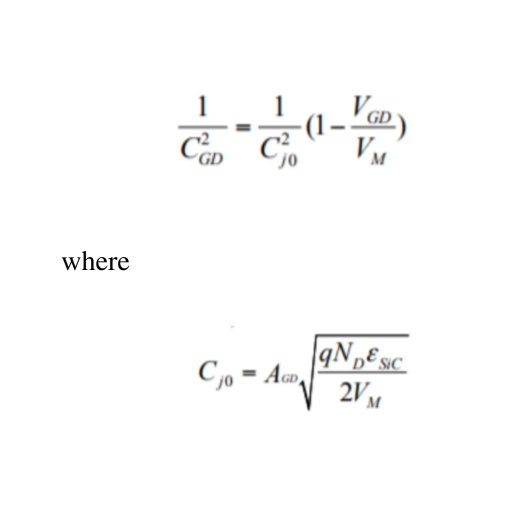

平面结栅源 C GS和 C DS电容与 V DS的测量、数值模拟和分析模型分别呈现在模拟图中。根据 C DS模型的方程,已经观察到 C GS(以圆圈和顶部箭头表示,约 400pF 电容)随 V DS微弱增加,但 C GS取决于 V GS并且类似于栅源平面电容。研究人员注意到,在这种情况下,实验和模拟结果是一致的,这在 CDS 和 CGS 电容的第三种情况下是不正确的,其中 CGD 电容不适合平面结电容。为了解决这种差异,该团队基于 TCAD 数值分析,提出了 CGD 电容的解析模型。

公式 2:C GD电容的分析模型

使用分析模型,可以得出结论,CGD 测量的电容与计算的电容之间存在相关性。

SiC JFET 动态模型验证

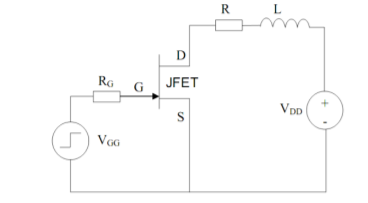

验证所提出的方法对于任何实验都非常重要。为此,该团队进行了测试,以评估切换情况下动态性能的有效性。负载电阻R、负载电感L和栅极电阻RG都是电感开关模拟威廉希尔官方网站 的一部分。

图 5:用于感应开关仿真的威廉希尔官方网站

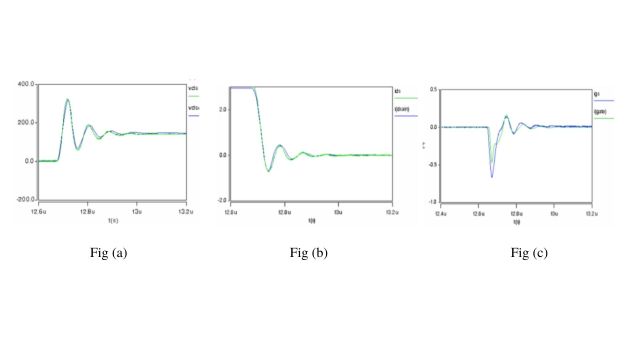

查看电感电阻开关关断的仿真(蓝色波形)和实验(绿色波形)结果的比较,我们可以看到两者非常吻合。对于感阻开关关断,我们看到两个结果彼此非常吻合。两个波形重合的点是理想点。但是,在实际场景中,误差会有所不同。目的是减少误差以获得优化的结果。

图6:感阻开关关断波形

结论与分析

该研究文章基于中开展的工作,旨在改进和验证 JFET 的多维结构。在阻断条件下(静态电流 = 0A),从 JFET 的静态和动态威廉希尔官方网站 模型开始,在 JFET 的每个端子之间产生串联和并联电容器。CV 特性的数值模拟显示了不同的结果,其中一些结果与其他结果不遵循相同的模式。在这篇研究文章中,该团队开发了一个具有横向通道的垂直 SiC JFET 的动态模型,该模型考虑了终端电容中的多功能效应。后来,动态模型在VHDL-AMS软件中进行,

审核编辑:刘清

-

如何建立动态电阻模型?2012-08-20 0

-

SIC JFET 驱动威廉希尔官方网站 设计2016-12-12 0

-

SiC-MOSFET的应用实例2018-11-27 0

-

搭载SiC-MOSFET和SiC-SBD的功率模块2019-03-12 0

-

SiC功率模块的特征与威廉希尔官方网站 构成2019-03-25 0

-

boost威廉希尔官方网站 动态模型仿真的占空比问题2019-12-03 0

-

【罗姆SiC-MOSFET 试用体验连载】开箱报告2020-05-19 0

-

基于动态描述逻辑的UCON授权模型2009-04-14 568

-

面向模型的动态架构2009-04-21 695

-

空间动态模型建模方法分析2011-02-23 919

-

SiC MOSFET与SiC SBD换流单元瞬态模型2018-02-01 954

-

基于SiC MOSFET的精确分析模型2018-03-13 1409

-

具有动态温度补偿的修正 MOSFET 模型2022-11-15 308

-

碳化硅VJFET的动态威廉希尔官方网站 模型设计2023-08-29 756

-

怎么提高SIC MOSFET的动态响应?2023-12-21 641

全部0条评论

快来发表一下你的评论吧 !