DDR4 IP校准后硬件故障的调试方法与根本原因分析

电子说

描述

本篇博客将为您演示如何使用此报告来帮助加速调试,甚至完全避免硬件故障,最后确定此问题根本原因是校准完成时出现争用状况。出现争用状况的原因是由于某个多周期约束所覆盖的时序例外,由此导致在时序分析报告中并未标记此问题。

这是使用方法论报告系列博文的第 5 部分。如需阅读整个系列中的所有博文,请点击下方标题查看。

问题说明:

客户在使用 UltraScale+ DDR4 IP 时,在硬件中遇到校准后数据错误。

根据设计的布线和实现,此问题与构建有关,换言之,在产品开发期间对多个构建镜像进行测试时,此问题可能出现而后又消失。此外,此问题可能仅在小部分板上出现。

时序报告显示没有任何违例。

调试方法:

由于重新实现后,此问题可能就会消失,因此无法使用 ILA 调试。

我们在已布线的 DCP 中使用 ECO 来探测未使用的管脚的信号,通过示波器观测信号发现哪个(些)信号开始显现错误。

最终,我们将问题范围缩小到 1 个特定的信号线,在 DCP 中对该信号线进行重新布线后,故障消失了。

随后,我们检查了与此信号线相关的路径上的时序分析和时序约束:

1. 经过该信号线的路径的时序报告。在此报告中,我们得知,所涉及的路径被多周期路径约束所覆盖

report_timing -through [get_nets ]

2. 打开“Timing Constraints”Wizard,查找对应的多周期路径约束。

工具 (Tools) -> 时序 (Timing) -> 编辑时序约束 (Edit Timing Constraints)

我们在“Timing Constraints”Wizard 中发现了以下多周期路径约束:

set_multicycle_path -setup -from [get_pins */u_ddr_cal_top/calDone*/C] 8 set_multicycle_path -hold -end -from [get_pins */u_ddr_cal_top/calDone*/C] 7

基于以上分析,我们判定在这些路径上存在争用状况问题。

这些多周期路径约束不应添加,在此用例中,应在每个时钟周期内正确捕获数据,以避免出现争用状况,因此,这些路径不属于多周期路径。

根本原因分析:

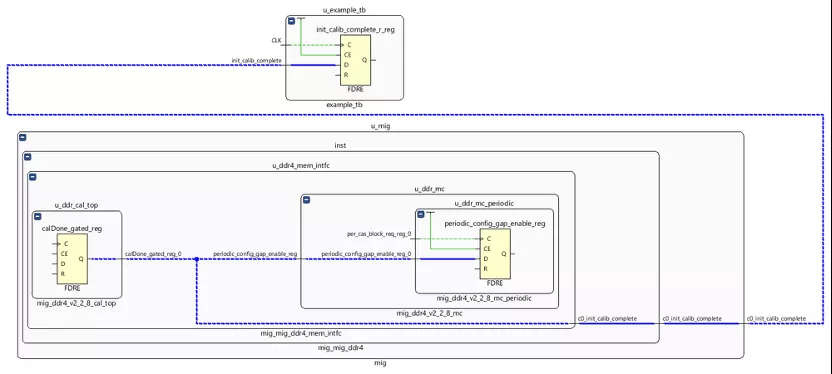

以下就是发生争用状况问题的路径。

其中 2 个目标都应在同一个周期内接收到 calDone 信号,因为这两者紧密相关。这 2 条路径属于不同时序路径,各自都应在不同时钟周期达成时序收敛(根据多周期约束,应在 1 到 8 个周期内达成时序收敛)。这可能导致 calDone 在不同时间线到达目标,导致功能异常。

另一方面,2 个目标都没有 CE 管脚控制(CE 管脚绑定到 VCC)。因此,未能在同一时钟周期内捕获 2 条路径上的数据,所以这些路径并非合格的多周期路径。

此多周期约束违例实际上是由 Methodology Report 捕获的:

TIMING-46 警告 1

多周期路径含绑定 CE 管脚

在寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_cal_top/calDone_gated_reg/Q

与寄存器

u_example_tb/init_calib_complete_r_reg/D

之间定义了 1 条或多条多周期路径,并具有直接连接,且 CE 管脚已连接到 VCC(请参阅 Vivado IDE 中的“时序约束 (Timing Constraint)”窗口中的约束位置 6)。这可能导致路径要求不准确。

TIMING-46 警告 2

多周期路径含绑定 CE 管脚

在寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_cal_top/calDone_gated_reg/Q

与寄存器

u_mig/inst/u_ddr4_mem_intfc/u_ddr_mc/u_ddr_mc_periodic/periodic_config_gap_enable_reg/D

之间定义了 1 条或多条多周期路径,并具有直接连接,且 CE 管脚已连接到 VCC(请参阅 Vivado IDE 中的“时序约束 (Timing Constraint)”窗口中的约束位置 6)。

这可能导致路径要求不准确。

最好在流程初期阶段尽早检查 Methodology Report。在诸如此类的示例中,它可帮助您捕获并修复多周期违例,并避免发生硬件故障。您还可以在调试过程中先运行 Methodology Report,并查看警告,其中高亮的违例将有助于加速问题调查。

解决办法:

【赛灵思答复记录 73068】提供的补丁可用于解决在低于 2020.1 版的版本中发生的此问题。

从 2020.1 版起,已移除了多周期路径约束,并在路径上添加了流水线阶段,以简化时序收敛,同时确保所有目标都能在同一个互连结构周期内达成时序收敛。

结论:

1. 在设计流程中尽早运行 Methodology Report 以便捕获并修复潜在问题。

2. 请在含绑定到 VCC 的 CE 管脚的路径上谨慎使用多周期约束。

审核编辑:汤梓红

-

电池漏液的根本原因?如何判定电池是否漏液?2021-03-11 0

-

引起调节的根本原因是什么2021-09-01 0

-

引起调节的根本原因是偏差吗2021-09-10 0

-

低功耗产生的根本原因及其控制方法2021-12-31 0

-

内核oops的根本原因是什么?我们如何调试内核oops?2023-04-20 0

-

使用SPI找到无铅制造缺陷的根本原因2009-10-01 608

-

如何修复硬件中存在DDR4校准错误2021-09-03 2985

-

硬件中存在DDR4校准后数据错误2021-09-16 2512

-

XILINX使用方法论设计无法连贯布线2021-09-28 1785

-

DFX设计无法连贯布线的根本原因及修护2022-08-02 1552

-

时钟域交汇相关处理错误的根本原因分析2022-08-02 1011

-

硬件中存在DDR4校准错误的调试方法与根本原因分析2022-08-02 5801

-

网线是影响网速快慢的根本原因吗2022-09-08 8715

-

速率越高的DDR4,等长控制越严格?2022-09-13 1388

-

MES系统没效果的根本原因2024-02-22 123

全部0条评论

快来发表一下你的评论吧 !