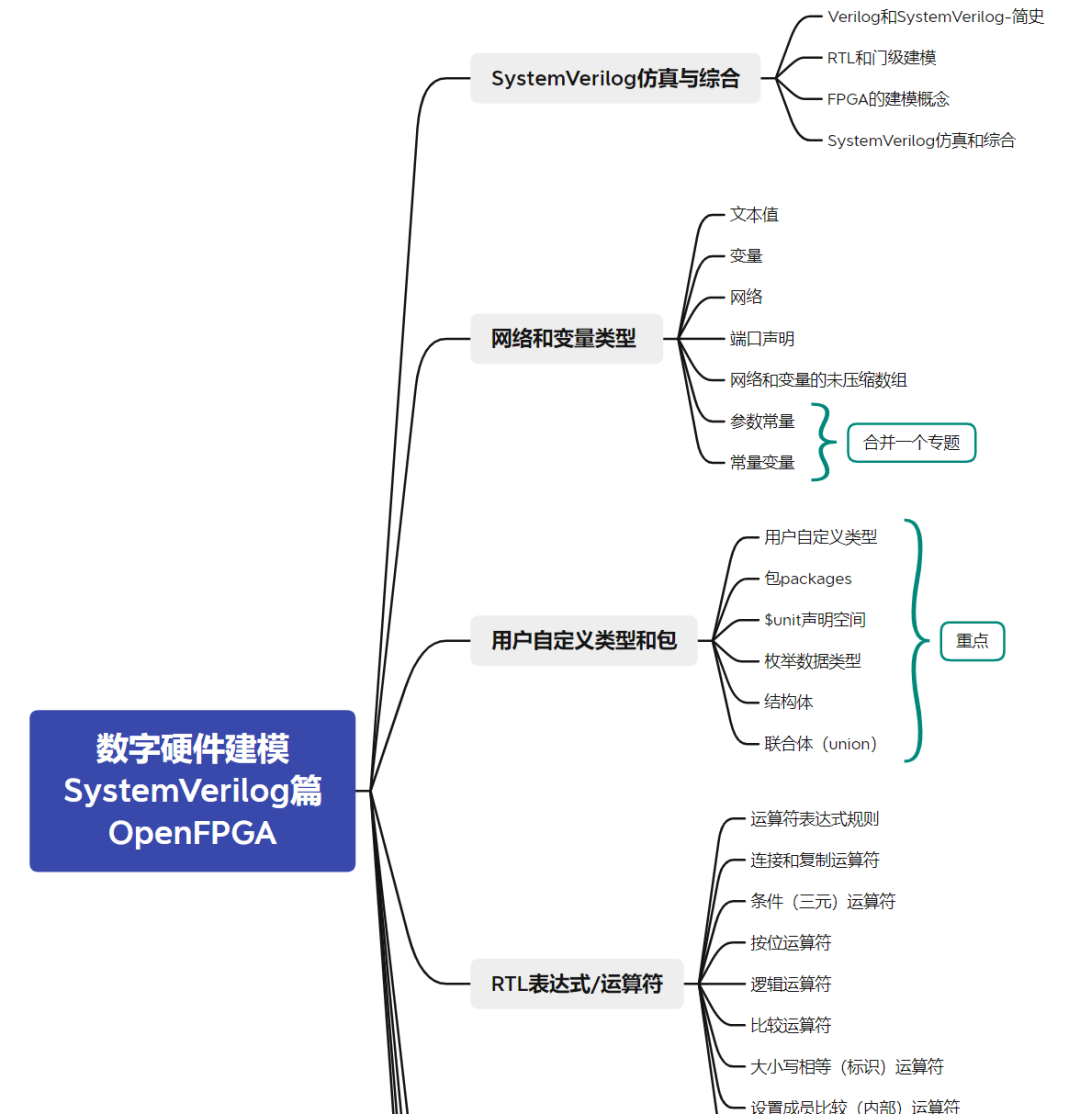

SystemVerilog-运算符/表达式规则

描述

数字硬件建模SystemVerilog-条件(三元)运算符

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

马上HDLBits-SystemVerilog版本也开始准备了,基本这一部分完成后就开始更新~

介绍

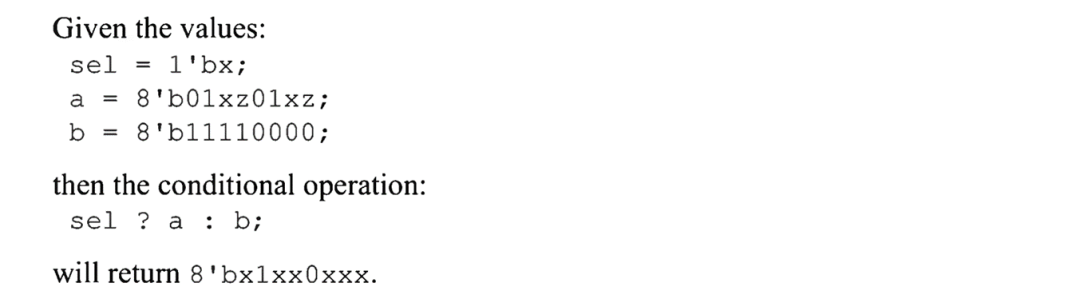

RTL建模中广泛使用的运算符是条件运算符,也称为三元运算符,该运算符用于在两个表达式之间进行选择——表5-2列出了用于表示条件运算符的重点。

表5-2:RTL建模的条件(三元)运算符

| 运算符 | 示例用法 | 描述 |

|---|---|---|

| ?: | s?m:n | 如果s为真,则选择m;如果s为假,则选择n,否则(s不为真不为假)对m和n进行按位比较 |

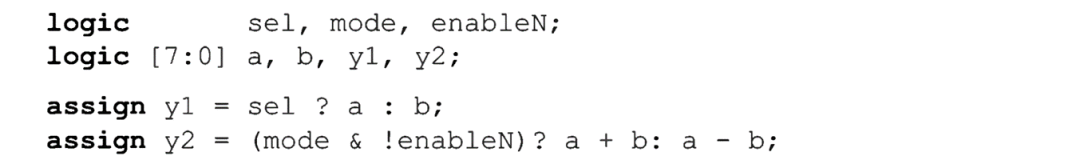

问号(?)前面列出的表达式被称为控制表达式(control expression),表示它可以是一个简单的整数值(任何大小的向量,包括1位),也可以是另一个返回整数值的操作的结果。例如:

使用以下规则将控制表达式计算为true或false:

如果所有位为l,则表达式为true。

如果所有位均为0,则表达式为false。

如果未设置任何位且并非所有位均为0,则表达式未知,如果某些位为X或Z,则可能出现这种情况。

对于4-state值,控制表达式可能既不是真的也不是假的。在下面的值中,没有一个位是l,但不是所有的位都是0。

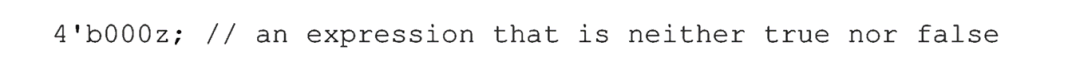

当控制表达式未知时,条件运算符对两个可能的返回值进行按位比较。如果对应位均为0,则该位位置返回0,如果对应位均为l,则该位位置返回1。如果对应的位不同,或者任一位有X或Z值,则返回该位位置的X。下面的示例演示了这种仿真行为。

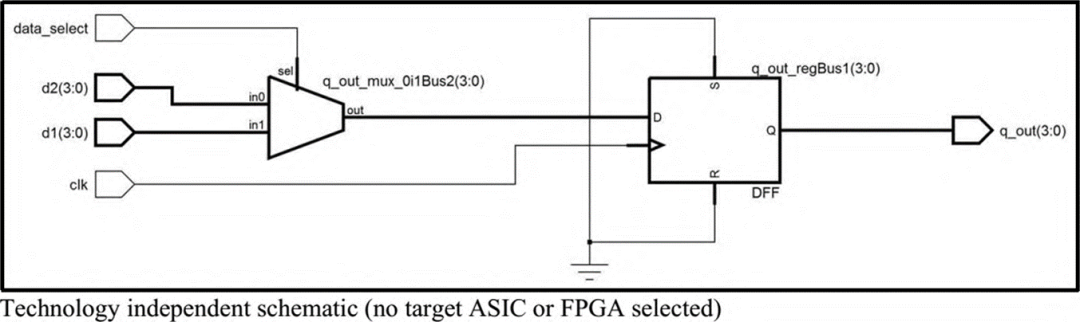

条件运算符的行为通常类似于硬件多路复用器。示例5-3说明了如何使用条件运算符在寄存器的两个输入之间进行选择。图5-3显示了综合该示例的结果。条件运算符映射到四个多路复用器,四位d1和d2输入的每一位对应一个多路复用器。

示例5-3:使用条件运算符:4位多路复用寄存器D输入

// 4-bit register with multiplexed D input, using conditional // operator. // //`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords module muxed_register #(parameter WIDTH = 4) // register size (input logic clk, // 1-bit input input logic data_select, // 1-bit input input logic [WIDTH-1:0] d1, d2, // scalable input size output logic [WIDTH-1:0] q_out // scalable output size ); timeunit 1ns; timeprecision 1ns; always_ff @(posedge clk) q_out <= data_select? d1 : d2; // store d1 or d2 endmodule: muxed_register //`end_keywords图形5-3:示例5-3的综合结果:条件运算符(多路复用寄存器)

图5-3所示的威廉希尔官方网站 是综合编译器将威廉希尔官方网站 映射到特定ASIC或FPGA目标实现之前的中间通用综合结果。用于生成图5-3的综合编译器使用了具有未连接的set和rst输入的通用触发器,使用ASIC或FPGA库的最终实现可能能够使用没有这些输入的触发器(如果目标设备中可用)。不同的综合编译器可能会使用不同的通用型组件来表示这些中间结果。

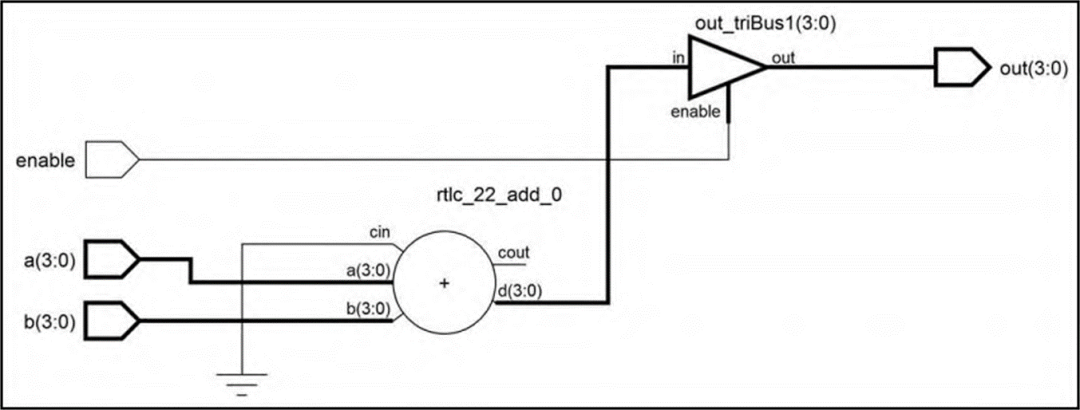

条件运算符并不总是作为多路复用器实现。综合编译器可能会根据操作数的类型和运算的上下文,将条件运算符映射并优化为其他类型的门级逻辑。在示例5-4中,条件运算符表示三态缓冲器,而不是多路复用逻辑,图5-4显示了综合该示例的结果,

示例5-4:使用条件运算符:带三态输出的4位加法器

// 4-bit adder with tri-state outputs, using conditional operator // (no carry). // //`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords module tri_state_adder #(parameter N = 4) // N-bit adder size (input logic enable, // output enable input logic [N-1:0] a, b, // scalable input size output tri logic [N-1:0] out // tri-state output, net type ); timeunit 1ns; timeprecision 1ns; assign out = enable? (a + b) : 'z; // tri-state buffer endmodule: tri_state_adder //`end_keywords

在本例中,条件运算符(?)选择输出端口应分配(a+b)或高阻抗。如果en为false,则将out赋值为z。’z标记是一个文字值,用于将表达式的所有位设置为高阻抗,并自动缩放到表达式的向量大小。有关向量填充文字值的更多详细信息,请参见之前的文章。

在示例5-4中观察,out三态输出端口被声明为3-state logic类型,而不是通常的逻辑类型,logic数据类型只定义端口时可以有四态值,它不定义端口类型是网络类型或者变量类型。输出端口默认为变量类型,除非显式声明为NET(网络)类型。(相反,输入端口将默认为NET类型,除非显式声明为变量类型),关键字•tri声明网络类型。tri类型在各个方面都与wire类型相同,但tri关键字可以帮助记录网络或端口的预期三态(高阻抗)值。

图5-4:示例5-4的综合结果:条件运算符(三态输出)

SystemVerilog-连接和复制运算符

SystemVerilog-运算符/表达式规则

-

JAVA语言的运算符及表达式2008-12-06 0

-

数据类型、运算符与表达式2009-03-10 0

-

关于C语言的运算符和表达式--笔记12015-07-19 0

-

C语言程序设计--运算符与表达式2010-07-14 461

-

单片机C语言教程-运算符和表达式2010-03-27 2219

-

基于运算符信息的数学表达式检索技术2021-04-29 698

-

RTL表达式和运算符2022-07-27 1719

-

关于RTL表达式和运算符2022-09-01 1879

-

玩转SQLite8:运算符与表达式2022-09-27 2445

-

运算符/表达式规则2023-02-09 986

-

逻辑运算符与表达式2023-02-21 2124

-

位逻辑运算符与表达式2023-02-21 1244

-

C语言基本的算术运算符及表达式2023-03-09 1608

全部0条评论

快来发表一下你的评论吧 !