一文解析多芯片堆叠封装技术(上)

今日头条

描述

随着信息数据大爆炸时代的来临,市场对存储器的需求持续增长。在芯片成品制造环节中,市场对于传统打线封装的依赖仍居高不下。市场对于使用多芯片堆叠技术、来实现同尺寸器件中的高存储密度的需求也日益增长。这类需求给半导体封装工艺带来的不仅仅是工艺能力上的挑战,也对工艺的管控能力提出了更高的要求。

在这里,我们将向大家介绍长电科技的多芯片堆叠封装技术的优势、工艺和管控能力,内容将分为上下两期呈现。

多芯片堆叠封装技术优势

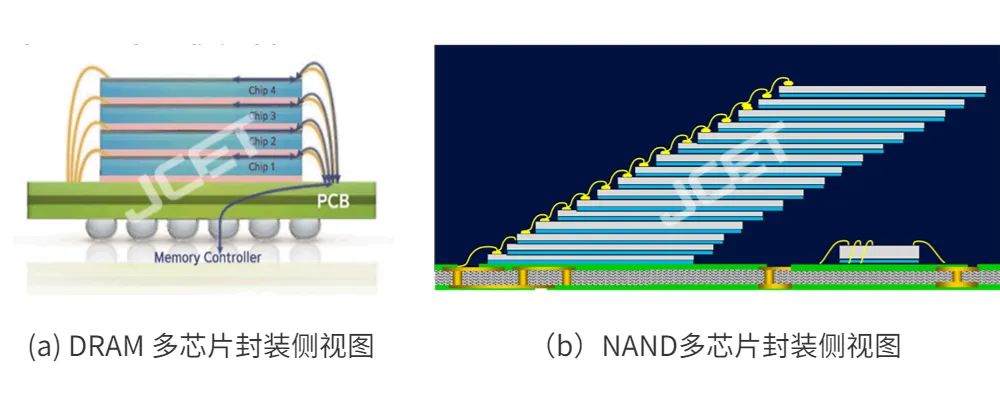

图1 多芯片封装侧视图

图1是两个不同类型的存储器封装的侧视图,从其封装结构我们可以看出,两个封装都是由多个芯片堆叠而成,目的是为了减少多芯片封装占用的空间,从而实现存储器件尺寸的最小化。其中较关键的工艺是芯片减薄、切割,以及芯片贴合。

从市场需求来看,倒装封装(FC)和硅通孔(TSV),以及晶圆级(wafer level)的封装形式可以有效地减小器件尺寸的同时,提高数据传输速度,降低信号干扰可能。但就目前的消费类市场需求来看,还是基于传统打线的封装形式仍占较大比重,其优势在于成本的竞争力和技术的成熟度。

长电科技目前的工艺能力可以实现16层芯片的堆叠,单层芯片厚度仅为35um,封装厚度为1mm左右。

多芯片堆叠封装关键工艺

之芯片减薄、切割

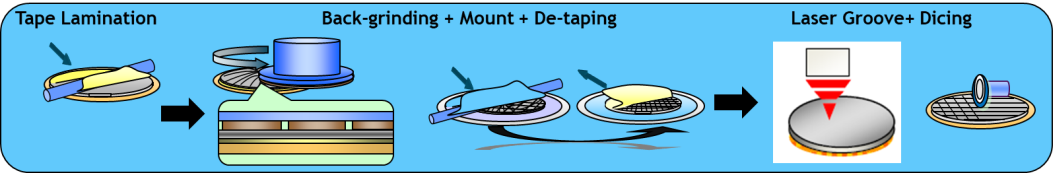

研磨后切割

(Dicing After Grinding,DAG)

主要针对较厚的芯片(厚度需求>60um),属于较传统的封装工艺,成熟稳定。晶圆在贴上保护膜后进行减薄作业,再使用刀片切割将芯片分开。适用于大多数的封装。

图2 DAG(来源:DISCO)

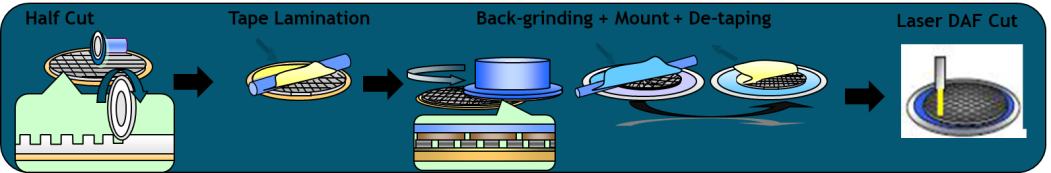

研磨前切割

(Dicing Before Grinding,DBG)

主要针对38-85um芯片厚度,且芯片威廉希尔官方网站 层厚度>7um,针对较薄芯片的需求和存储芯片日益增长的威廉希尔官方网站 层数(目前普遍的3D NAND层数在112层以上)。使用刀片先将芯片半切,再进行减薄,激光将芯片载膜 (Die attach film)切透。适用于大部分NAND 芯片,优势在于可以解决超薄芯片的侧边崩边控制以及后工序芯片隐裂(die crack)的问题,大大提高了多芯片封装的可行性和可量产性。

图3 DBG(来源:DISCO)

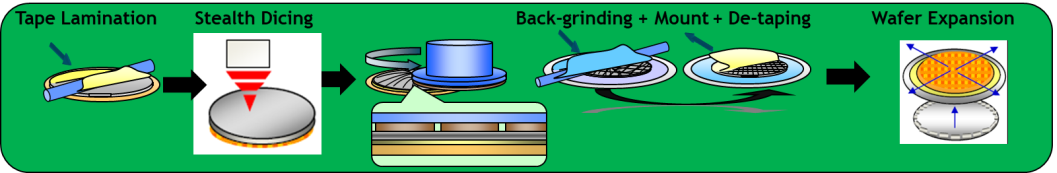

研磨前的隐形切割

(Stealth Dicing Before Grinding,SDBG)

主要针对35-85um芯片厚度,且芯片威廉希尔官方网站 层厚度<7um,主要针对较薄芯片的需求且威廉希尔官方网站 层较少,如DRAM。使用隐形激光先将芯片中间分开,再进行减薄,最后将wafer崩开。适用于大部分DRAM wafer以及威廉希尔官方网站 层较少的芯片,与DBG相比,由于没有刀片切割机械影响,侧边崩边控制更佳。芯片厚度可以进一步降低。

图4 SDBG(来源:DISCO)

审核编辑:刘清

-

芯片的堆叠封装是怎么进化的电子学习 2022-12-10

-

科技产品下一个重大突破将在芯片堆叠领域出现2017-11-23 0

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 0

-

芯片堆叠的主要形式2020-11-27 0

-

多层芯片堆叠封装方案的优化方法2012-01-09 1387

-

英特尔逻辑芯片3D堆叠技术“Foveros” 将实现世界一流性能2018-12-14 2666

-

华为又一专利公开,芯片堆叠技术持续进步2022-05-07 100516

-

华为公布芯片堆叠专利,能否解缺芯燃眉之急2022-05-09 24809

-

华为公布两项芯片堆叠相关专利2022-05-09 5757

-

华为芯片堆叠封装专利公开2022-08-11 9631

-

一文解析芯片堆叠封装技术2022-11-30 2016

-

芯片堆叠技术在系统级封装SiP中的应用存?2023-02-11 2041

-

多芯片封装技术是什么2023-05-24 2106

-

华为公布“芯片堆叠结构及其形成方法、芯片封装结构、电子设备”专利2023-08-09 1962

-

芯片堆叠封装技术实用教程(52页PPT)2024-11-01 3101

全部0条评论

快来发表一下你的评论吧 !