芯片设计之逻辑综合过程(下)

电子说

描述

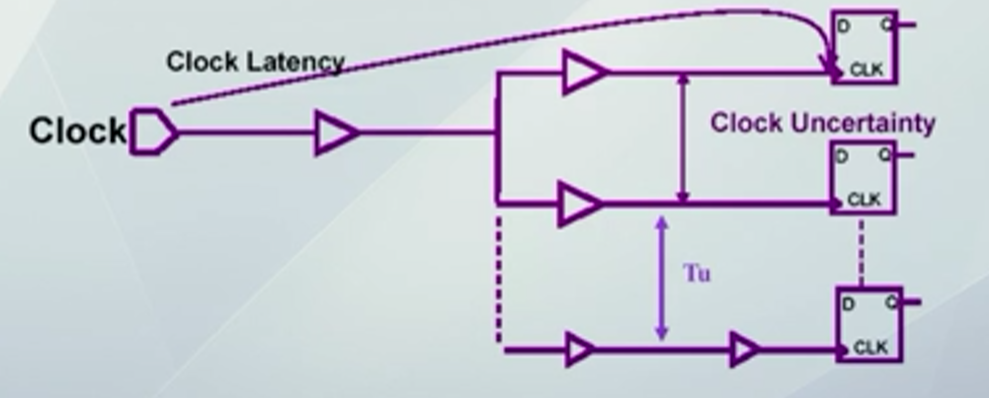

逻辑综合过程(5)设置约束中,时序约束除需估计威廉希尔官方网站 中的连线参数外,还需要关注时钟网络。在复杂网络中,输入的时钟信号可能会连接数百个D触发器,需要通过树状网络连接,树状网络的每个分叉连接有限个D触发器。为使时钟信号到达每个D触发器的时间近似相等,树状网络需要尽可能均匀。

描述时钟网络信号的参数有两个:Clock Latency和Clock Uncertainty。Clock Latency表示时钟信号经由其他元器件和连线到达D触发器的延时,Clock Uncertainty表示各个D触发器间时钟延时的微小差异。

综上,过程(5)设置约束中,时序约束通过静态时序分析的准则、估算连线参数、确定时钟网络参数完成约束。

图片来源:学堂在线《IC设计与方法》

当时序约束满足后,综合逻辑所需的软件将尝试满足面积约束要求,一般面积约束的要求是将芯片的面积最小化。

以下是描述芯片的面积的三种方式:

(1)通过与非门对芯片进行描述,得出芯片等效多少门。

(2)通过等效晶体管数量的方式进行描述。

(3)通过物理面积的方式进行描述,常用的面积单位是平方微米。

非专业人员倾向使用方式(1)和方式(2)描述芯片面积。EDA软件(根据代码自动生成芯片威廉希尔官方网站 的软件)中对芯片面积的描述不清晰,需要设计人员判断数值的单位是门、晶体管、物理面积三种中的哪一种。如果数值包含0.5,可能是以门为单位,因为一个非门大约等效0.5个与非门;如果数值为整数,可能是以晶体管为单位;如果数值有多个小数位,可能是以物理面积为单位。

设置约束结束后,可以进行逻辑综合操作。逻辑综合操作中软件可以对威廉希尔官方网站 做以下优化:

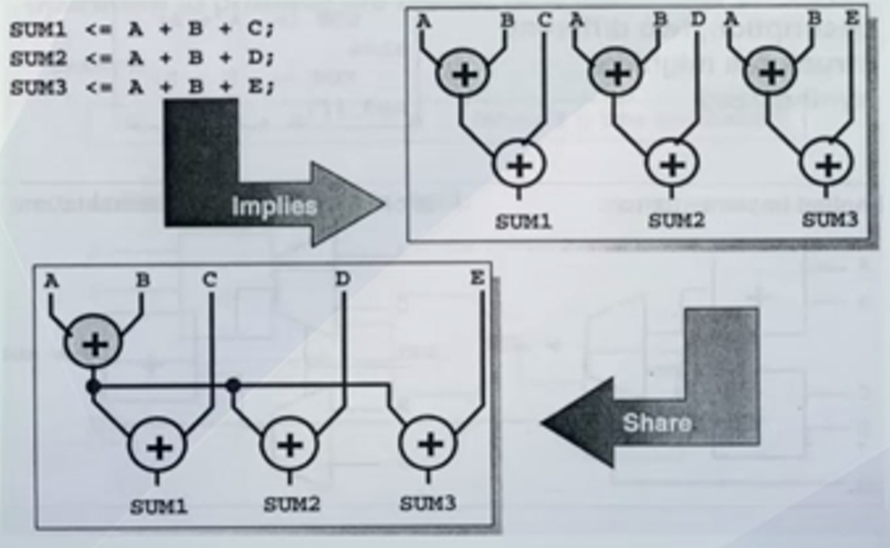

(1)共享表达式:如下图所示,三个表达式中均有A+B,软件会将重复的A+B威廉希尔官方网站 化简。

图片来源:学堂在线《IC设计与方法》

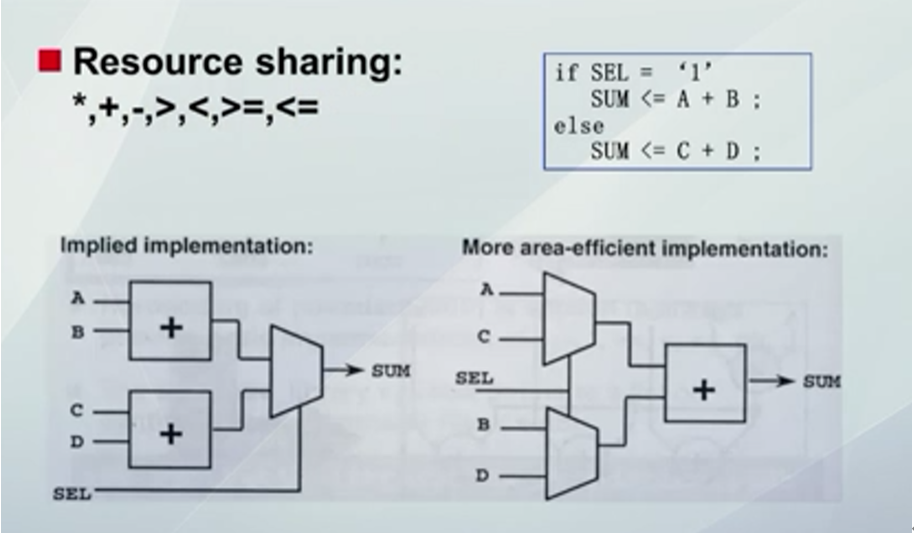

(2)资源共享:加法器(下图威廉希尔官方网站 中带加号的正方形)所需的资源多于多路选择器(下图威廉希尔官方网站 中的梯形)所需的资源,通过改变威廉希尔官方网站 结构,将资源选择器共享转化为加法器共享,节省资源。

图片来源:学堂在线《IC设计与方法》

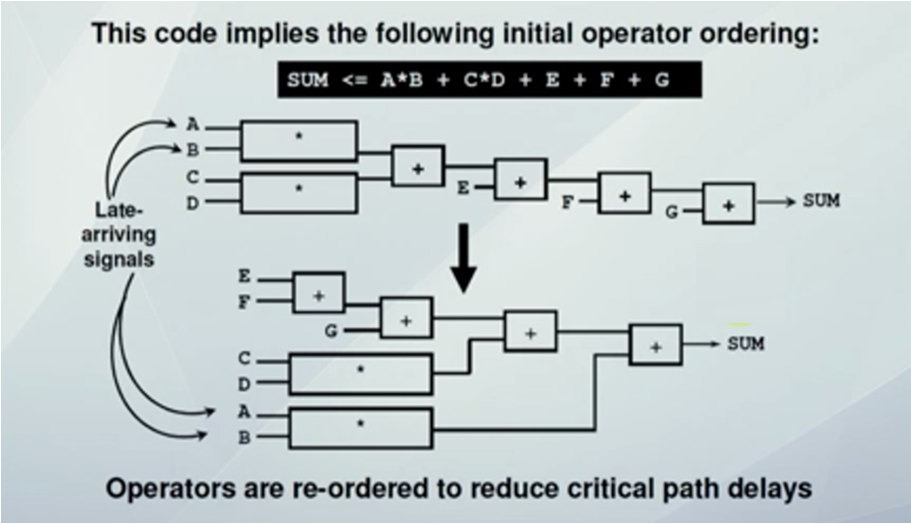

(3)操作重新排序:下图是操作重新排序的案例,如果A、B、C、D、E、F信号不能同时到达,如A、B信号到达较晚,操作重新排序后的威廉希尔官方网站 (图中箭头指向的威廉希尔官方网站 )运算速度更快。

图片来源:学堂在线《IC设计与方法》

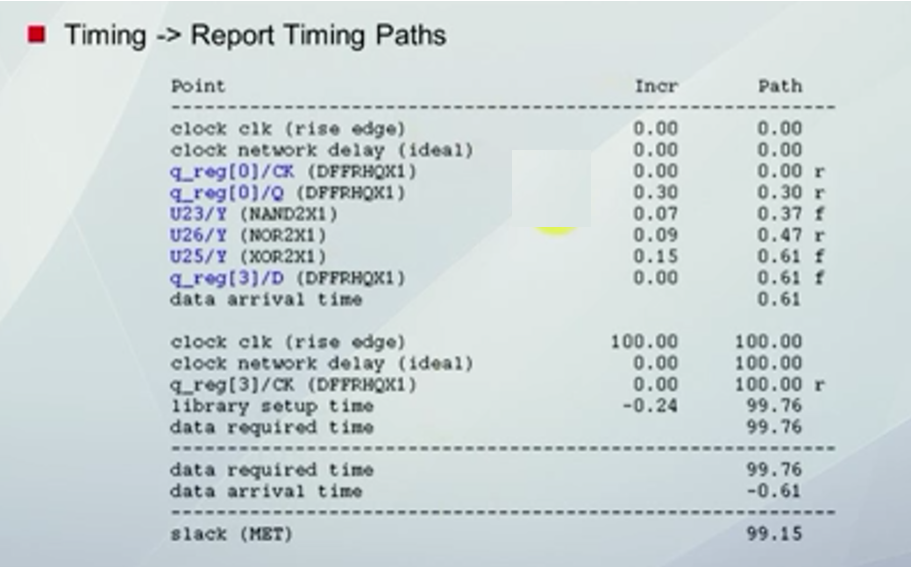

逻辑综合操作后,进行结果分析。首先需要关注时序报告。

时序报告的第一部分是数据到达时间(data arrival time),表示上一级触发器时钟信号出现开始,经过所有元器件所需要的时间(个人理解)。

时序报告的第二部分是数据需求时间(data required time),表示数据传输可以使用的时间。

如果数据需求时间-数据到达时间>0,则满足时序约束,可以进行面积报告分析,否则需修改约束或设计代码。根据时序分析结果,可以重建关键路径,进一步优化威廉希尔官方网站 。

图片来源:学堂在线《IC设计与方法》

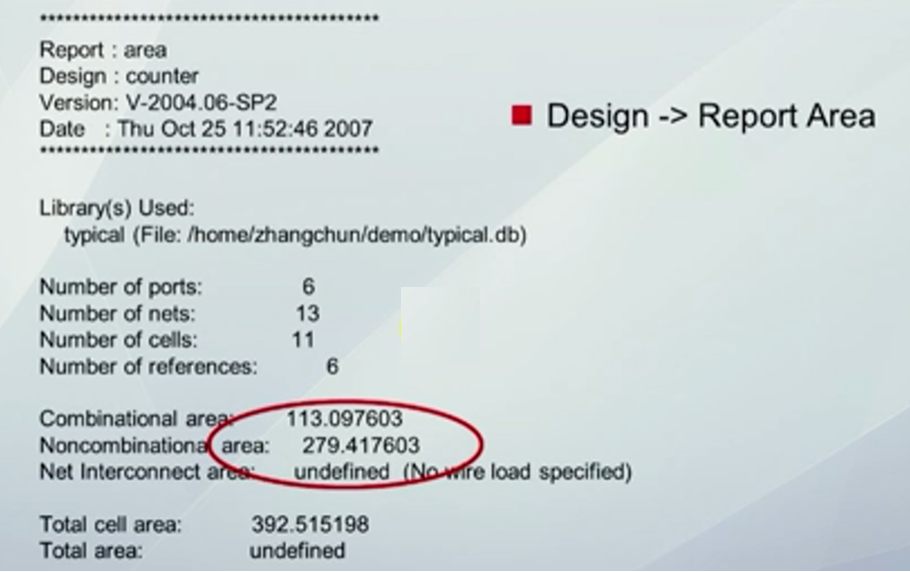

其次关注面积报告,下图报告中红圈内表示芯片的面积参数,因为报告中数值有多个小数位,所以数值的单位是平方微米。

在商业设计中,需要定义芯片内连线的模型以更准确地估算出芯片面积(含个人理解),Net Interconnect area会有具体数值,不会如下图中表示的undefined。

结果分析满足设计条件后,保存结果,逻辑综合过程结束。

审核编辑 :李倩

-

浅谈IC设计中逻辑综合2013-05-16 0

-

求一套手工逻辑综合的方法和综合步骤?2021-04-08 0

-

DC逻辑综合详解2021-07-29 0

-

什么是逻辑综合?2021-11-02 0

-

DC逻辑综合2011-12-29 788

-

Labview之综合实例2016-04-19 1015

-

逻辑漏洞之越权详解2017-09-07 852

-

ASIC逻辑综合及Synopsys Design Compiler 的使用资料说明2019-10-23 782

-

芯片设计之ASIC设计流程和逻辑综合2022-08-12 5100

-

芯片设计之逻辑综合过程2022-08-12 3872

-

逻辑综合与物理综合2022-11-28 2717

-

EDA逻辑综合概念 逻辑综合三个步骤2023-06-19 3378

-

eda综合有哪些类型 逻辑综合的原理2023-06-26 2148

-

逻辑综合的流程和命令简析2023-08-09 962

-

什么是逻辑综合?逻辑综合的流程有哪些?2023-09-15 5231

全部0条评论

快来发表一下你的评论吧 !