芯片设计降低功耗的方法

电子说

描述

功耗是芯片中比较重要的一个性能指标,有时甚至可以决定一个芯片的成败。众所周知,前段时间闹得沸沸扬扬的“骁龙火龙”事件,就大大影响了这款芯片的市占率。对于工业级和车规级的芯片,功耗的高低体现的不是很明显。对于消费级芯片(如手机CPU,IoT芯片等),由于往往应用在小型移动设备中,低功耗设计就显得尤为重要。

有业内专家曾经指出,在不同的设计层次,进行功耗优化的效果也不同。下表显示了在一个产品的不同周期,可以减少功耗的百分比。

| 设计层次 | 降低功耗百分比 |

| 版图级 | <5% |

| 晶体管级 | 5% |

| 门级 | 10% |

| RTL级 | 20% |

| 系统级 | >50% |

门控时钟介绍

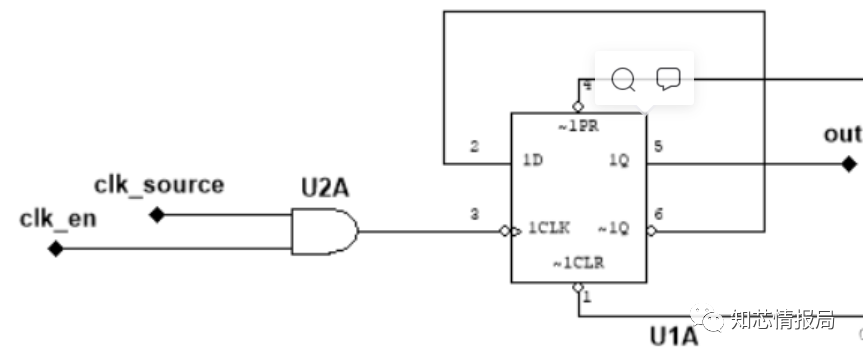

一般来讲,时钟树贯穿于整个芯片内部,由大量的buffer和反相器组成。时钟信号作为芯片中toggle率最高的信号,功耗可高达整个芯片功耗 的30%,甚至更高。加入门控时钟(clock gating,cg)威廉希尔官方网站 ,可大大降低时钟树的toggle行为,从而降低开关功耗。此外,时钟引脚开关行为的减少,寄存器的内部功耗也会减少。门控时钟是减少功耗的有力手段,在时钟被门控关闭后,该时钟网络和其中的寄存器都会停止翻转,因此功耗会显著减低。一个典型的门控时钟设计如下图所示:

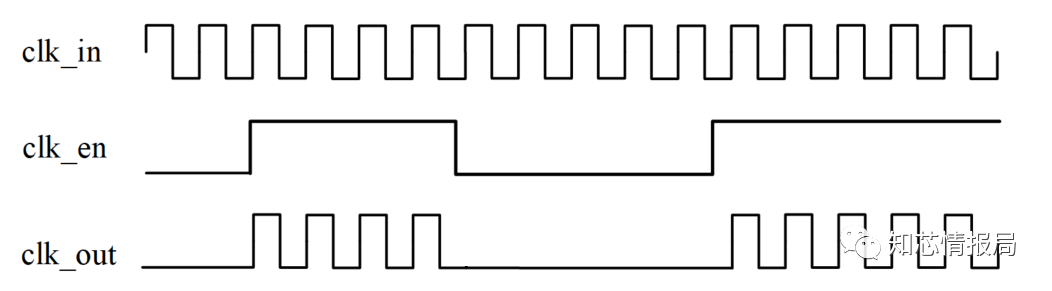

对于时钟源clk_source经过一个额外的与门U2A,当clk_en为高时,clk_source能过通过到达U1A触发器,当clk_en为低时clk_source无法到达触发器。当clk_en为低时,触发器及其时钟网络中的所有组合逻辑停止翻转,out端保持不变。由于clk_source经过了U2A与门,所有会产生一定的时钟偏移。在波形分析上,下面这个图可以比较好的理解门控时钟的概念,只有当clk_en为高的时候,clk_out=clk_in,否则,clk_out=0。

cg方法1:使用与逻辑

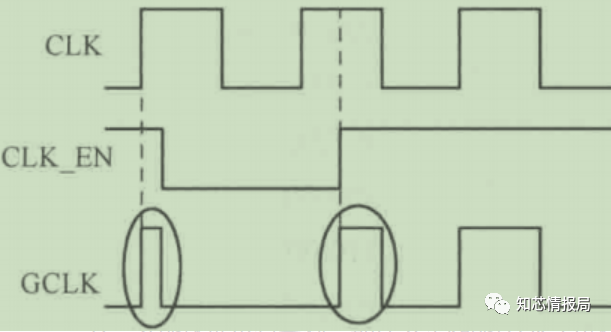

这个也是最简单的方法,直接将时钟使能控制(门控)信号与时钟做"与"逻辑。这个办法简单粗暴,但是也有一个严重的缺点:会有毛刺。当clk为低的时候,clk_en可任意变化,gclk都是低。但当clk为高的时候,clk_en必须保持不变,才能保证没有毛刺,那什么东西能让clk_en保持不变呢?答案就是:锁存器

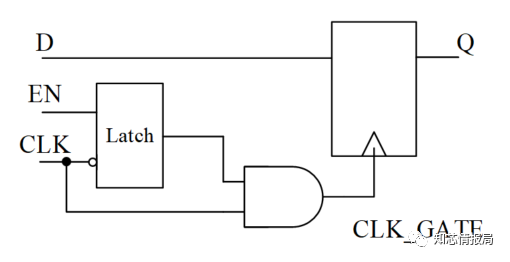

cg方法2:加入锁存器

在clk为低时锁存器连通、clk为高时锁存器锁住,如下图:

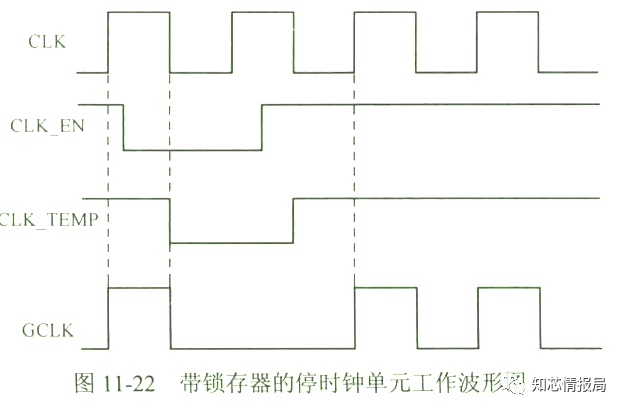

波形图如下,可见当clk为低的时候gclk为低没跑,但clk为高的时候,gclk的值可看作是clk上升沿采样的clk_en的值。所以使用Latch可以有效地锁存clk_en值,同时不影响clk的周期性。Latch门控时钟的本质是clk上升沿锁住了clk_en值,让clk为高时clk_temp不会翻转,所以消除了毛刺。

其RTL代码如下:

always@(*) beginif(clk)clk_temp = clk_en;elseclk_temp = clk_en;endassign gclk = clk & clk_temp;

cg方法3:使用标准单元库

虽然使用 latch 可以解决门控时钟毛刺的出现,但是时序也需要严格的约束。FPGA 或 IC 设计时,综合库中往往会有集成门控逻辑单元。此类门控逻辑单元经过了大量的更新迭代和验证,使用起来更加的方便、安全。因此一般情况下,门控时钟的设计也都会直接调用专用的集成门控逻辑单元。调用方式和基本的与门、缓冲器等基本单元类似,直接例化即可。

审核编辑:汤梓红

-

请问stm32不进入低功耗模式怎么降低功耗?2019-05-06 0

-

cogobuy降低功耗的措施2012-03-23 0

-

降低低功耗蓝牙的功耗2012-03-29 0

-

CC2530 如何降低ZC发现网络的频次以降低功耗?2016-04-07 0

-

vs1053如何降低功耗2016-08-10 0

-

IC芯片功耗有哪些降低方法?2017-06-29 0

-

如何利用FPGA满足电信应用中的降低功耗要求?2019-07-31 0

-

如何降低ZC发现网络的频次以降低功耗?2020-08-07 0

-

提高功率降低功耗的方法2021-02-26 0

-

寄存器传输级低功耗设计方法2011-02-16 1468

-

降低威廉希尔官方网站 漏电功耗的低功耗设计方法2020-09-16 11552

-

低功耗蓝牙芯片的应用可显著降低功耗和成本2021-03-05 1212

-

华润微CS88M312芯片降低功耗方法与使用注意事项2021-10-12 661

-

FreeRTOS如何降低功耗2023-07-30 995

-

如何降低设备功耗,降低采集设备功耗的几种方法2023-10-11 1581

全部0条评论

快来发表一下你的评论吧 !