搭建一个通用MicroBlaze最小系统+一个外设

处理器/DSP

描述

MicroBlaze是AMD-Xilinx提供的一个可以在FPGA中运行的嵌入式软核IP,其本质是一个32位RISC处理器软核,可以在150MHz时钟下,提供125 D-MIPS性能,具有运行速度快、占用资源少、可配置性强等优点。

今天主要是搭建一个通用MicroBlaze最小系统+一个外设,最后固化程序到FPGA。

缩略词索引:

MB-MicroBlaze

环境平台

win10 vivado 2020

Vitis 2020

FPGA部分搭建

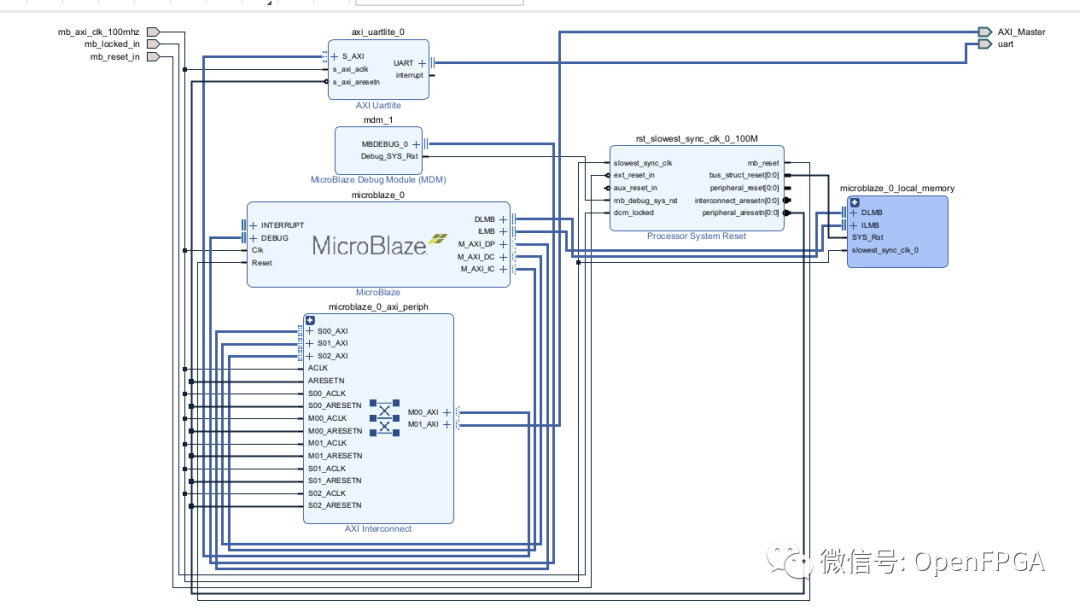

一个完整的MB系统,包括四个方面:CPU、时钟、 DDR 和外设,其中CPU不用说就是MB,DDR不是必须的,根据硬件选择,如果没有DDR时候选择内部RAM使用需要选择大一点,所以下面分成两种情况建立最小系统。

不带DDR的MB最小系统-通用系统

第1步

搭建Vivado系统,不过多赘述了!

第2步

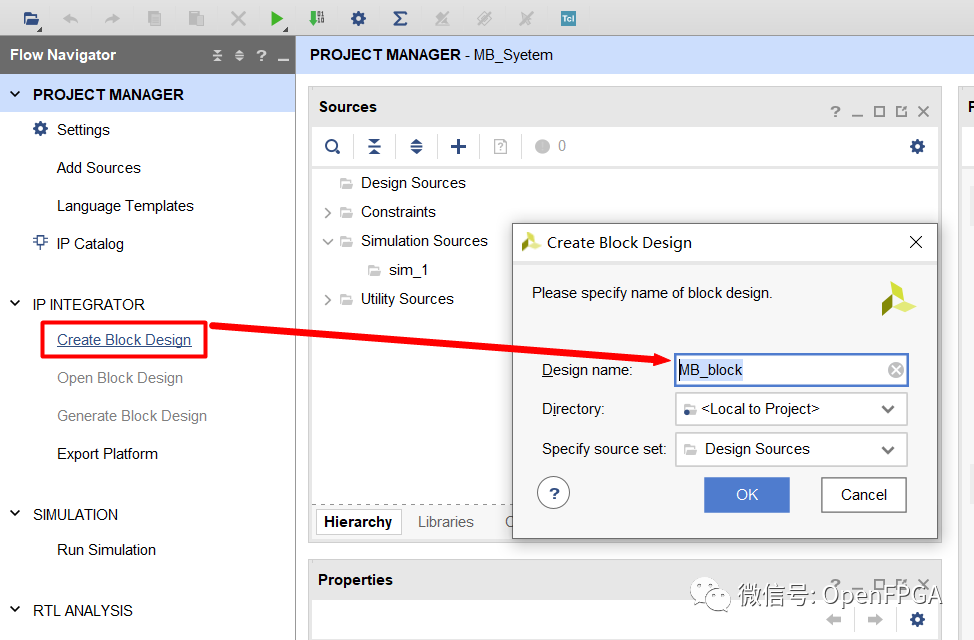

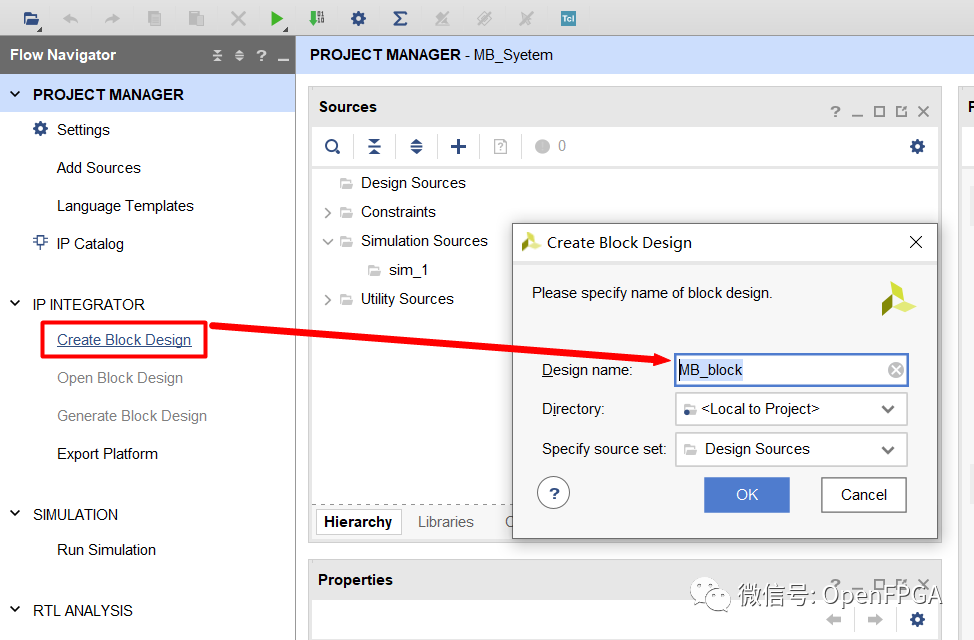

点击 Create Block Design,创建一个 BD 文件,并命名为MB_block。

第3步

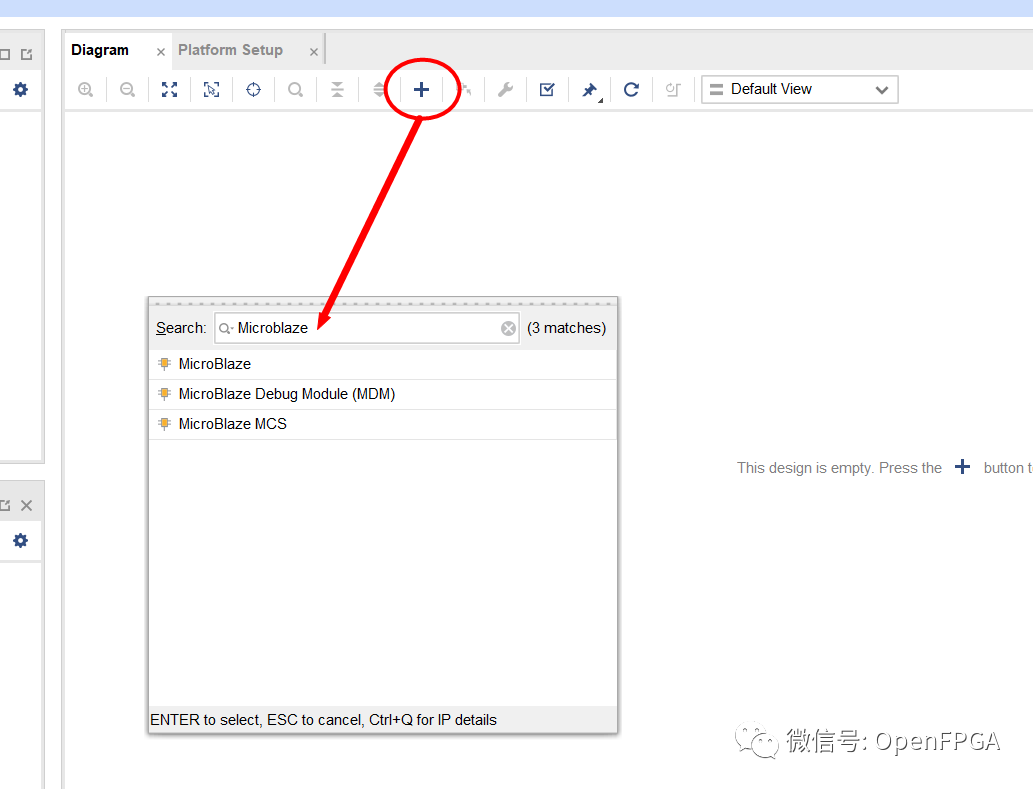

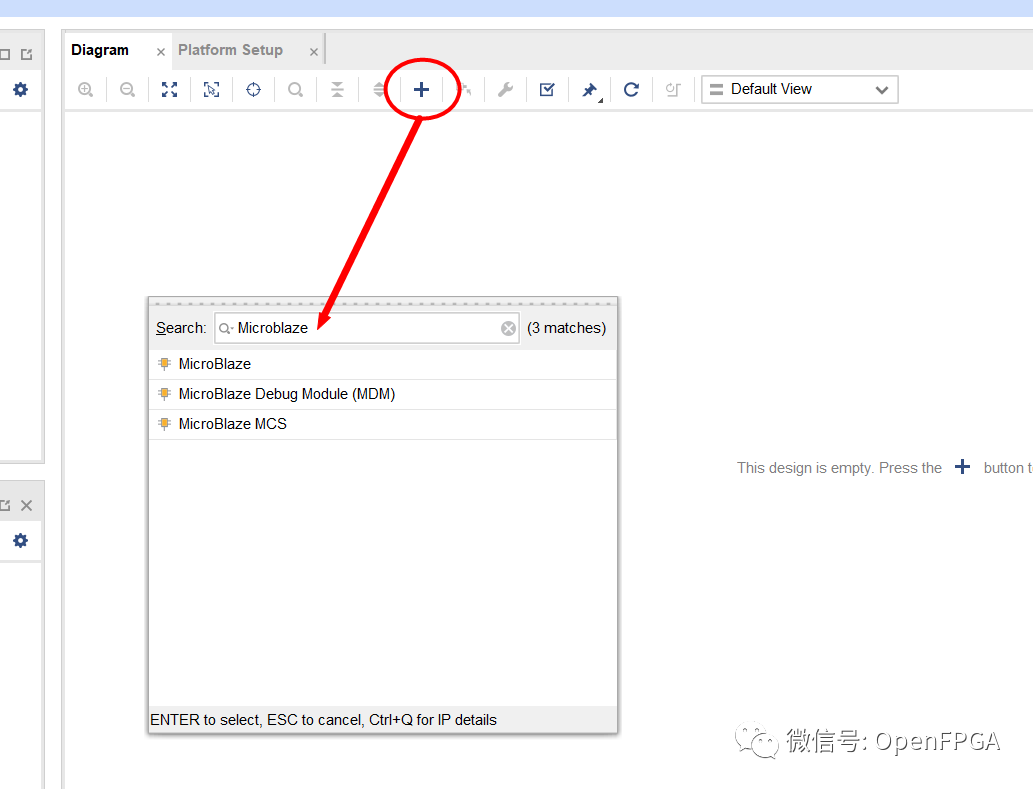

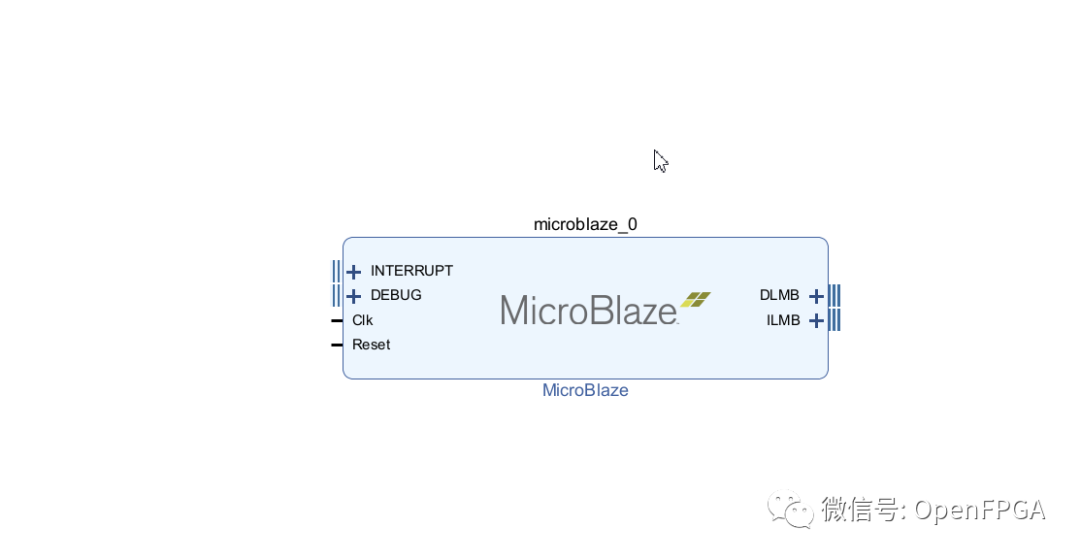

单击添加 IP 图标,然后输入关键字 MicroBlaze。

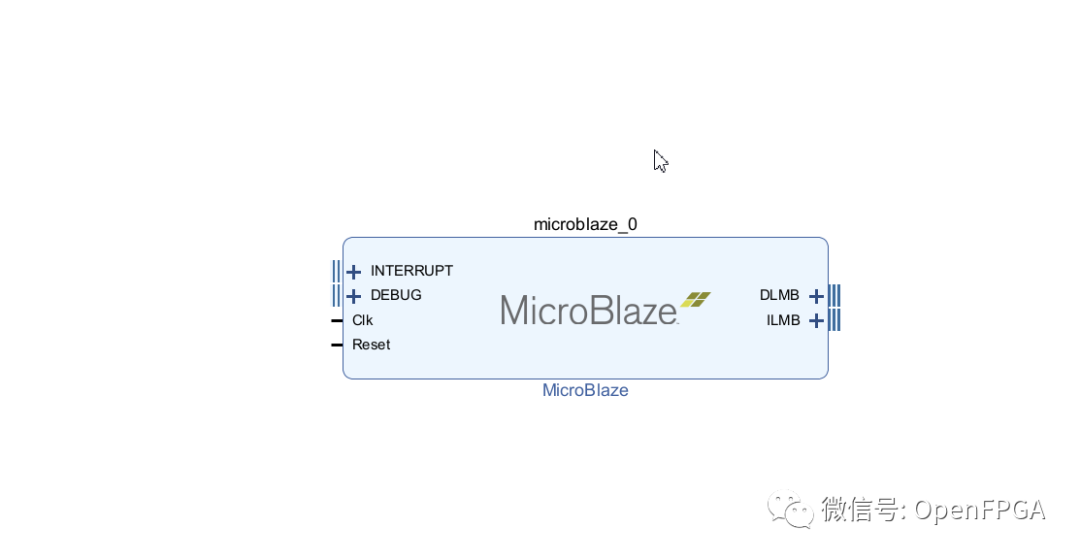

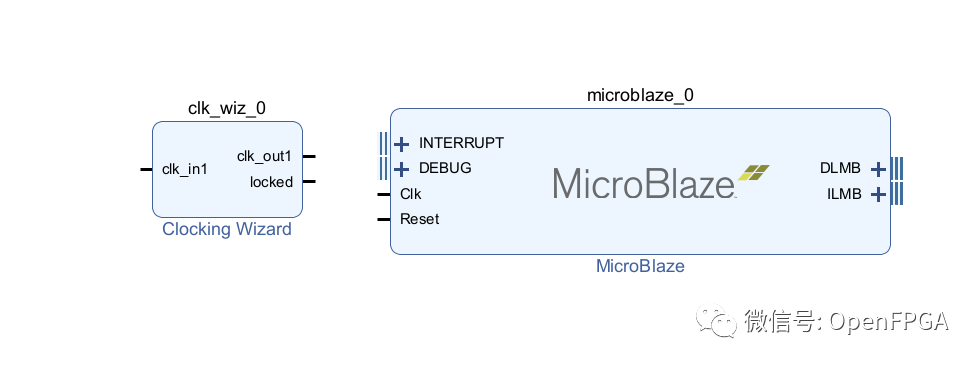

双击将MB添加到 BD 文件中:

第4步

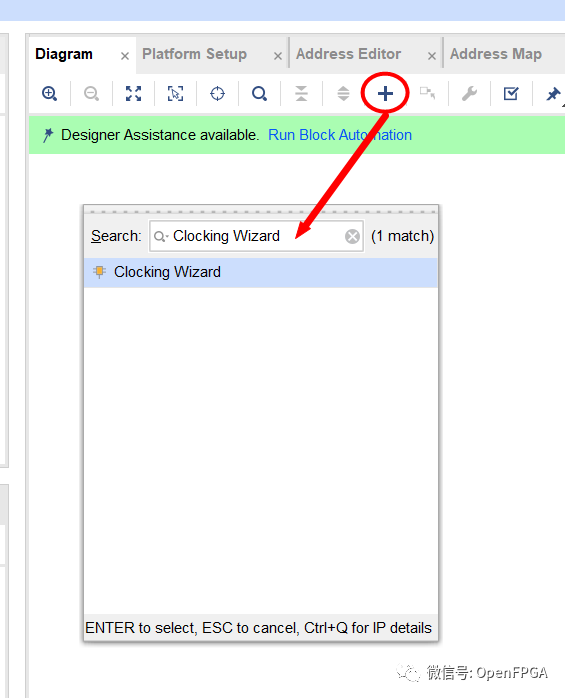

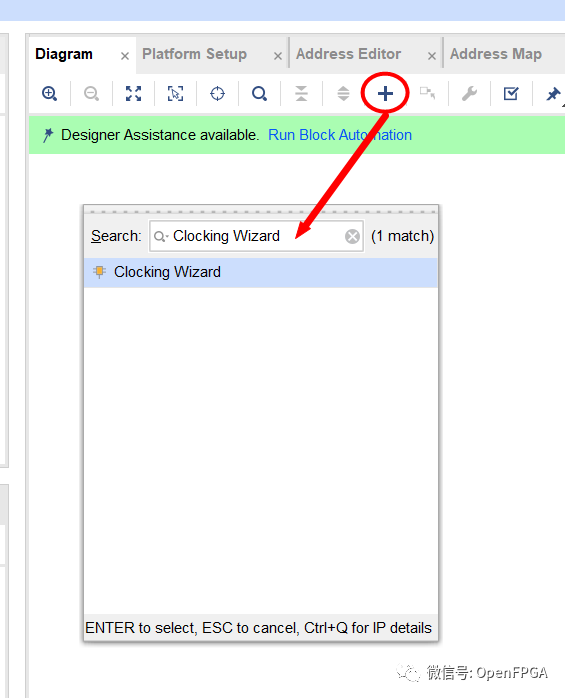

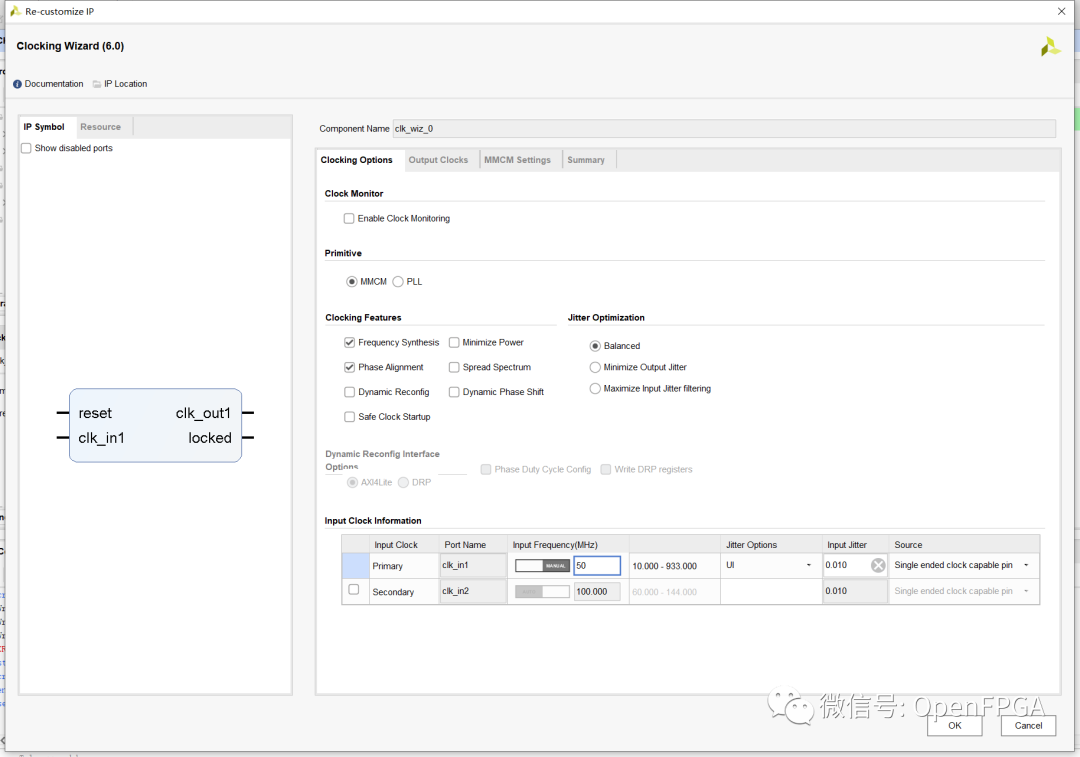

添加时钟,在添加IP图标位置输入关键字Clocking Wizard。

双击将Clocking Wizard添加到BD文件中。

第5步-此步可不加

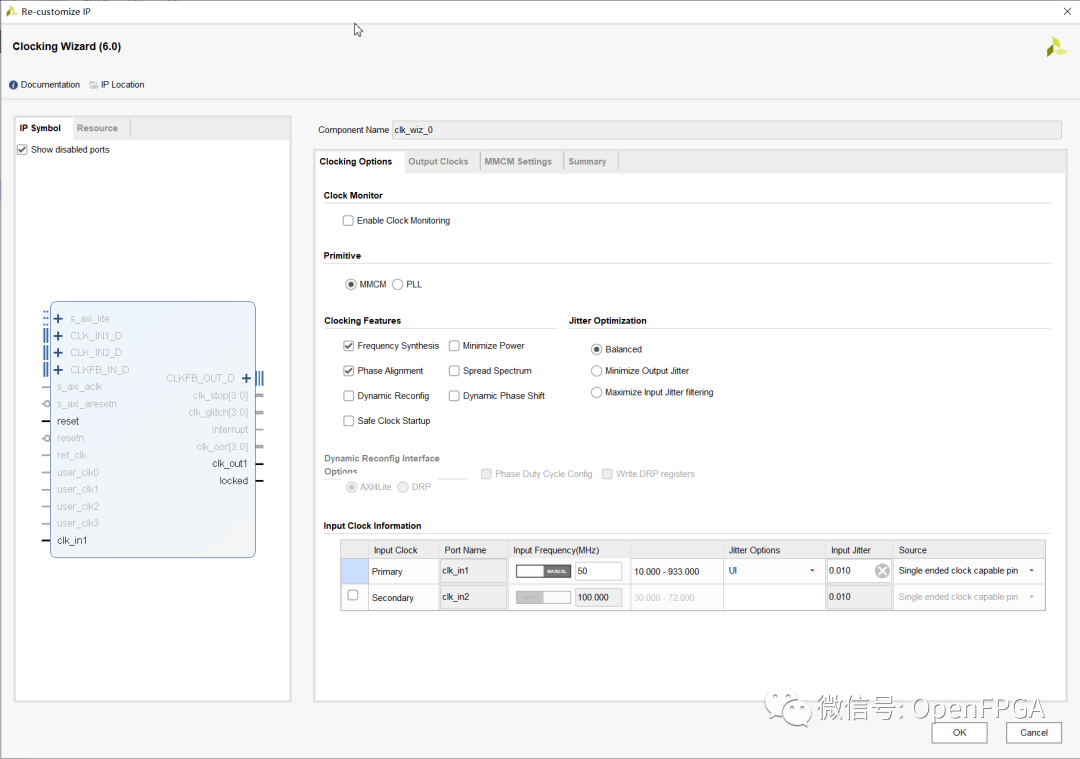

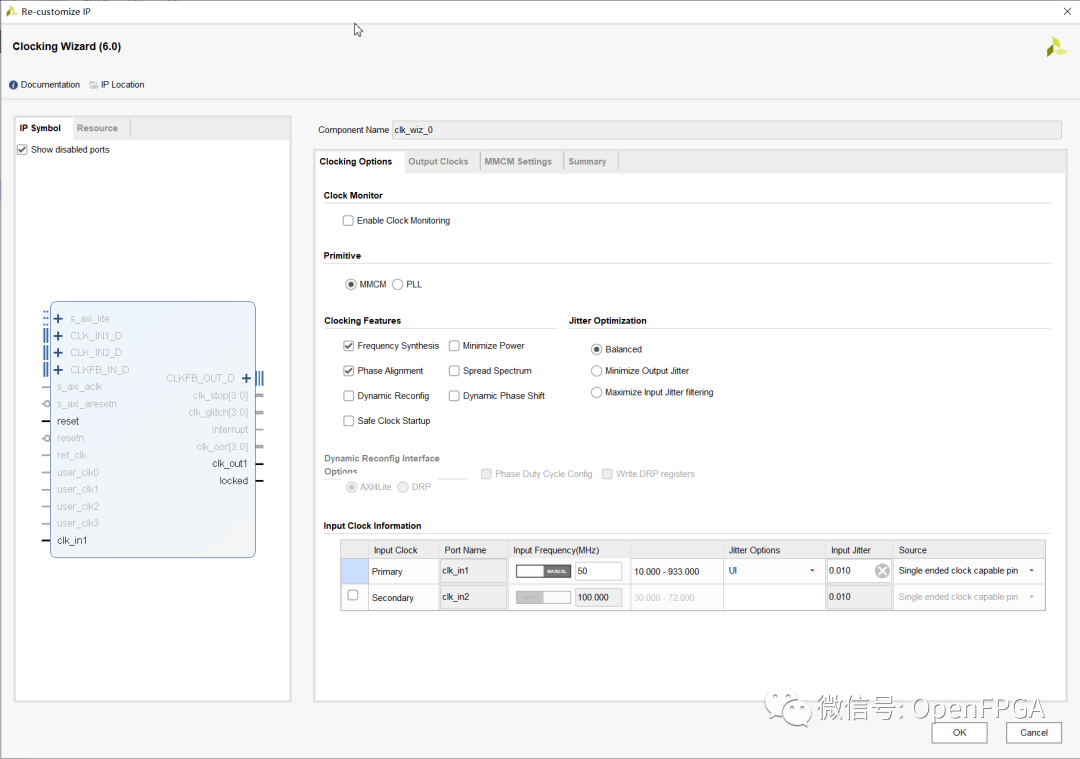

时钟设置,双击Clocking Wizard对时钟进行配置。

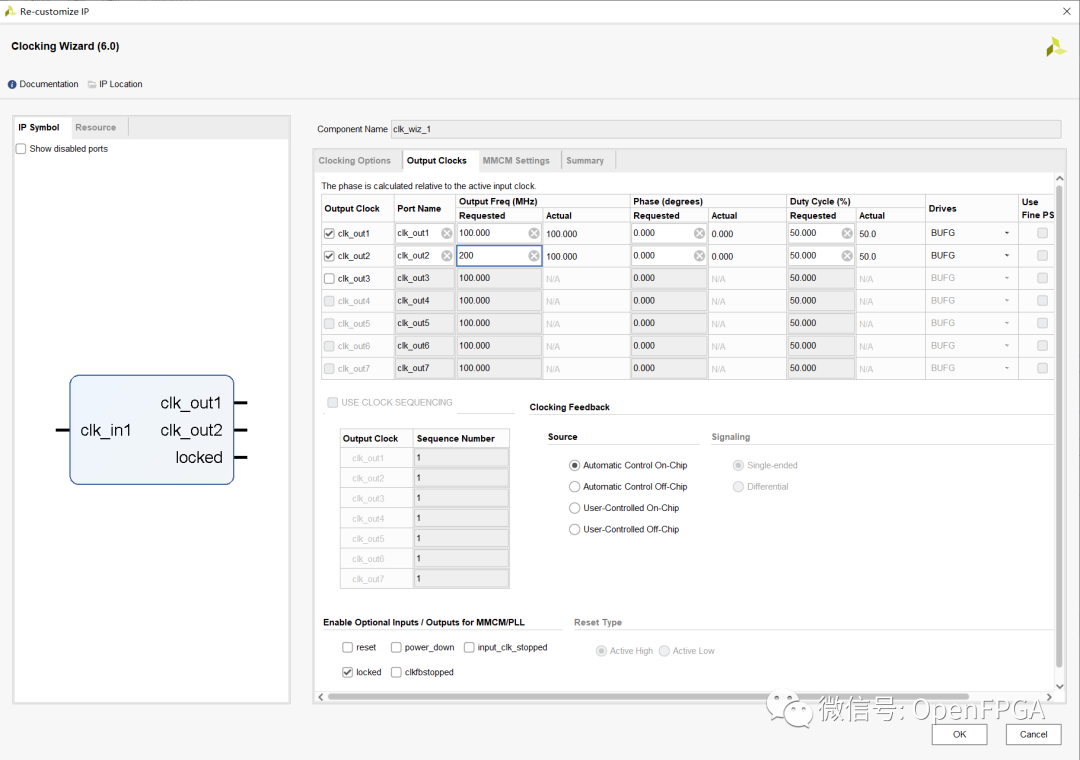

输入时钟根据硬件进行选择,我的硬件是一个单端50MHz时钟,输出时钟参数如下:

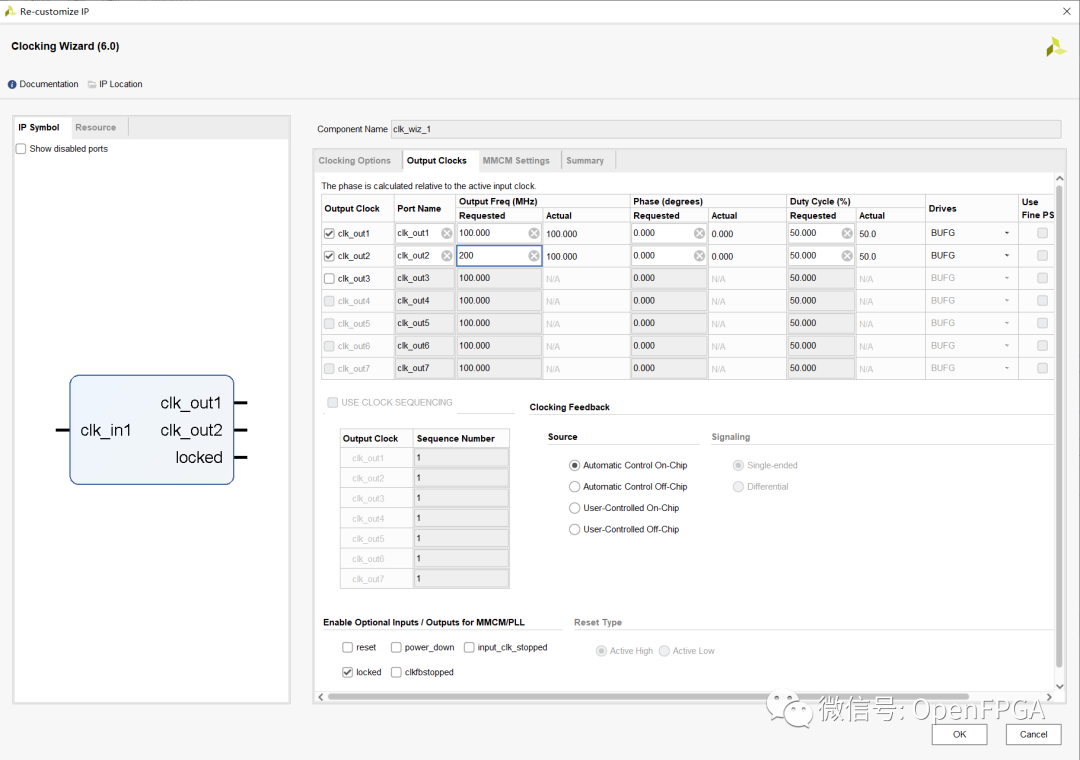

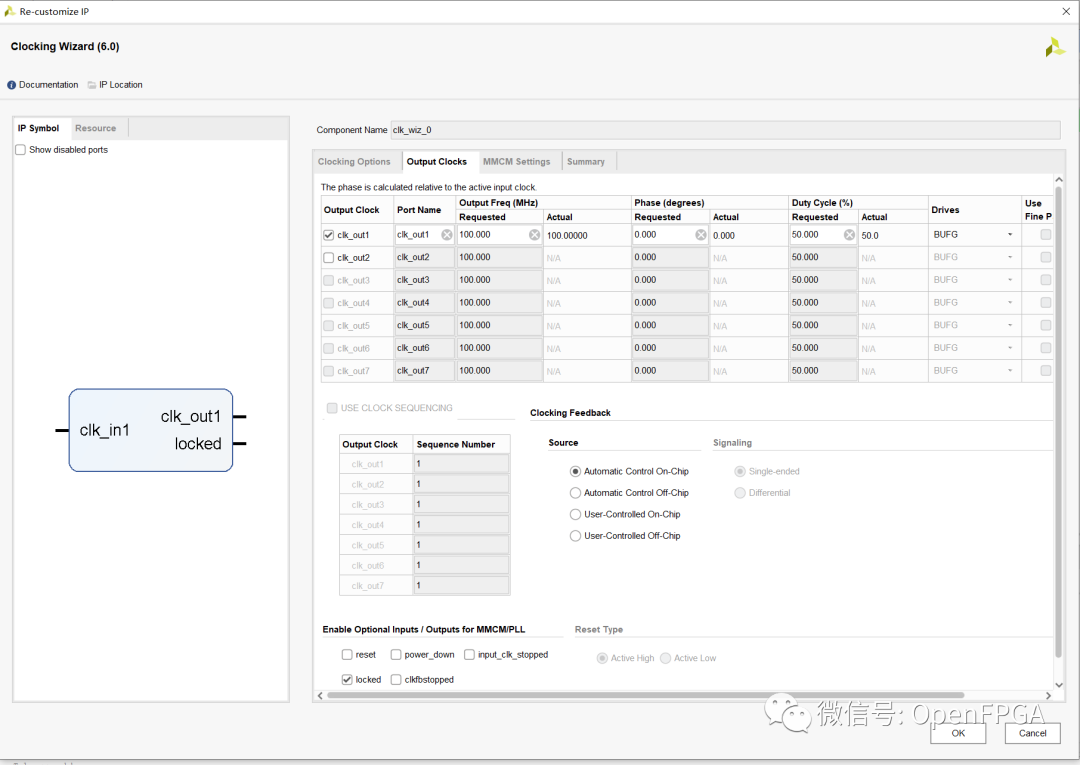

clk_out1作为MB的运行时钟,这里设置为100MHz,而clk_out2的200MHz是作为DDR控制器的运行时钟。

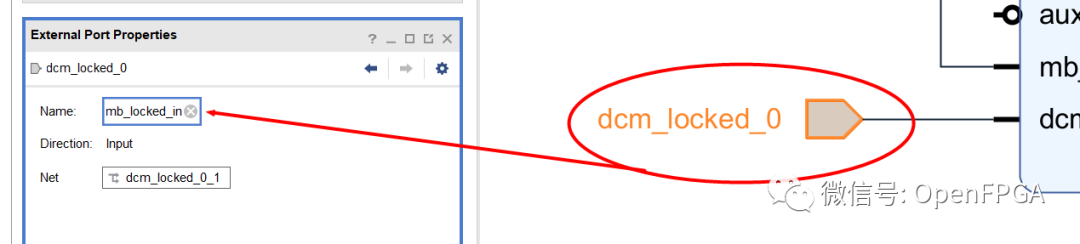

勾选locked作为后续威廉希尔官方网站 的复位信号。

其他页面默认即可,点击【OK】完成设置。

第6步

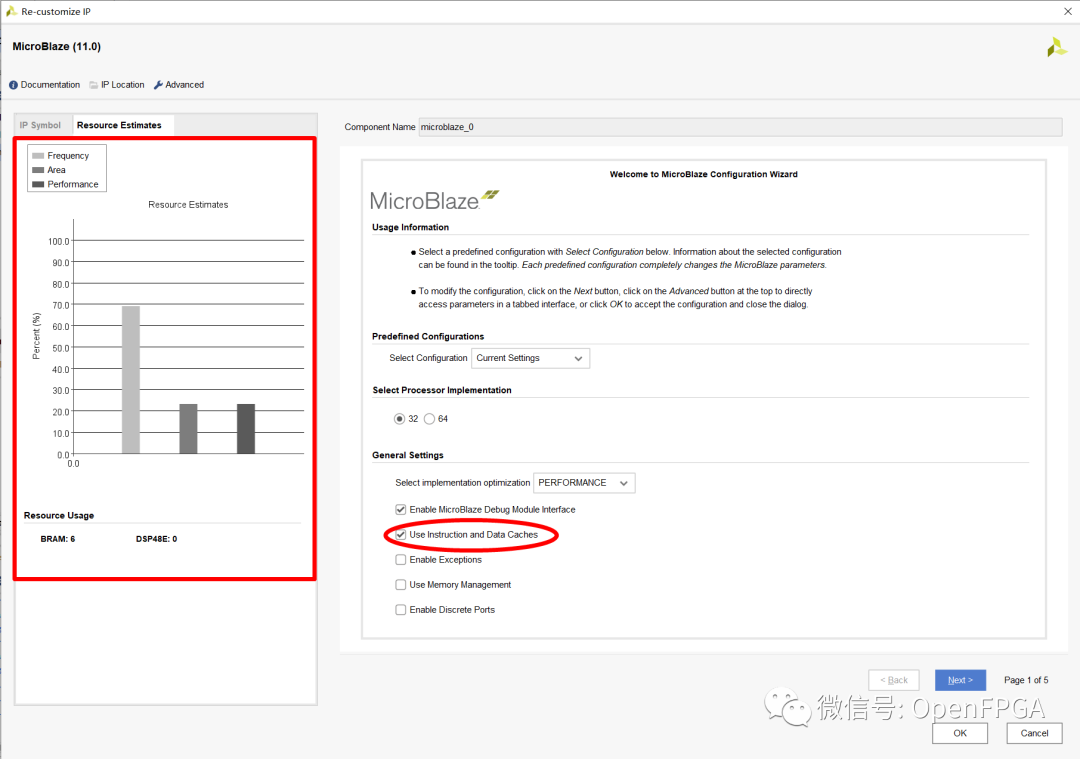

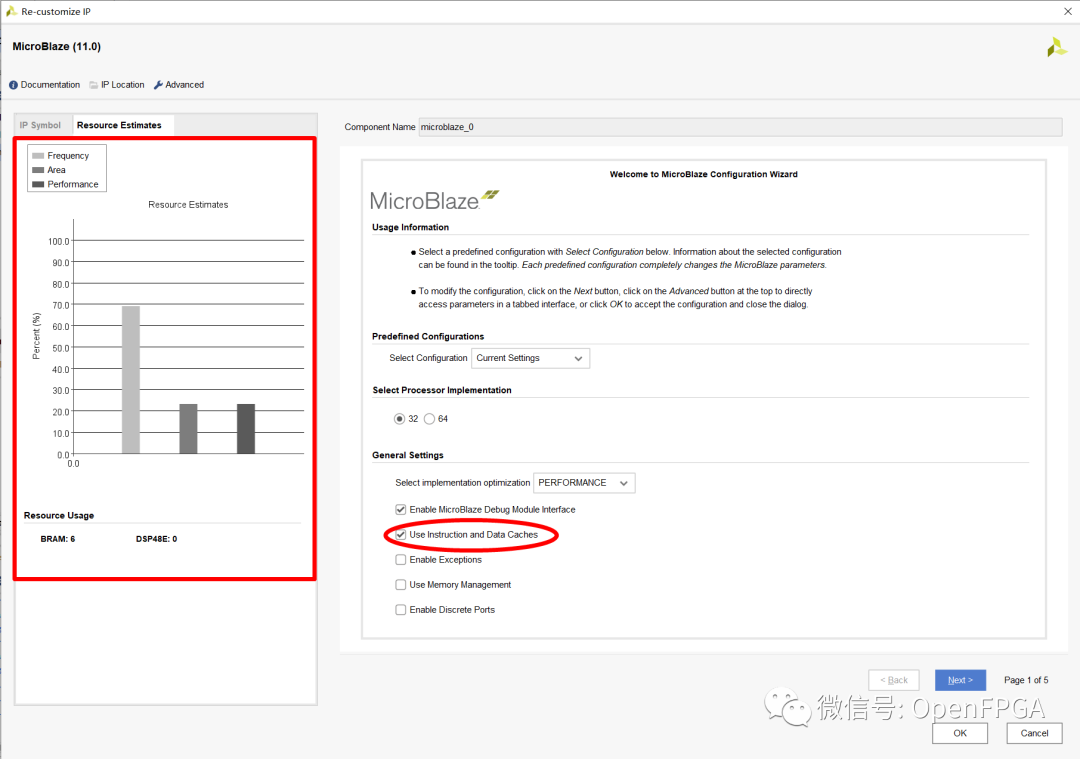

MB设置,在 BD 文件中,双击 MB 图标,对其进行配置,第一页配置参数如下图所示:

注意图中圆圈是需要勾选的,允许外部存储 BRAM 作为程序运行缓冲区,方框部分是软核的频率、面积和性能三方面的综合结果(三方不可同时兼得)。

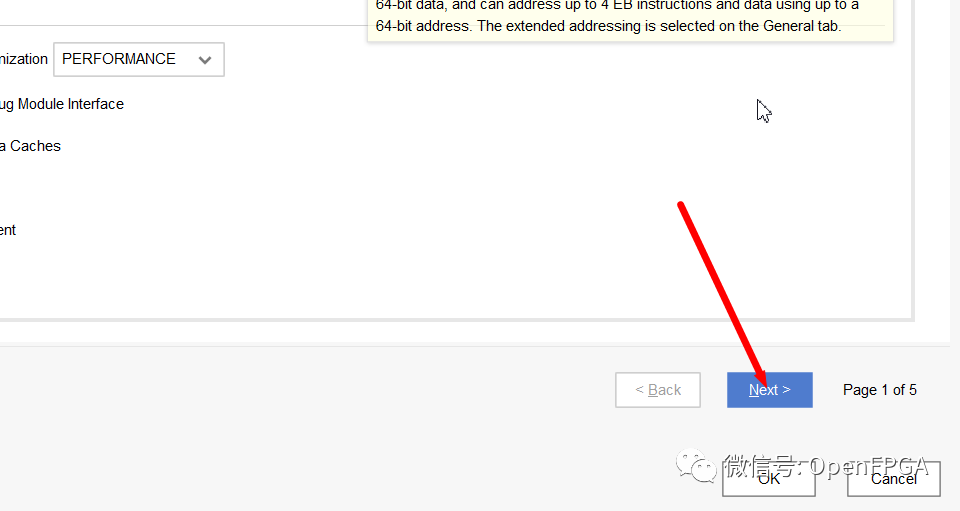

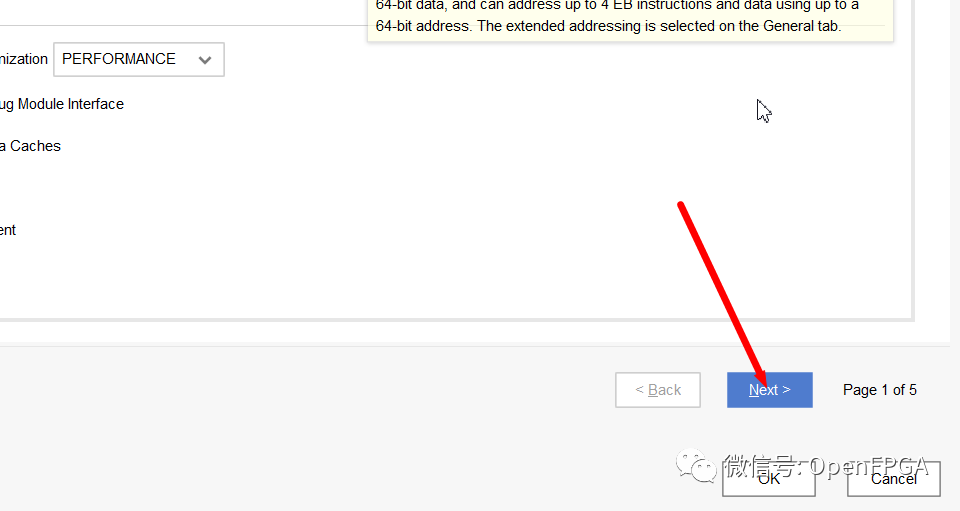

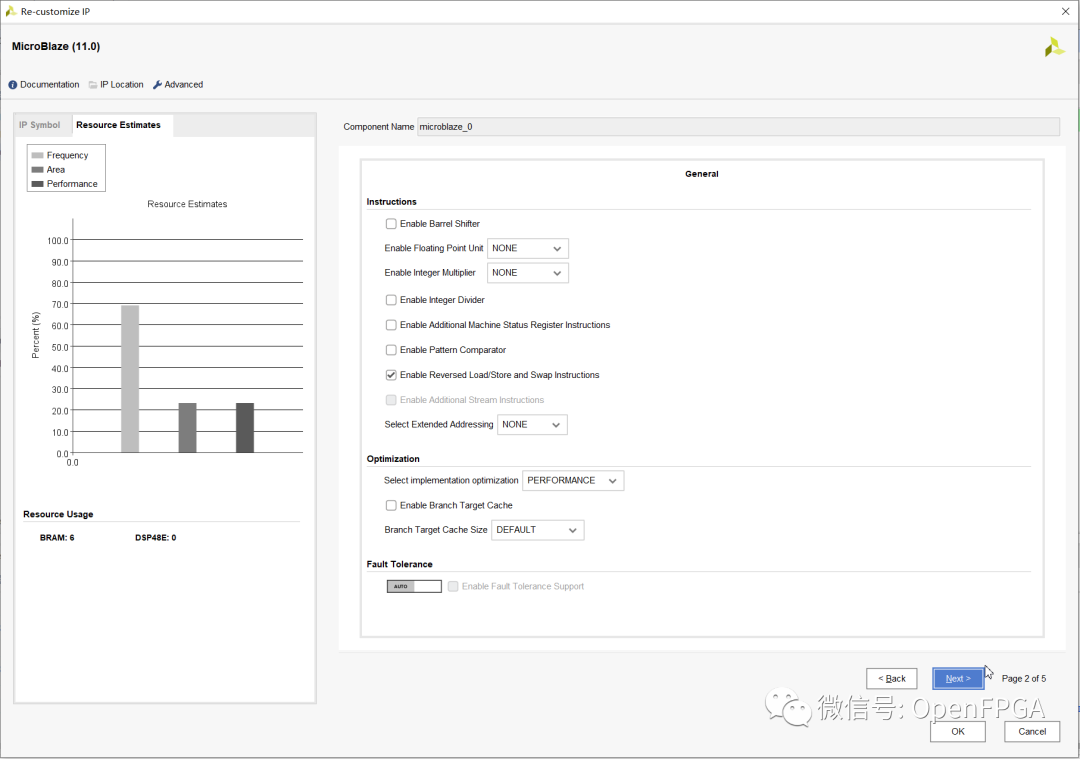

点击【Next】,进行下一界面进行设置:

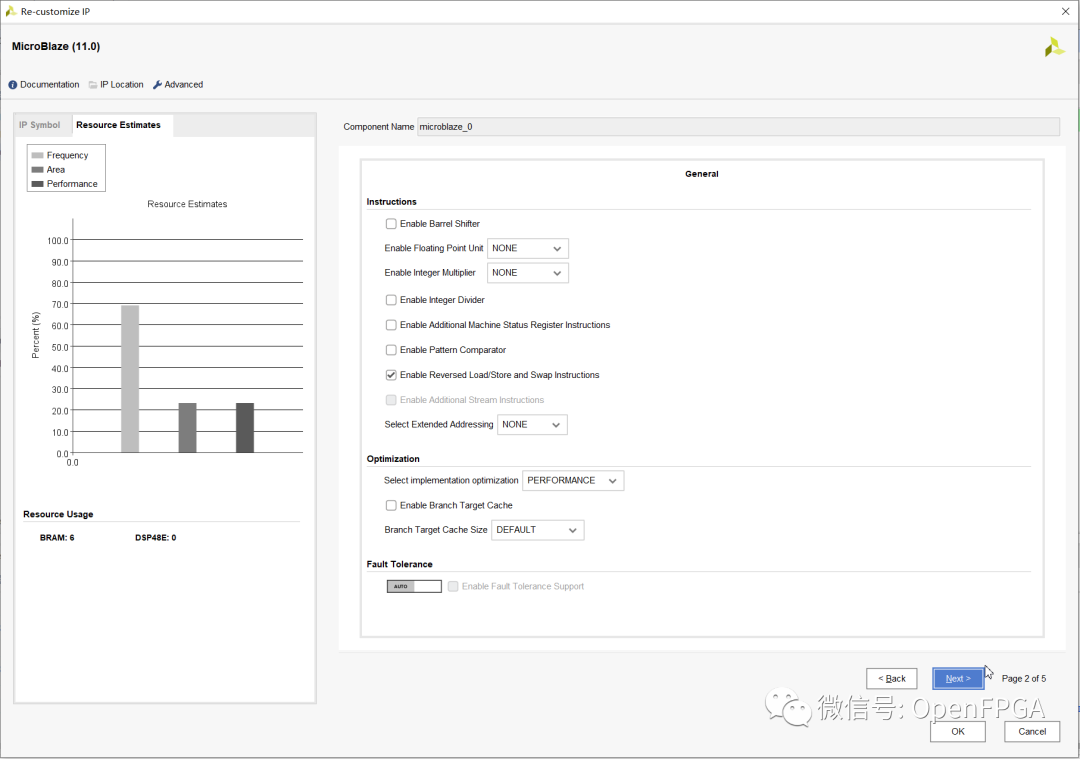

界面默认,点击【Next】:

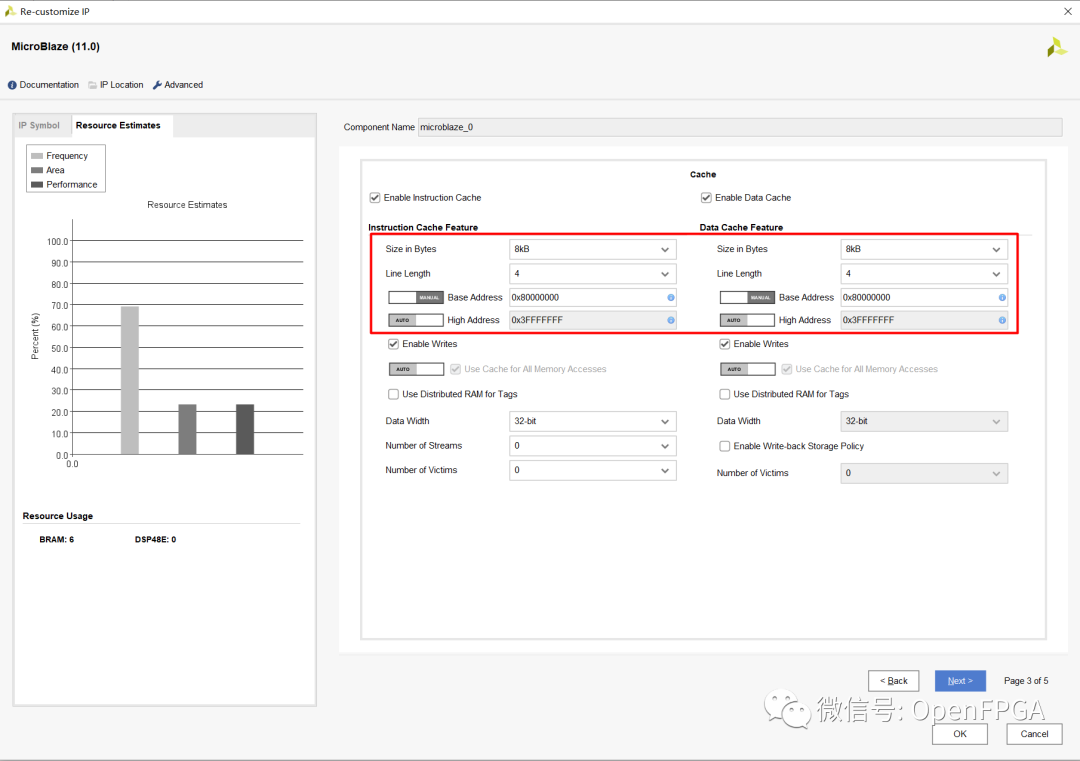

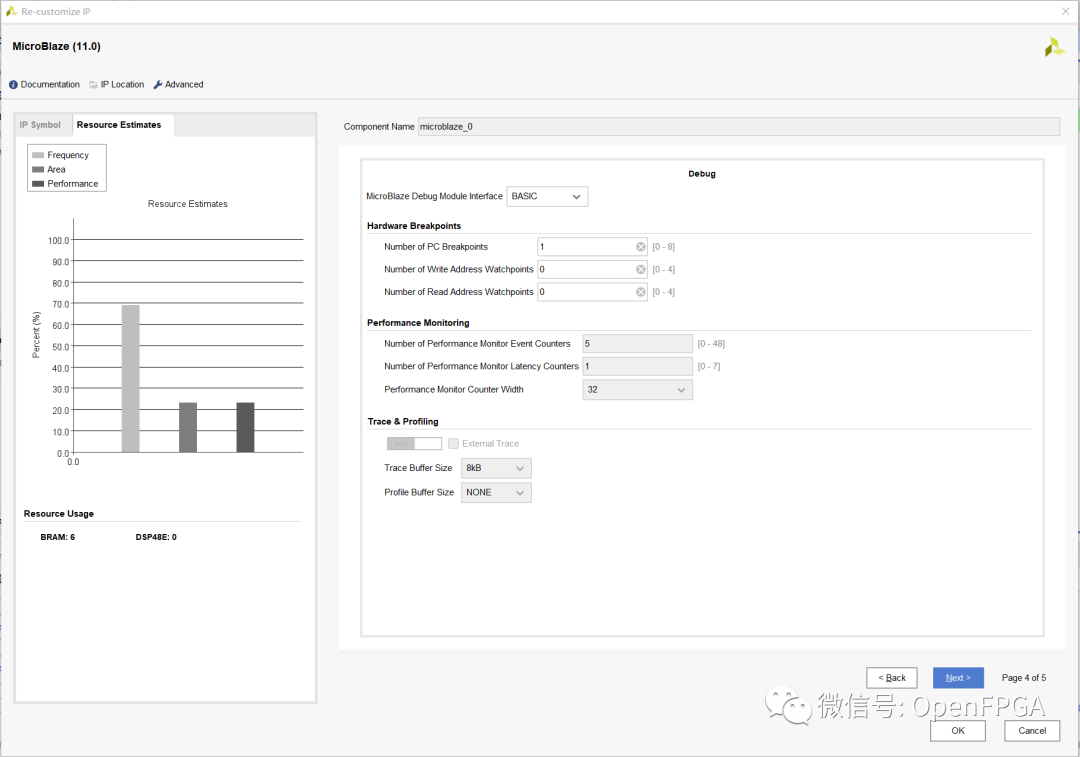

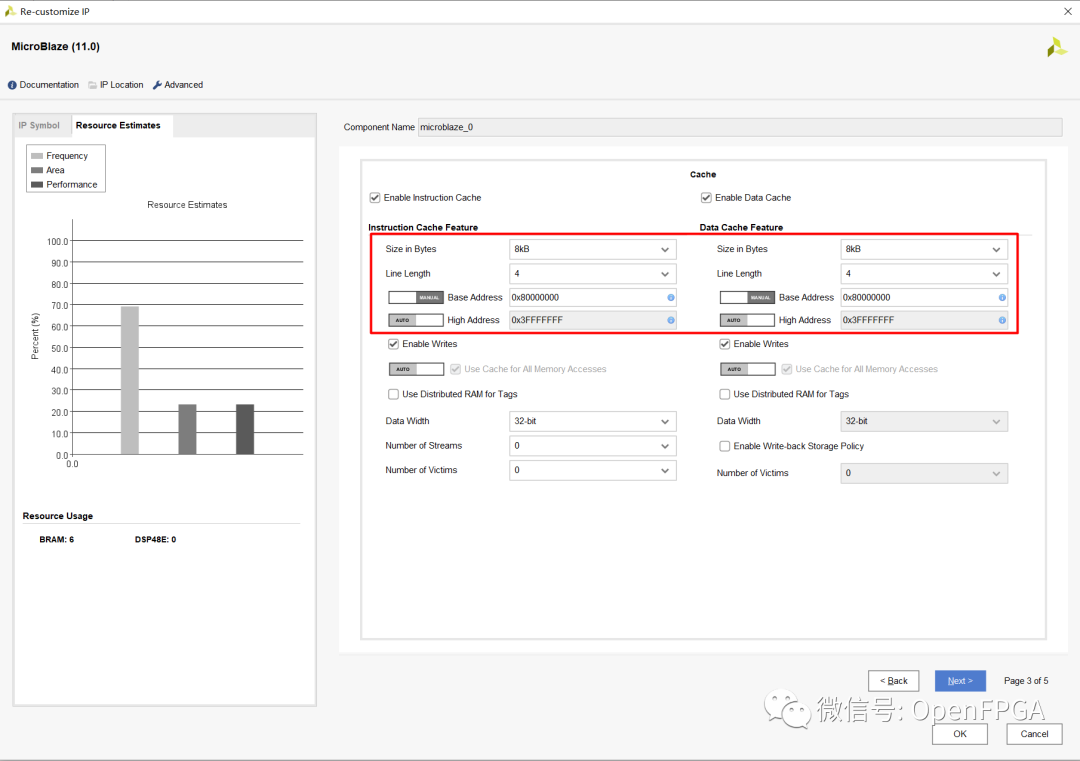

按照上图设置,点击【Next】:

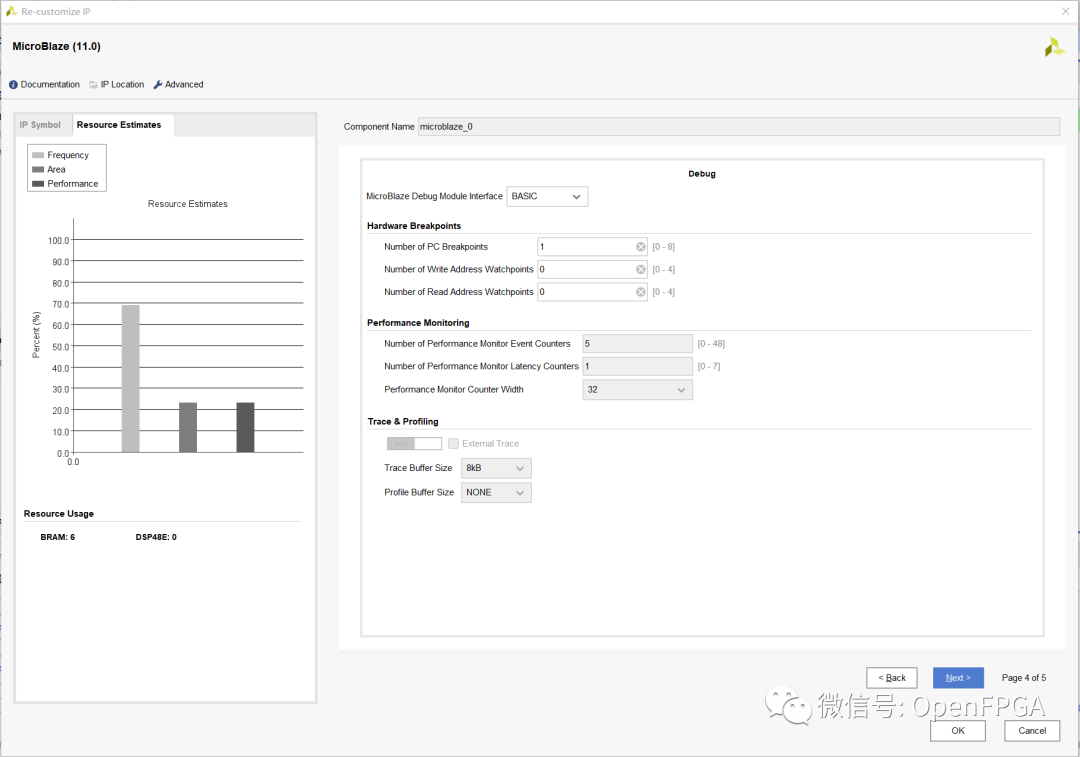

界面默认,点击【Next】:

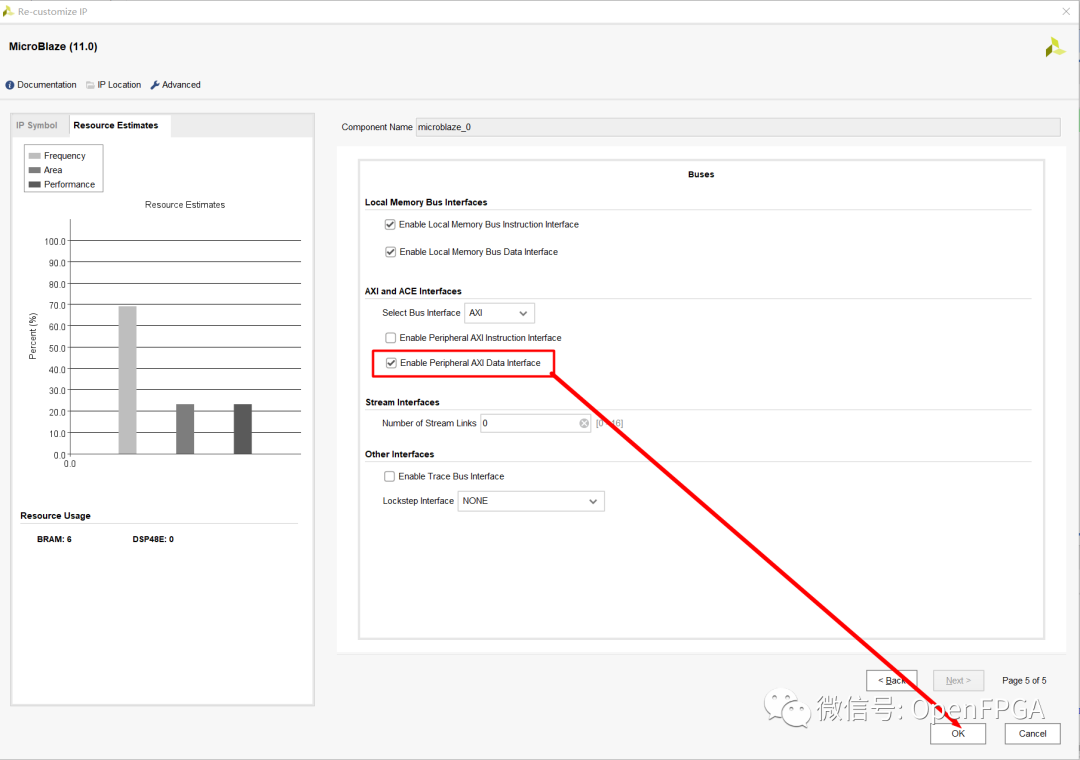

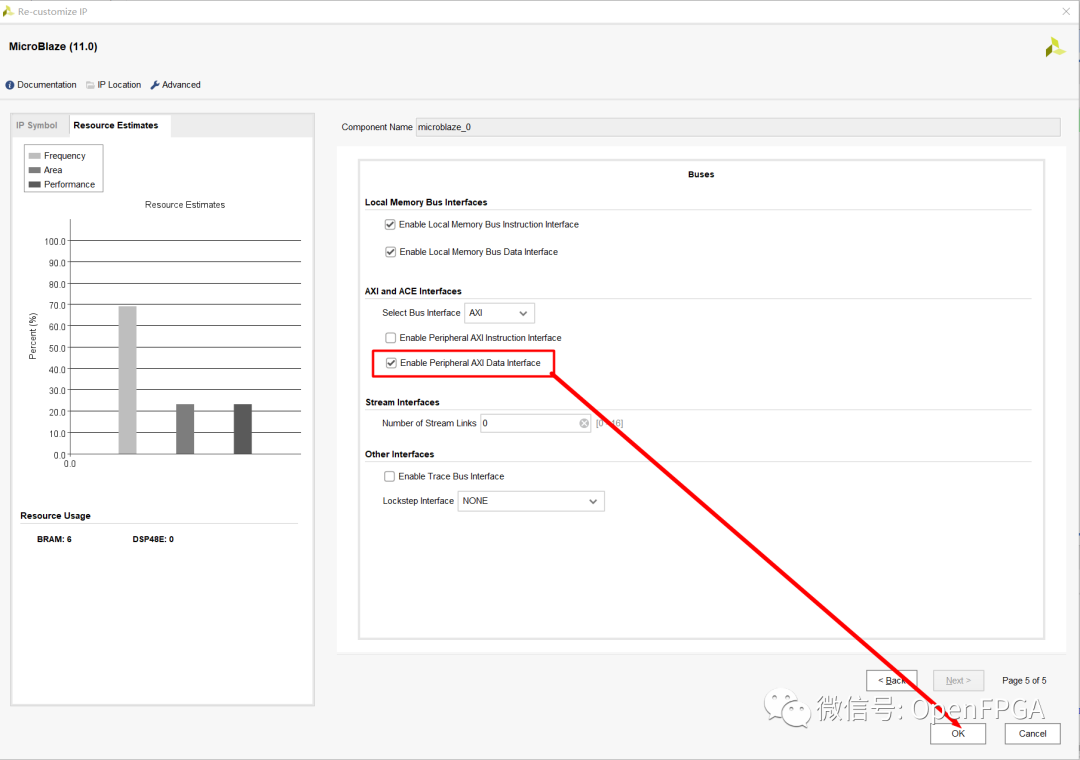

按照上图设置,允许 AXI 数据流。修改完成之后点击 【OK】 即可。

上面主要修改三个部分:第一页允许外部存储 BRAM 作为程序运行缓冲区;第三页设置Cache基地址和长度;第五页是允许AXI数据流,用来访问外部DDR。

第7步

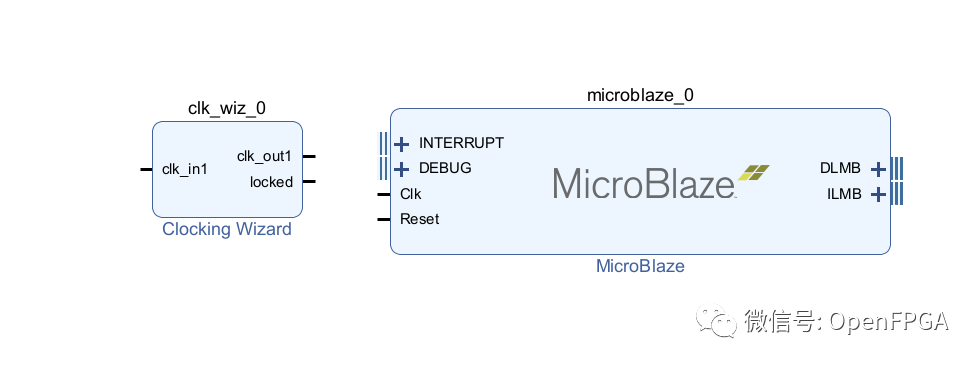

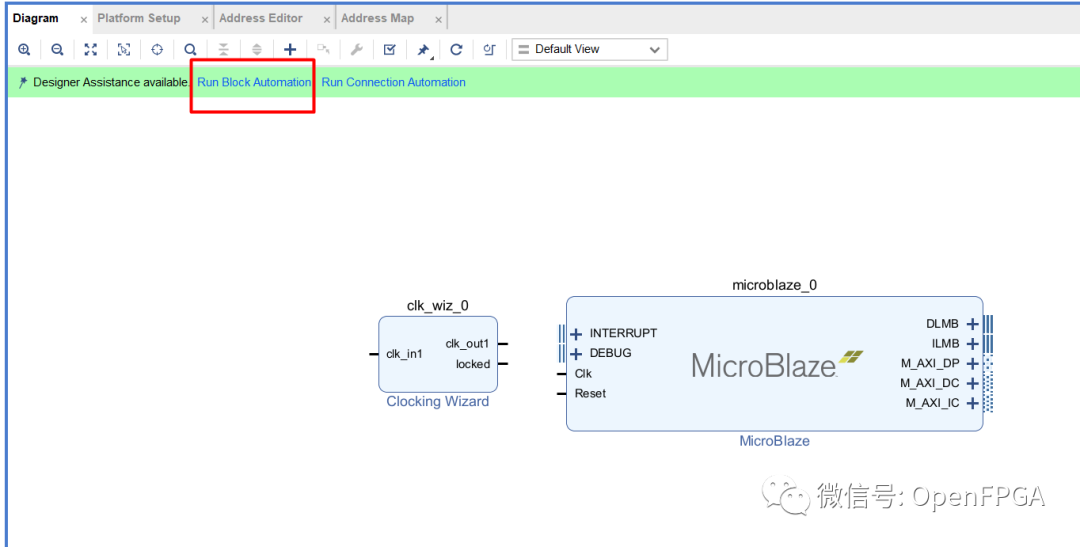

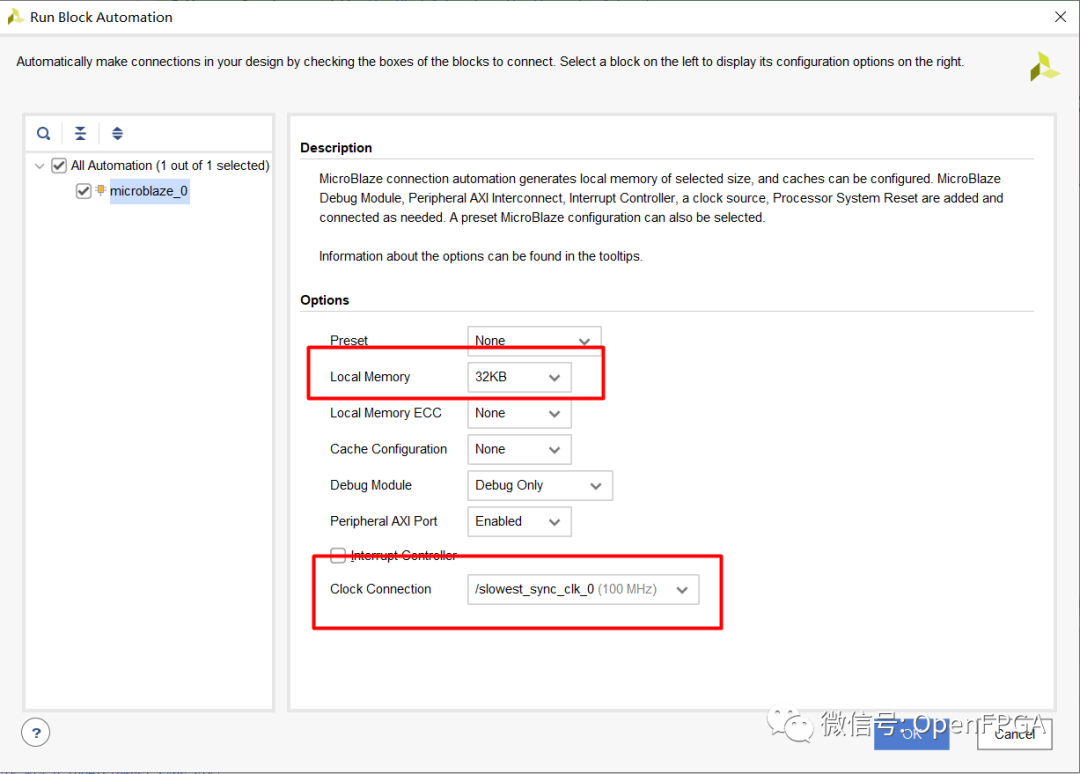

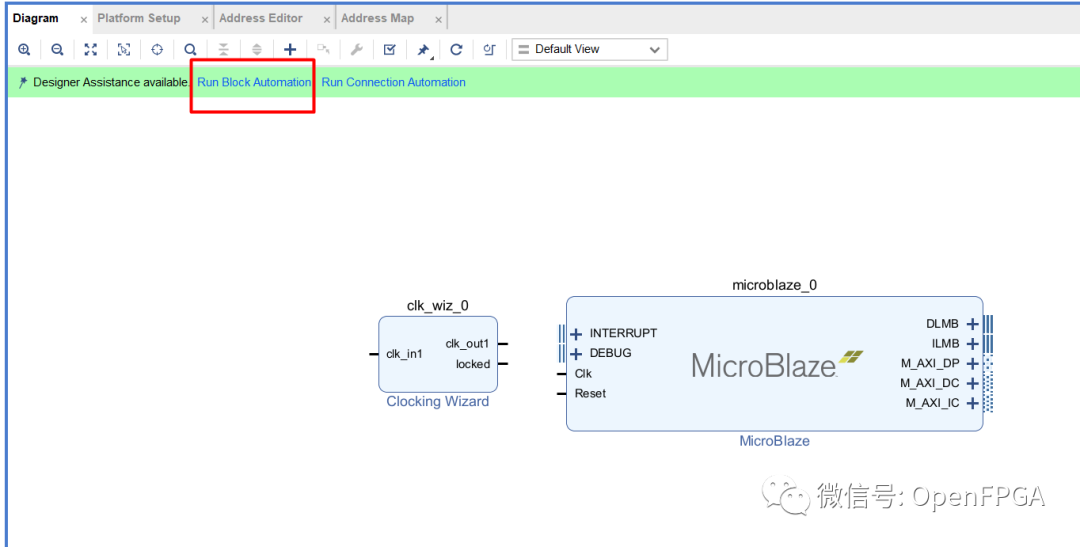

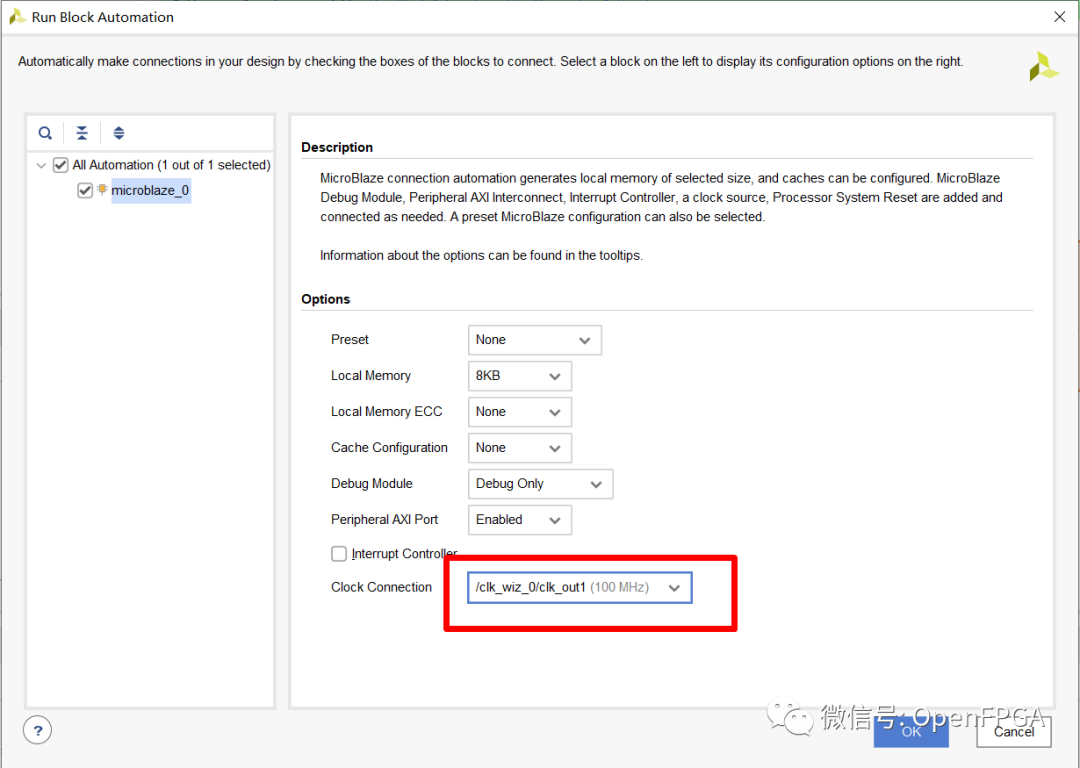

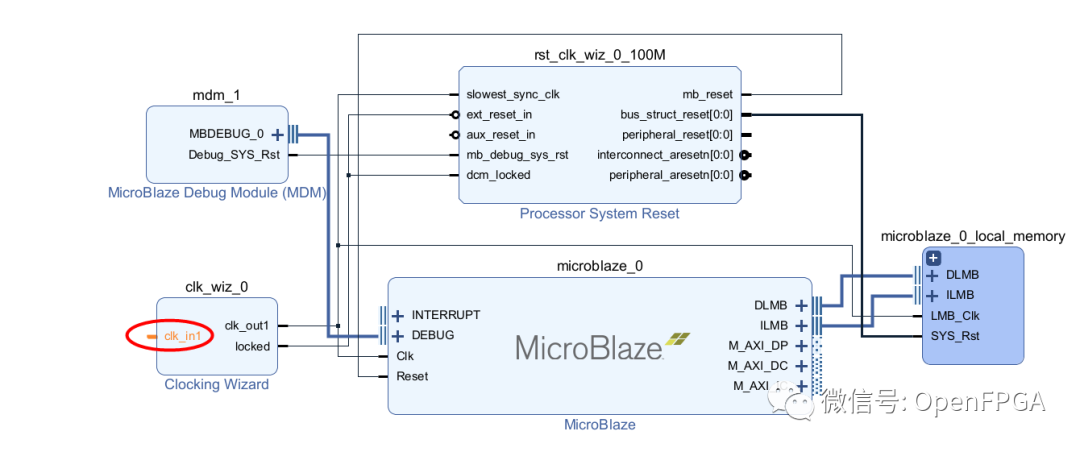

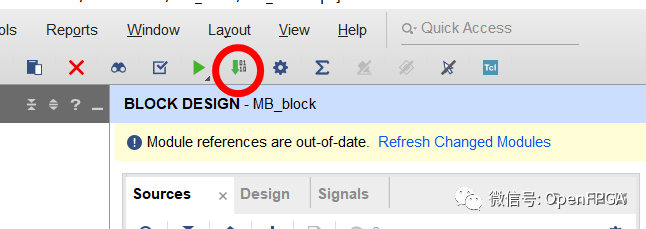

让BD自动完成设置,点击Run Block Automation完成剩下的设置。

弹出的界面默认即可,时钟使我们上面第4步Clocking Wizard生成的,Local Memory 选择 32KB,因为没有外部存储器。

第8步

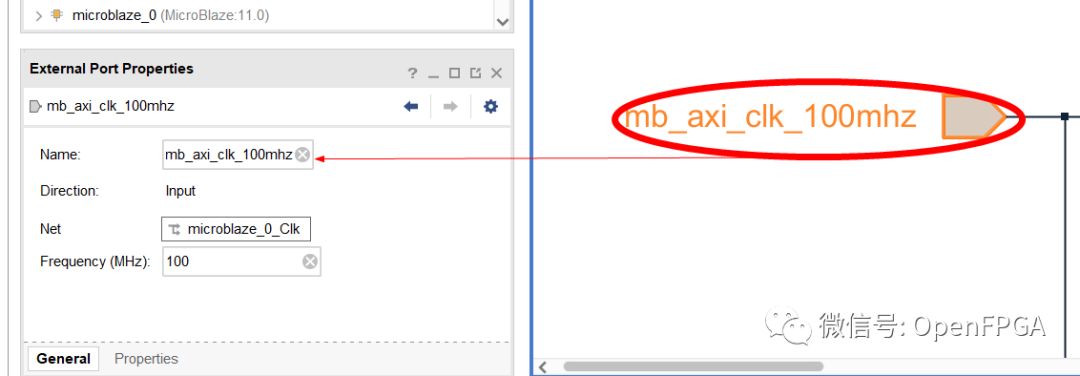

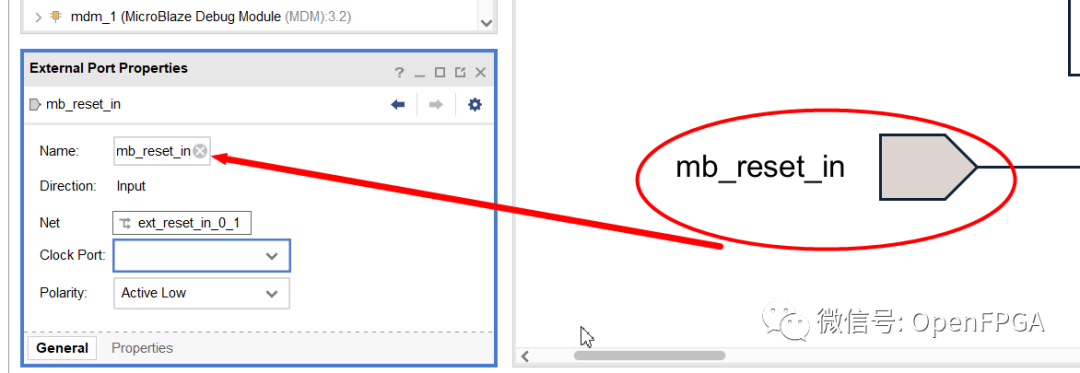

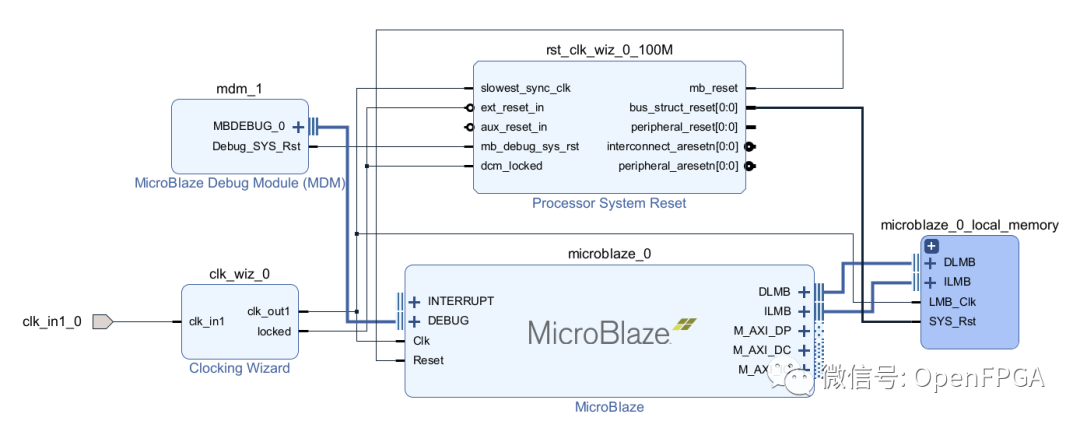

引出相关引脚。

组合键 【Ctrl+T】 引出引脚。

第9步

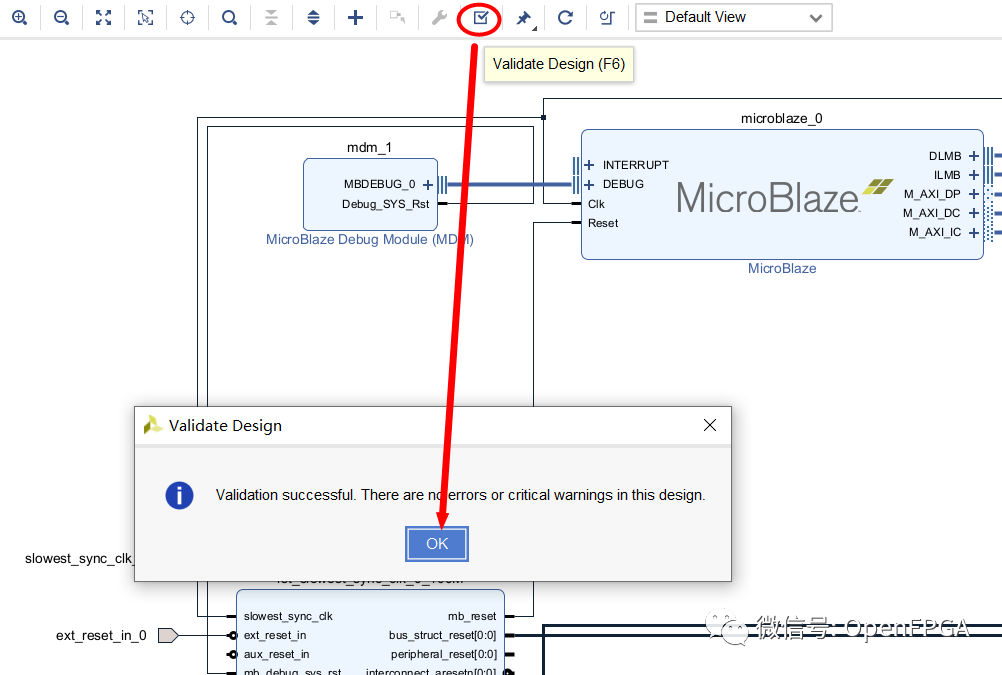

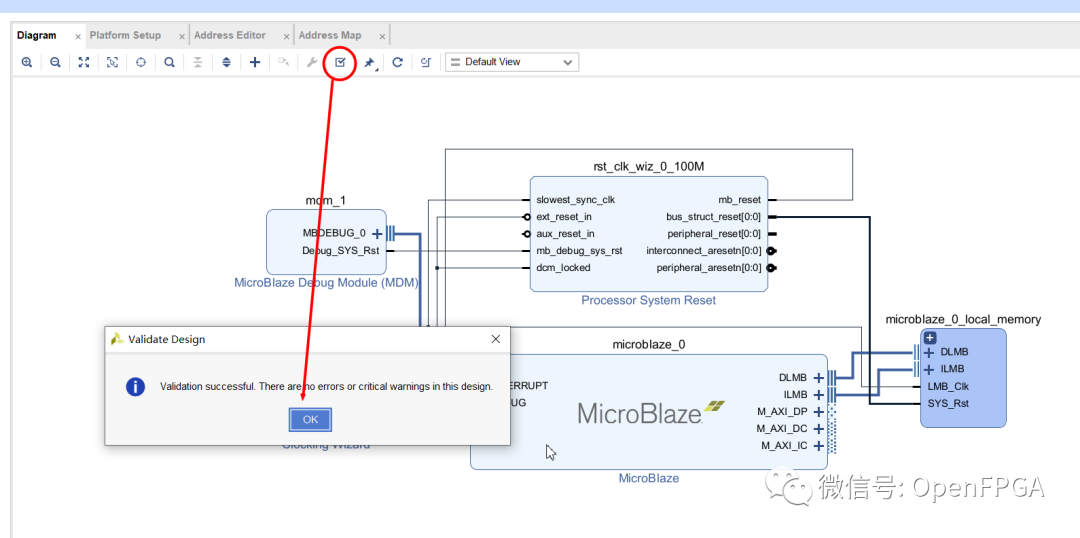

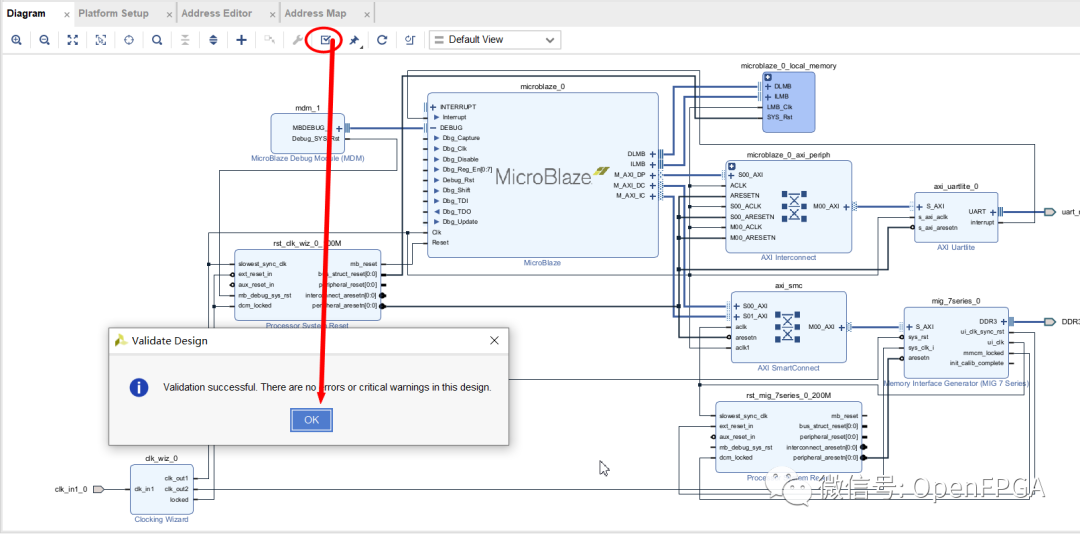

验证目前设计的正确性:

目前这一步已经完成了最小系统设计。

第10步

修改引脚名称。

第11步

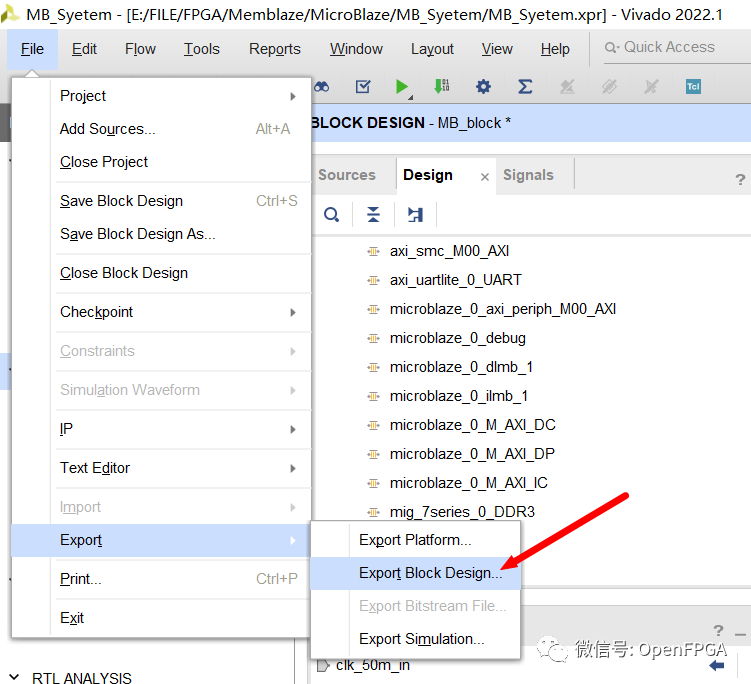

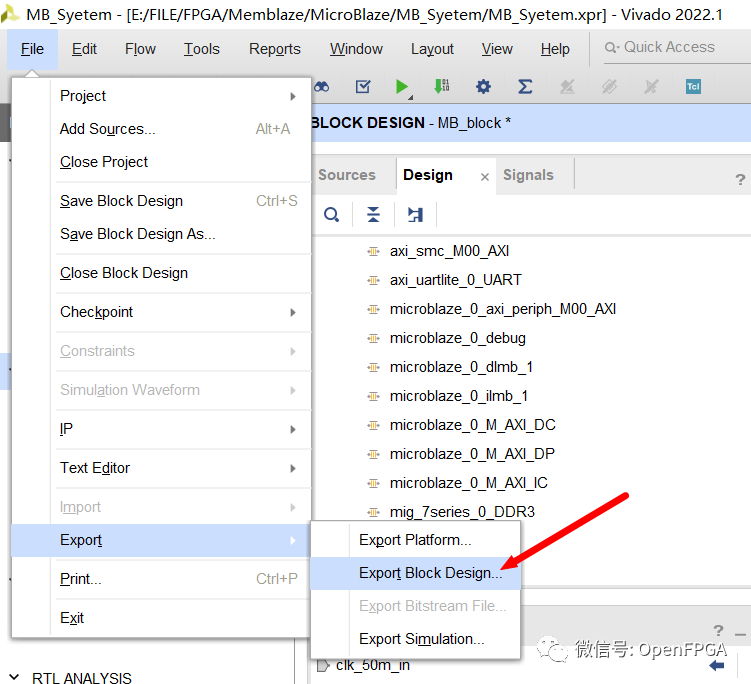

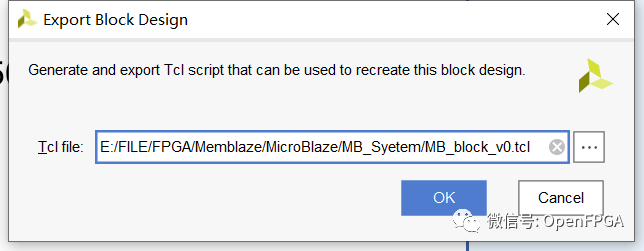

导出BD,按照下图位置:

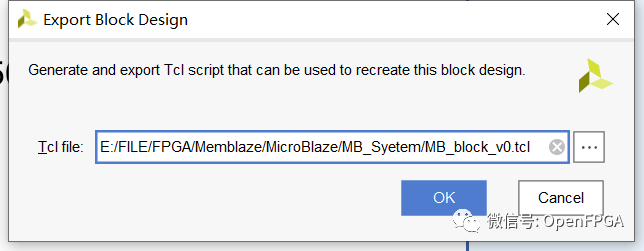

设置路径,设置BD名称:

路径下就生成了一个tcl文件,同理也可以使用下面命令实现相同功能:

write_bd_tcl [你的路径]/xxx_bd.tcl

第16步

上面就完成了整个最小系统搭建,接下来搭建带带DDR的MB最小系统,然后我们以这个最小系统为例说明其为什么具有通用性。

带DDR的MB最小系统

第1步

搭建Vivado系统,不过多赘述了!

第2步

点击 Create Block Design,创建一个 BD 文件,并命名为MB_block。

第3步

单击添加 IP 图标,然后输入关键字 MicroBlaze。

双击将MB添加到 BD 文件中:

第4步

添加时钟,在添加IP图标位置输入关键字Clocking Wizard。

双击将Clocking Wizard添加到BD文件中。

第5步

时钟设置,双击Clocking Wizard对时钟进行配置。

输入时钟根据硬件进行选择,我的硬件是一个单端50MHz时钟,输出时钟参数如下:

clk_out1作为MB的运行时钟,这里设置为100MHz,而clk_out2的200MHz是作为DDR控制器的运行时钟。

勾选locked作为后续威廉希尔官方网站 的复位信号。

其他页面默认即可,点击【OK】完成设置。

第6步

MB设置,在 BD 文件中,双击 MB 图标,对其进行配置,第一页配置参数如下图所示:

注意图中圆圈是需要勾选的,允许外部存储 BRAM 作为程序运行缓冲区,方框部分是软核的频率、面积和性能三方面的综合结果(三方不可同时兼得)。

点击【Next】,进行下一界面进行设置:

界面默认,点击【Next】:

按照上图设置,点击【Next】:

界面默认,点击【Next】:

按照上图设置,允许 AXI 数据流。修改完成之后点击 【OK】 即可。

上面主要修改三个部分:第一页允许外部存储 BRAM 作为程序运行缓冲区;第三页设置Cache基地址和长度;第五页是允许AXI数据流,用来访问外部DDR。

第7步

让BD自动完成设置,点击Run Block Automation完成剩下的设置。

弹出的界面默认即可,时钟使我们上面第4步Clocking Wizard生成的。

第8步

引出相关引脚。

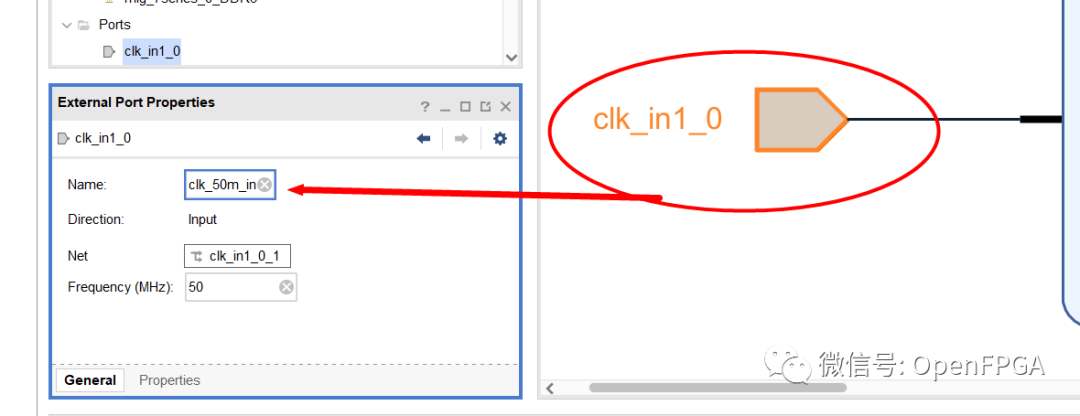

上图界面选择clk_in1,组合键 【Ctrl+T】 引出引脚:

上图界面选择clk_in1,组合键 【Ctrl+T】 引出引脚:

第9步

验证目前设计的正确性:

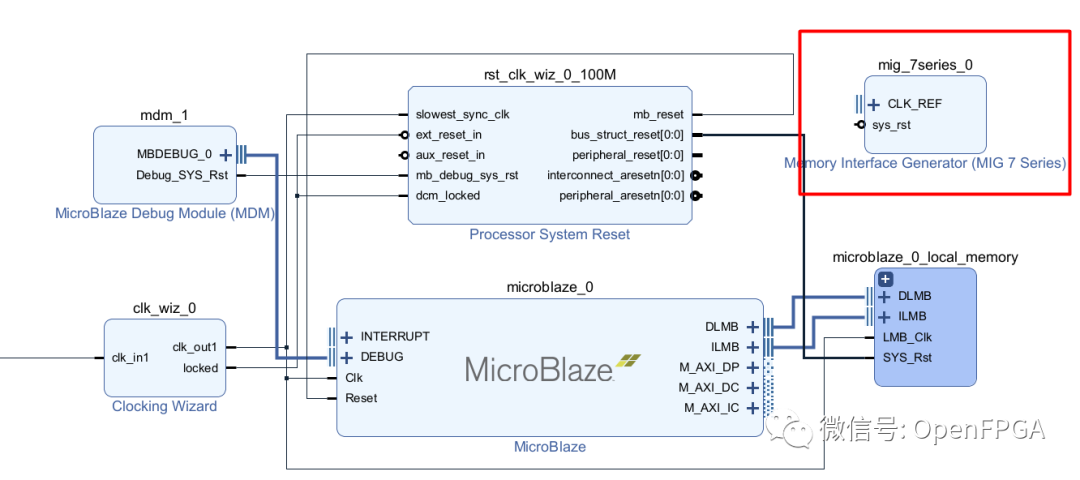

目前这一步已经完成了最小系统设计,下面开始DDR设计。

第10步

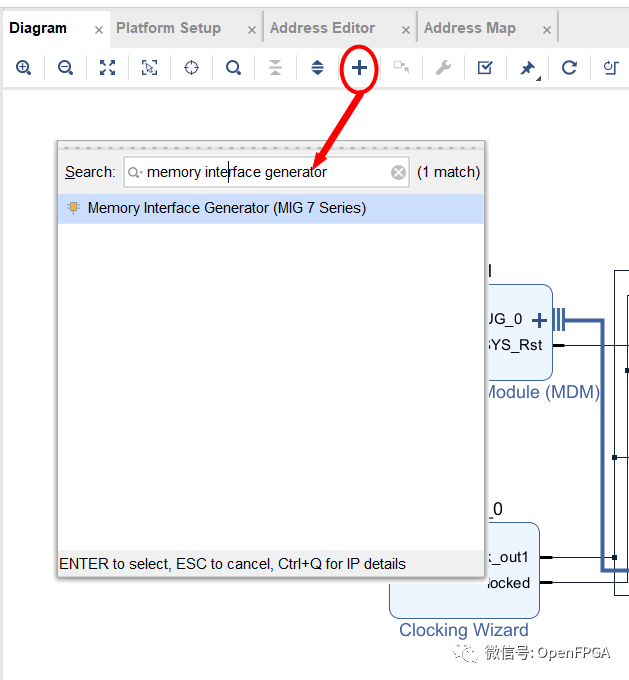

添加DDR控制器:

添加IP界面,输入关键字memory interface generator

双击memory interface generator后再BD中添加MIG:

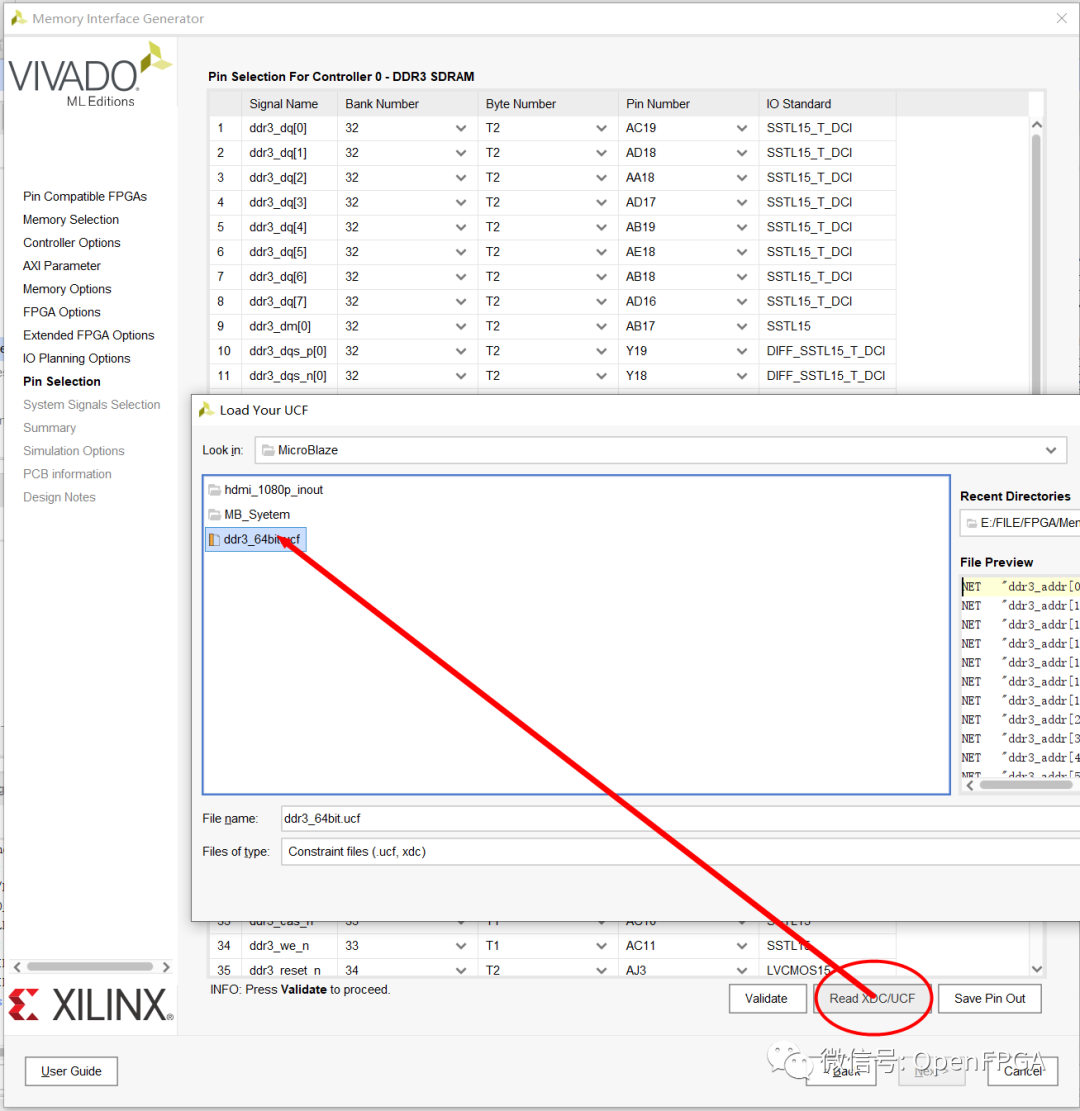

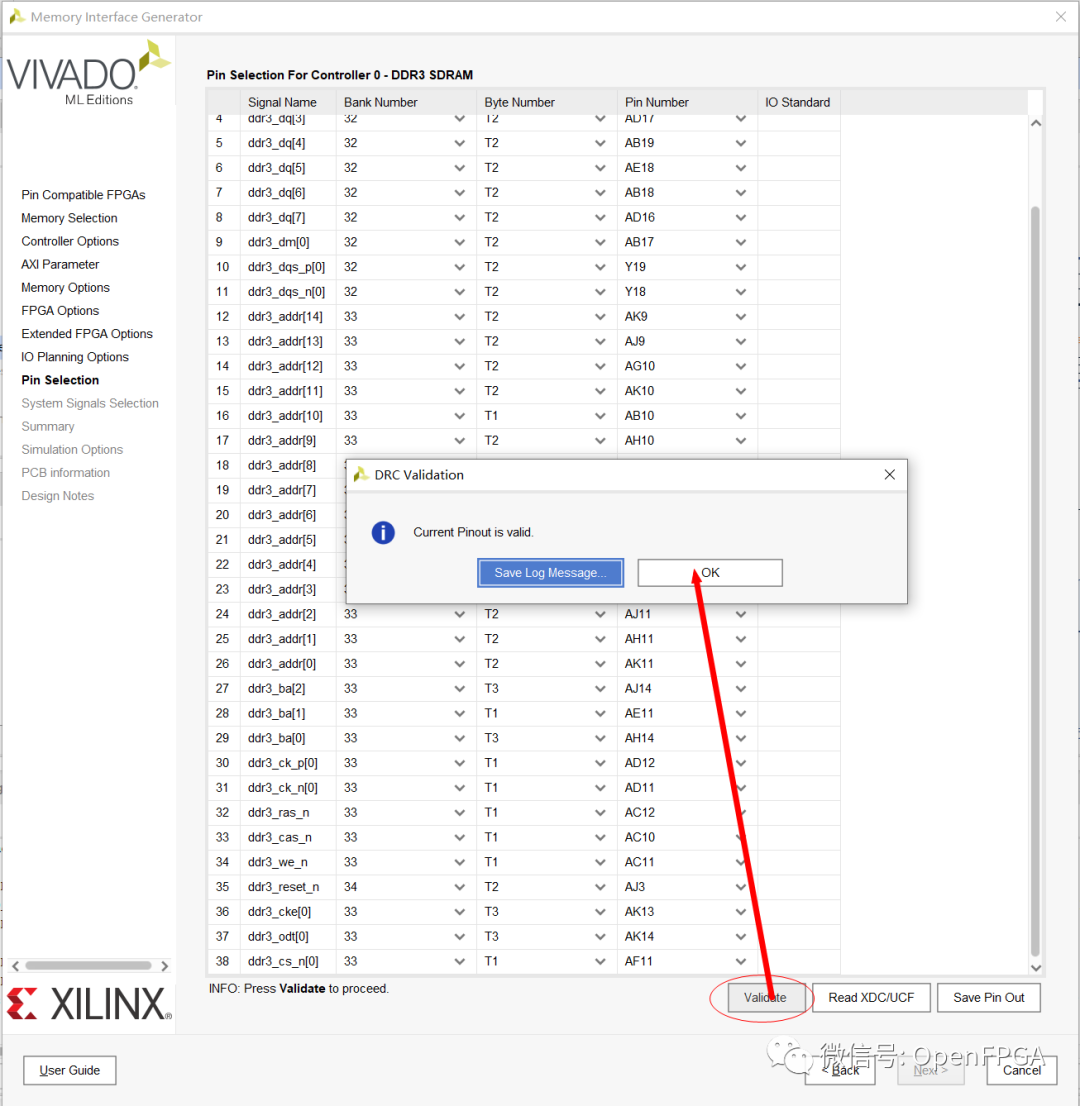

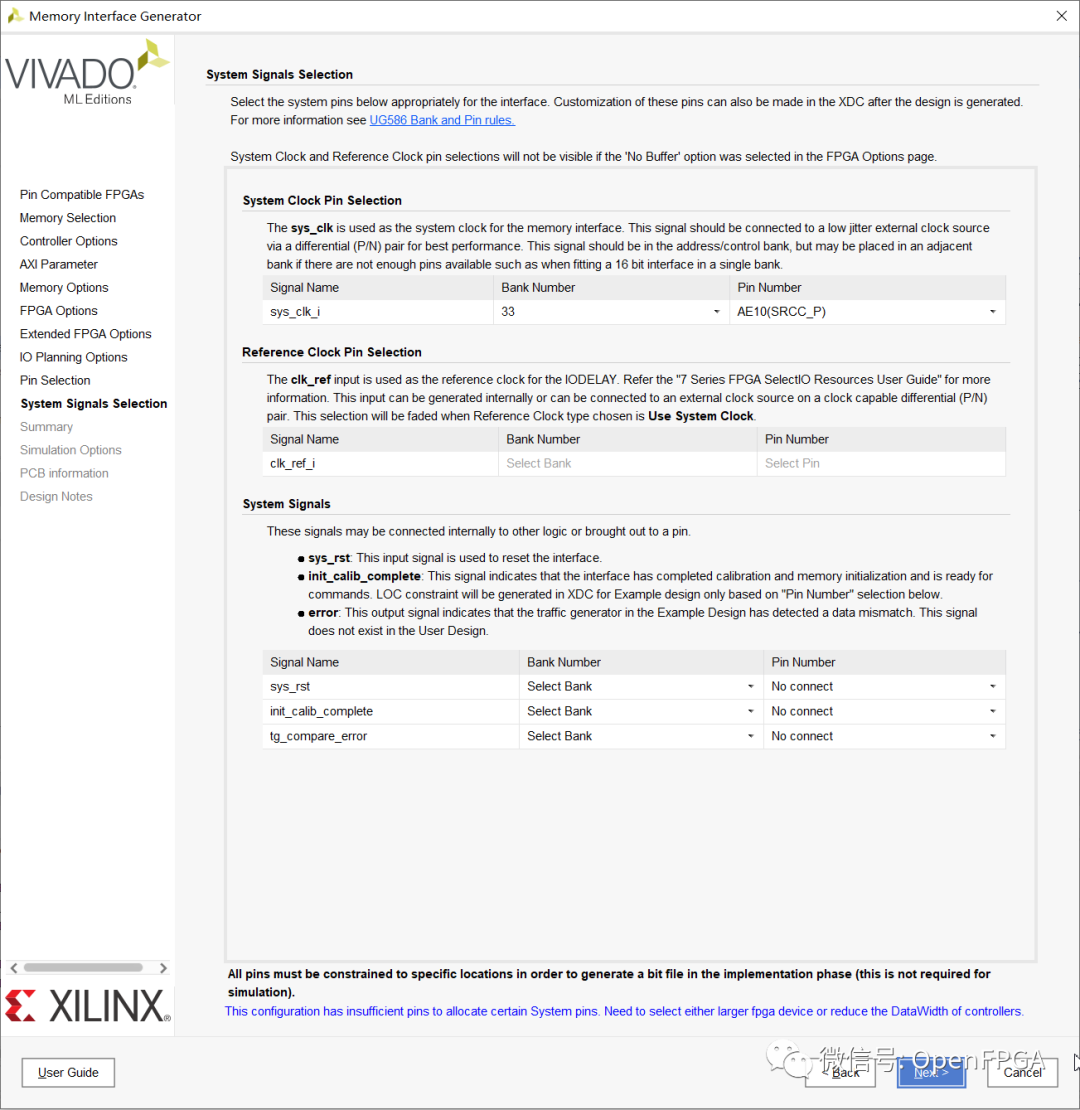

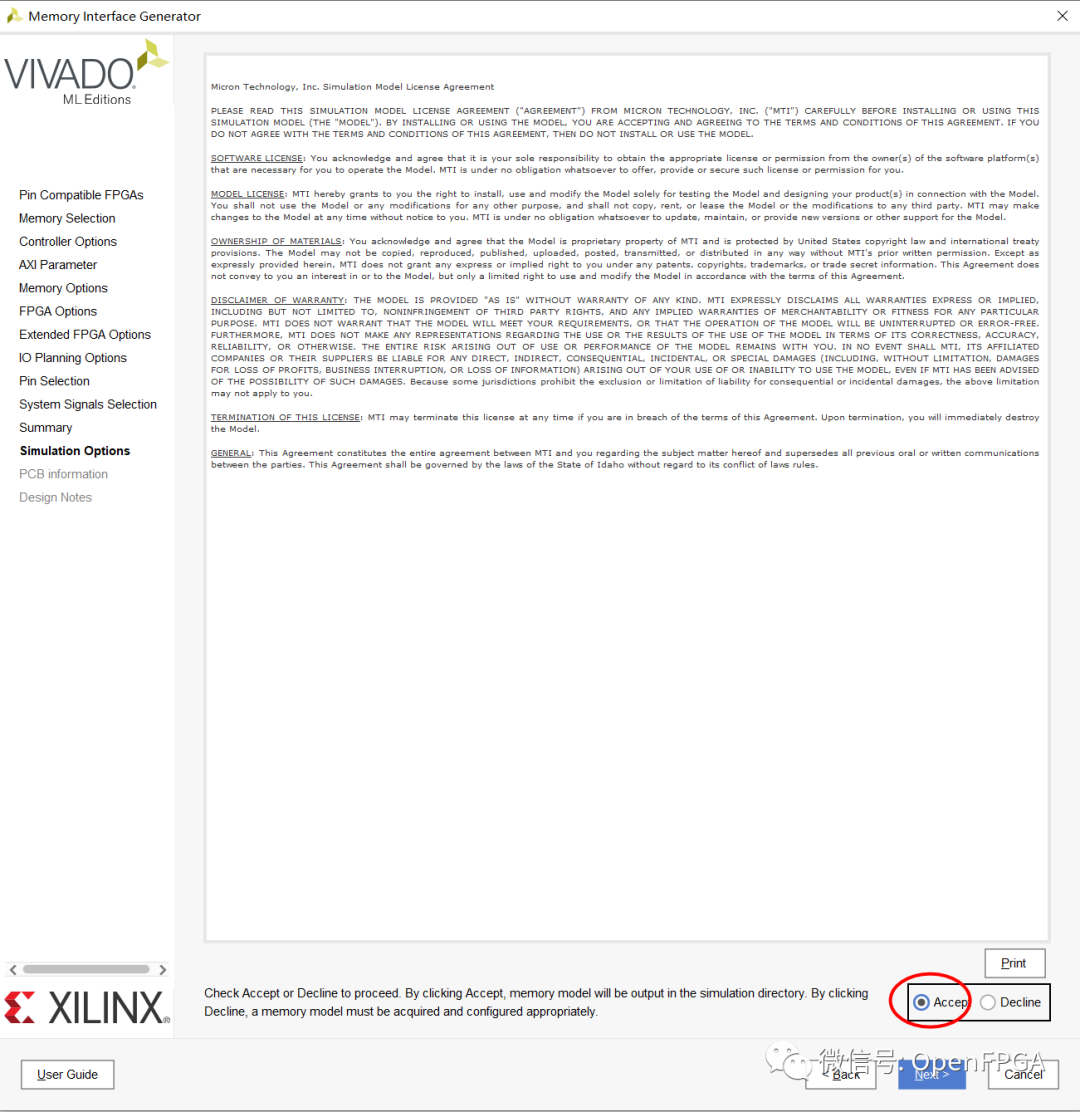

第11步

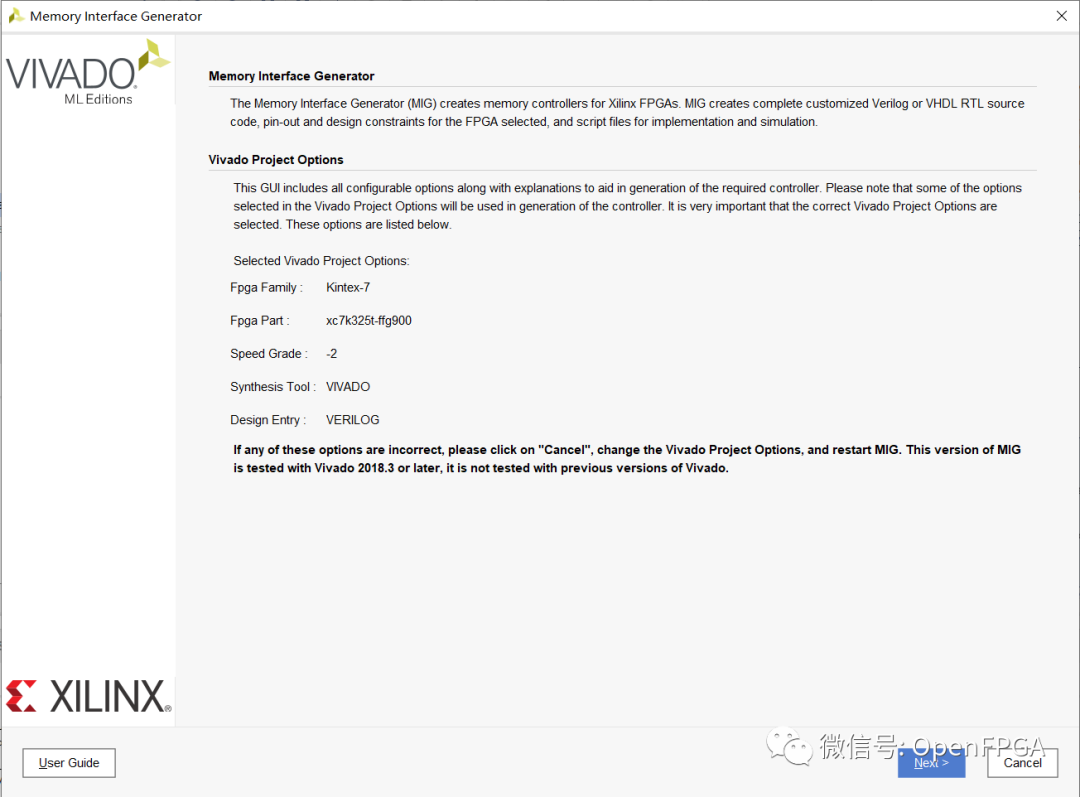

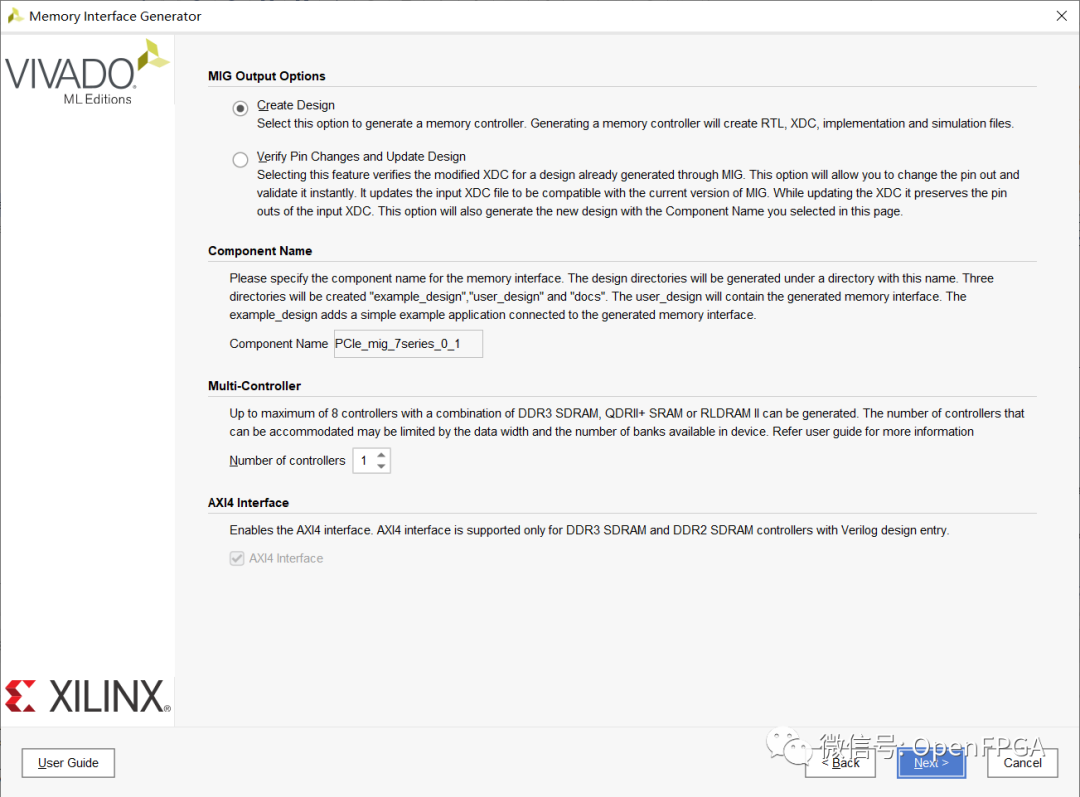

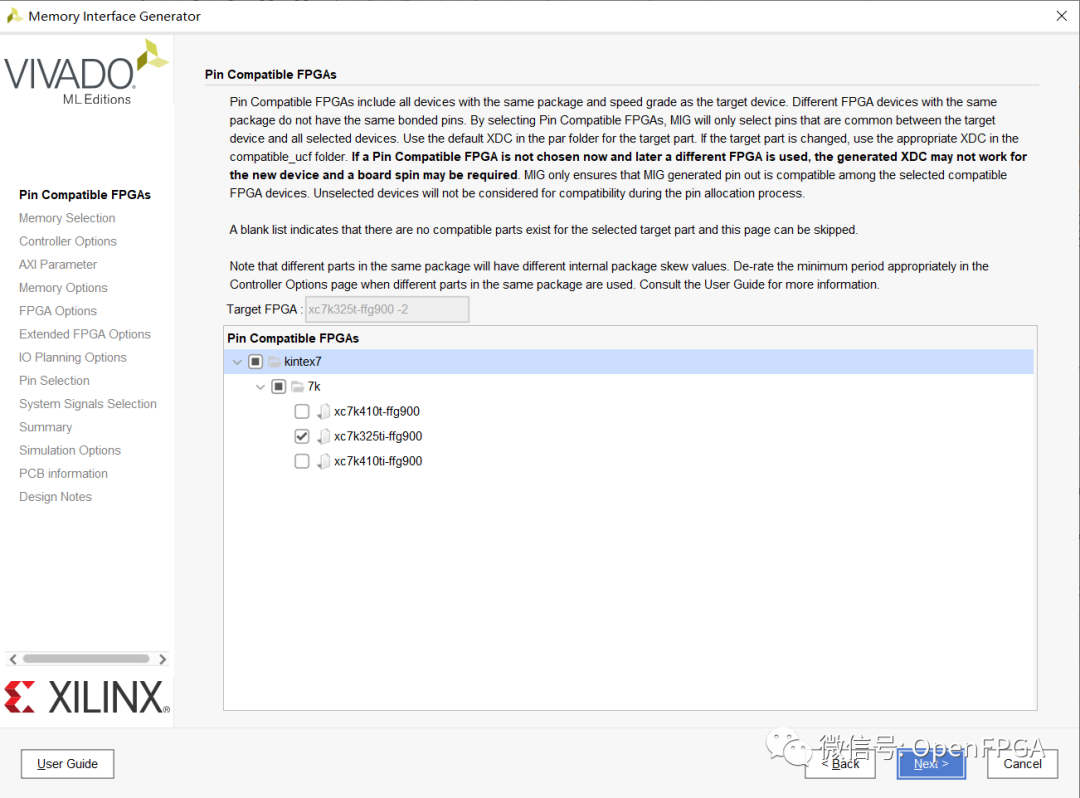

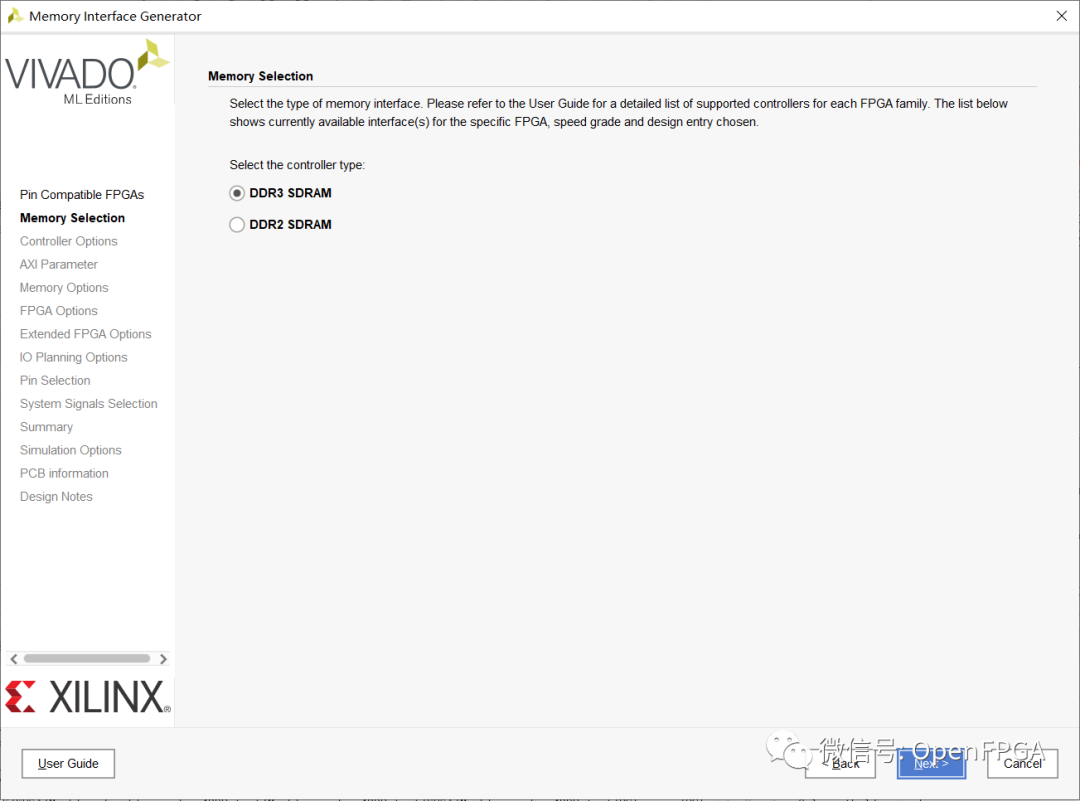

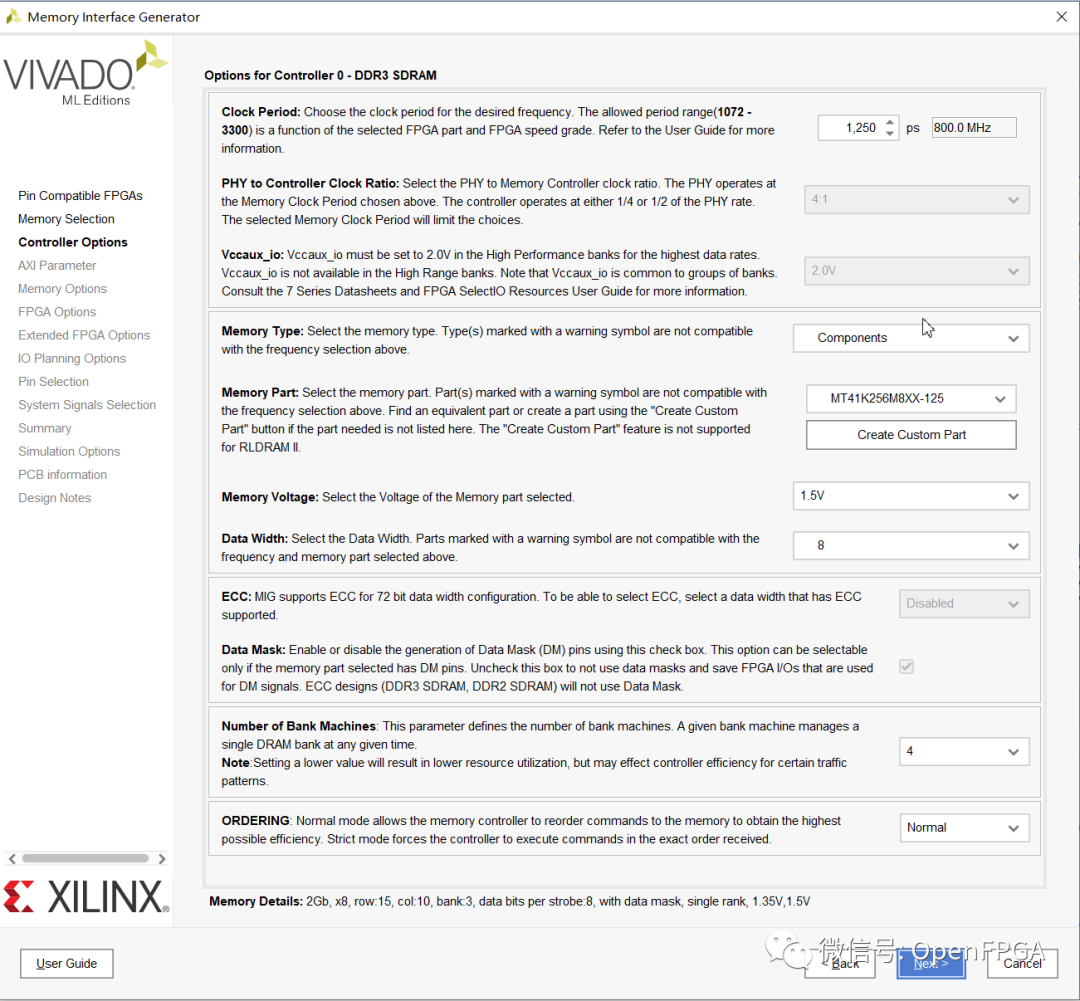

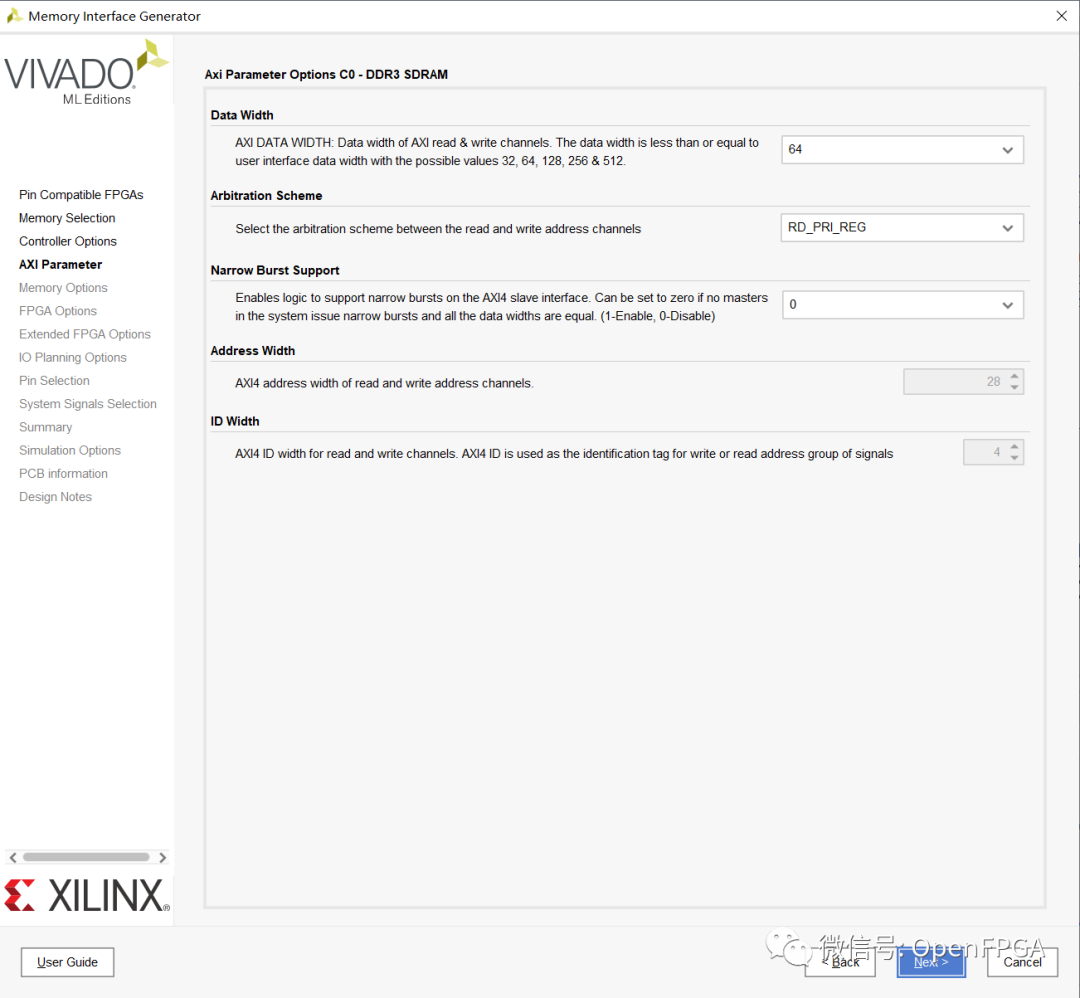

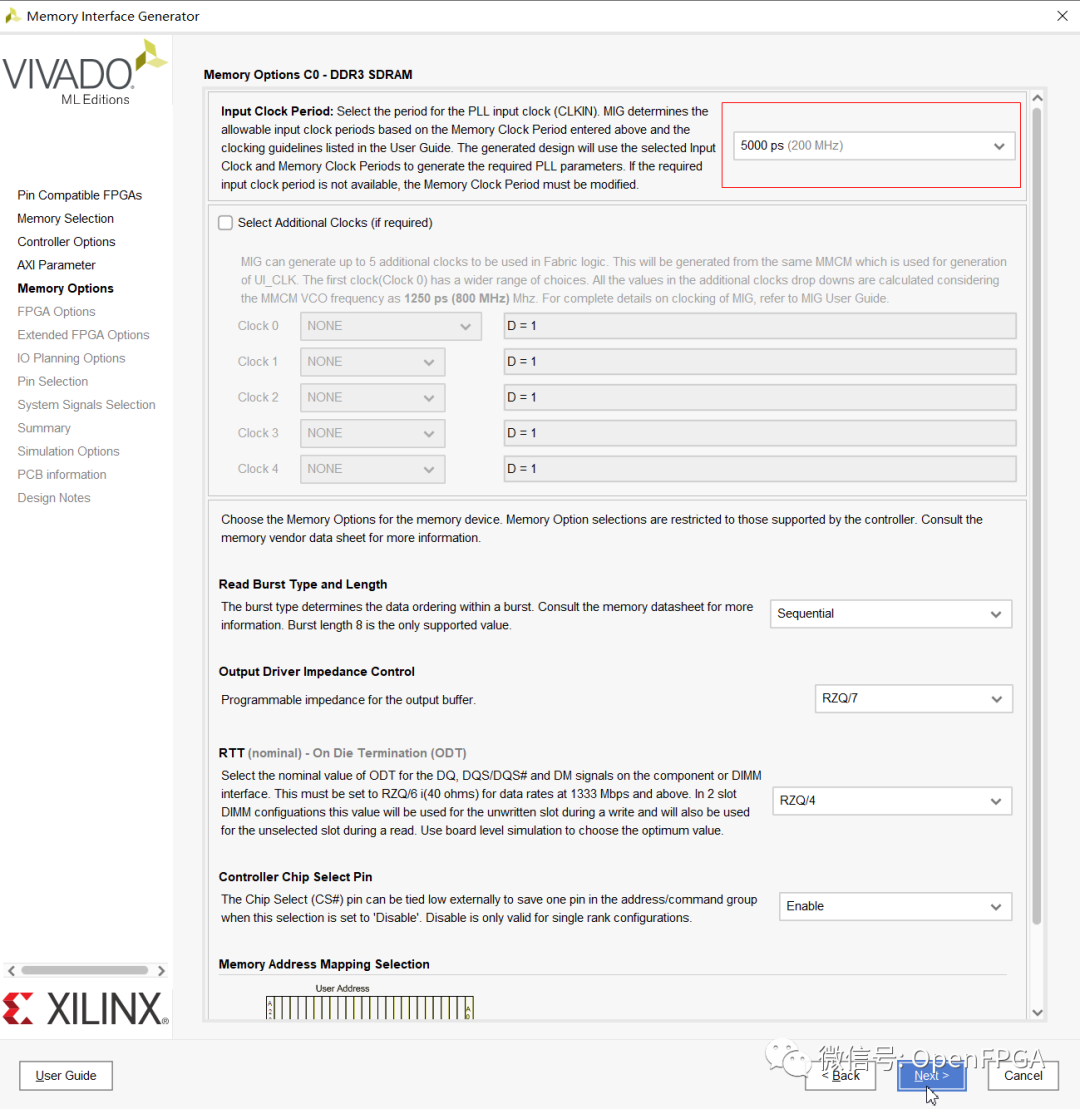

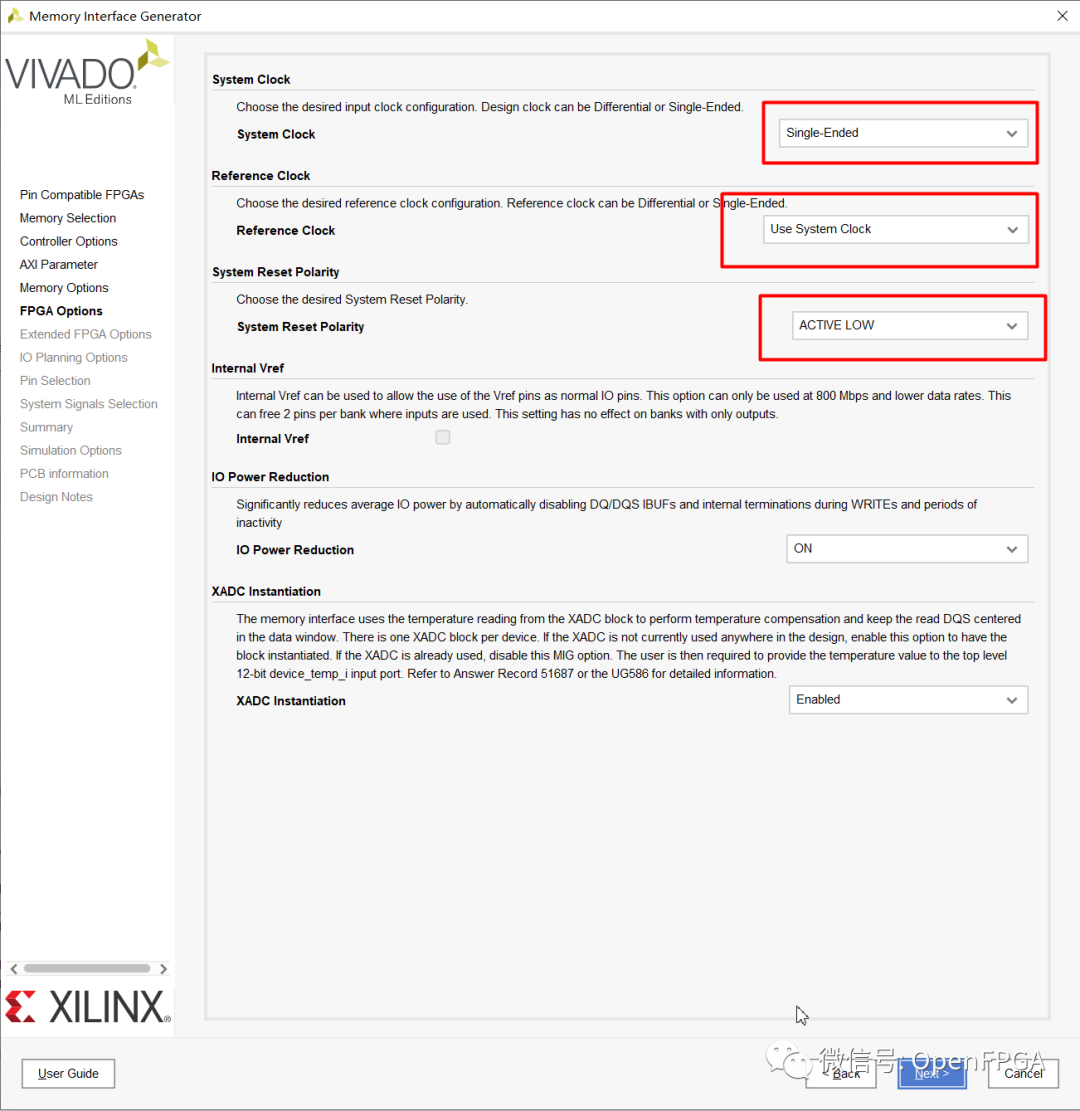

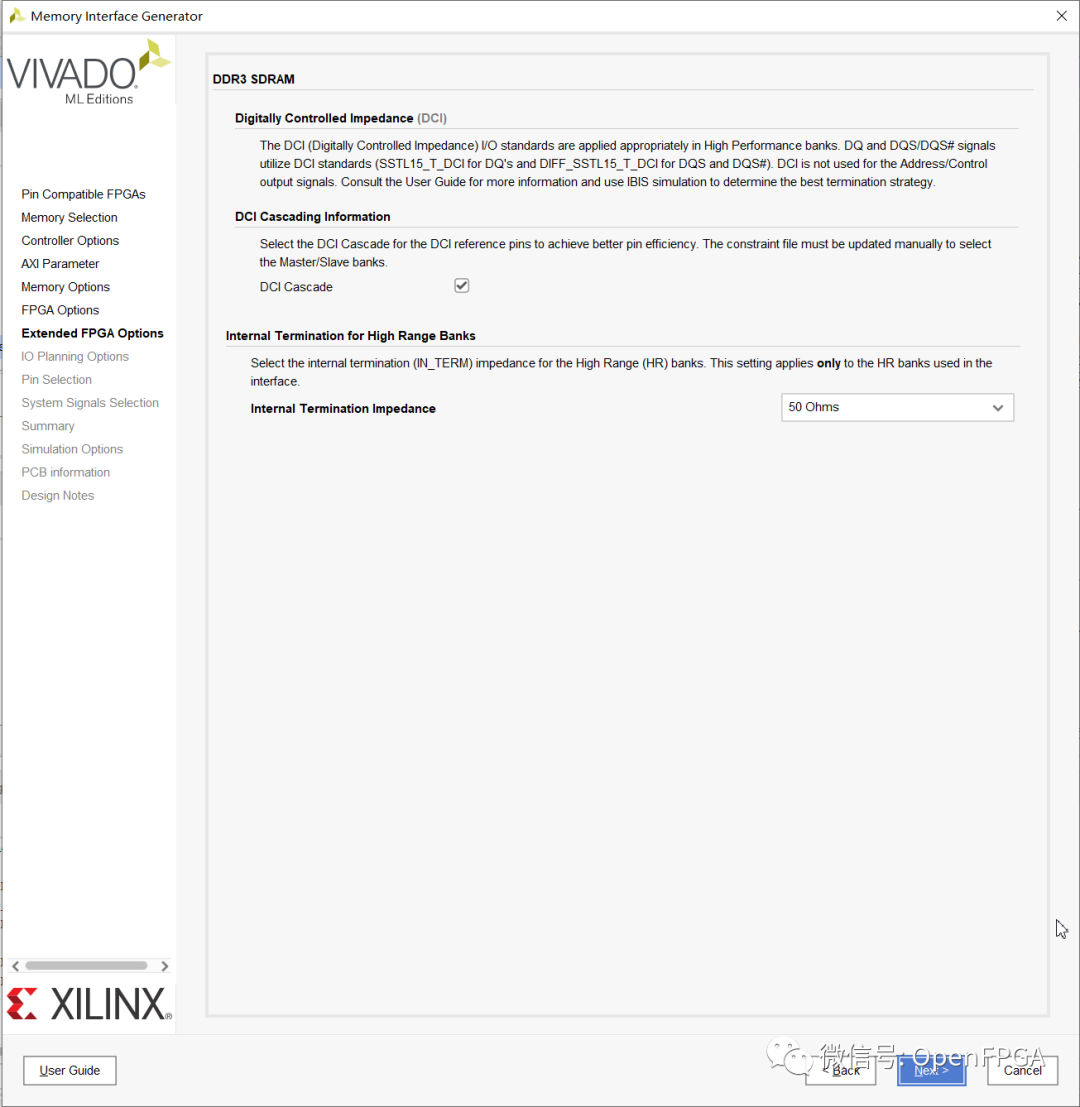

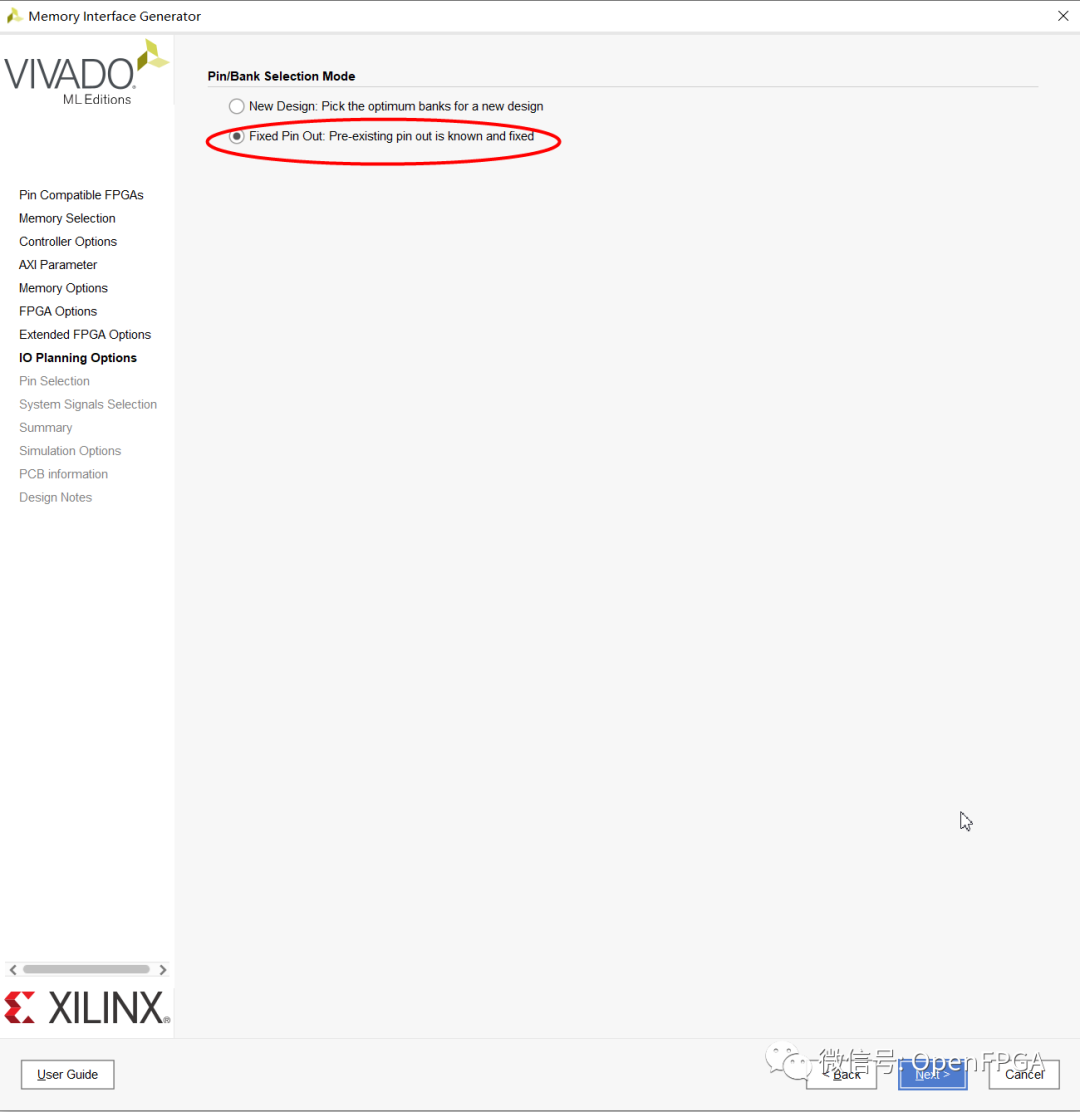

设置MIG IP。

双击 mig_7series_0,进行如下配置:

注:如果system clock的频率在199-201MHz之间,这里会出现一个use system clock 的选项,意思就是用系统时钟作为参考时钟

后面全部默认点击【NEXT】即可。

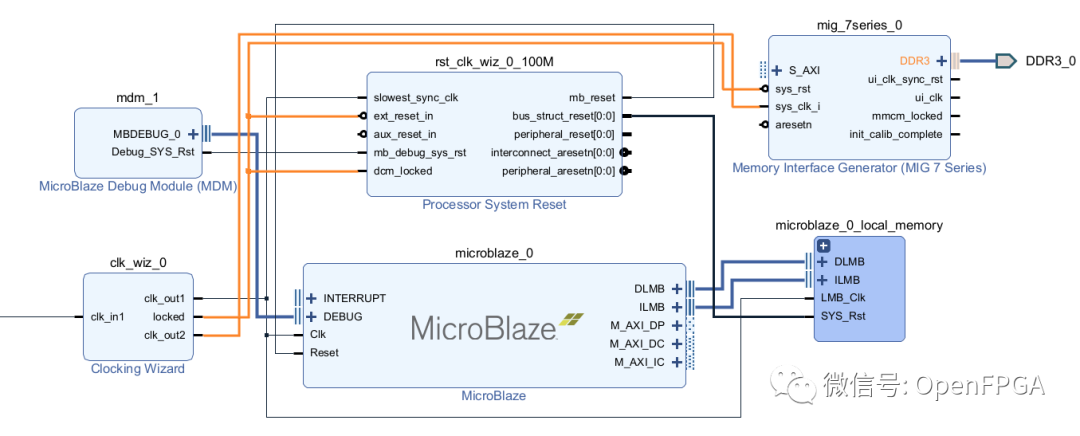

将MIG的线按照下图进行连接:

第12步

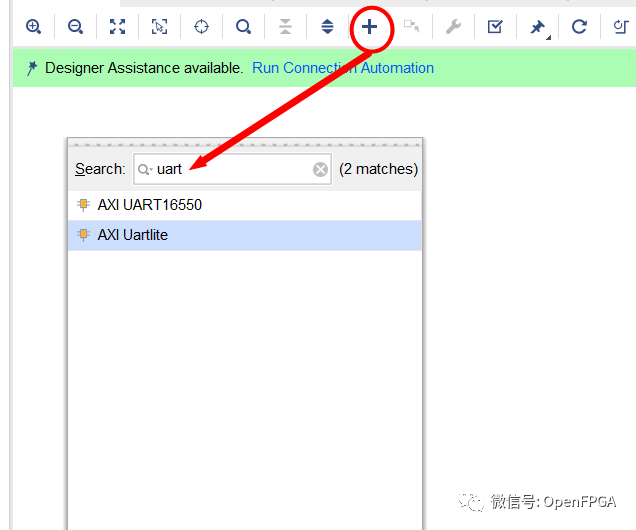

添加外设,我们主要添加串口,负责调试。

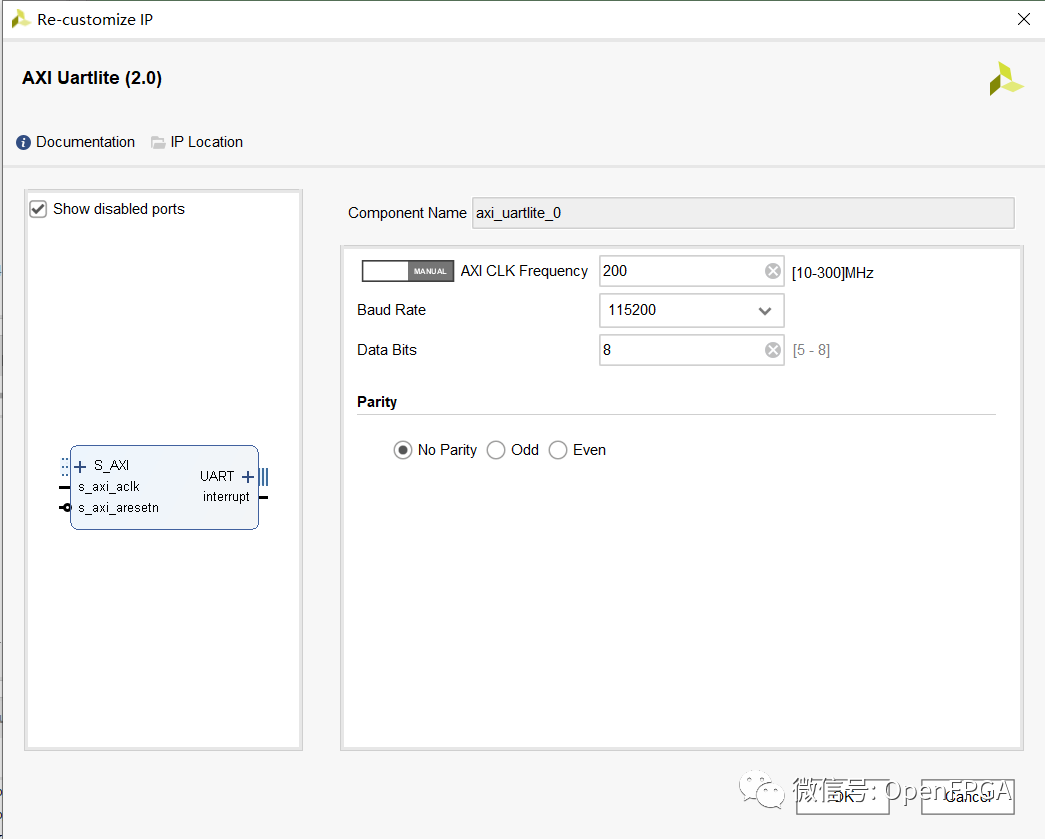

双击 UART,将波特率改为 115200:

第13步

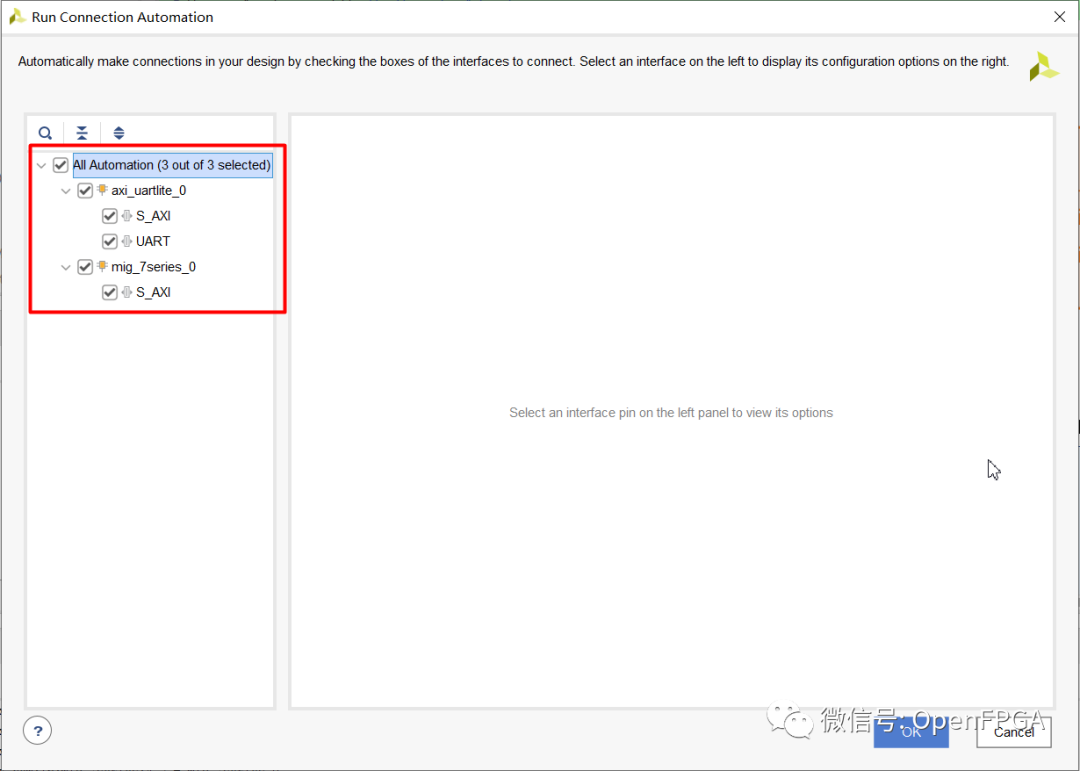

再点击 Run connection Automation,再弹出来的窗口中把所有选项勾选上,再点击【OK】 即可。

验证设计:

第14步

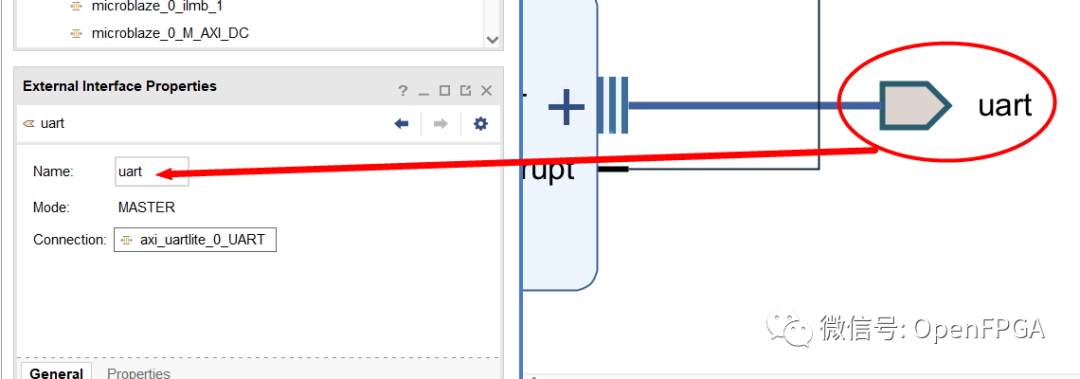

修改引脚名称,因为这部分将作为一个最小系统供后续使用。

第15步

导出BD,按照下图位置:

设置路径,设置BD名称:

路径下就生成了一个tcl文件,同理也可以使用下面命令实现相同功能:

write_bd_tcl [你的路径]/xxx_bd.tcl

测试及固化程序

第1步

建立一个新的Vivado工程。

第2步

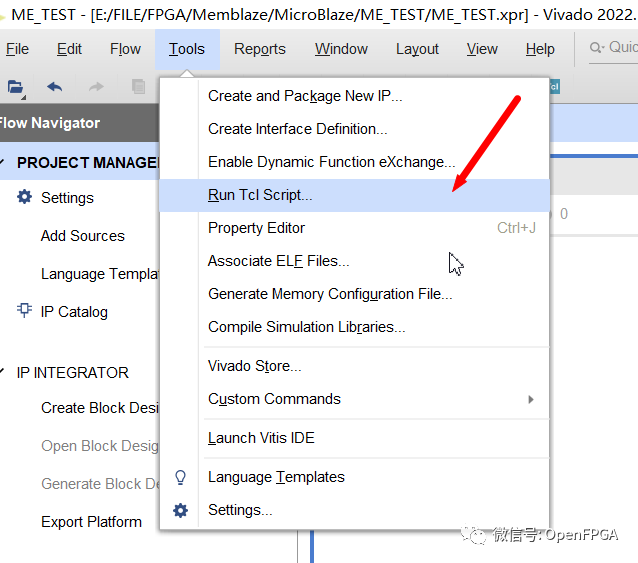

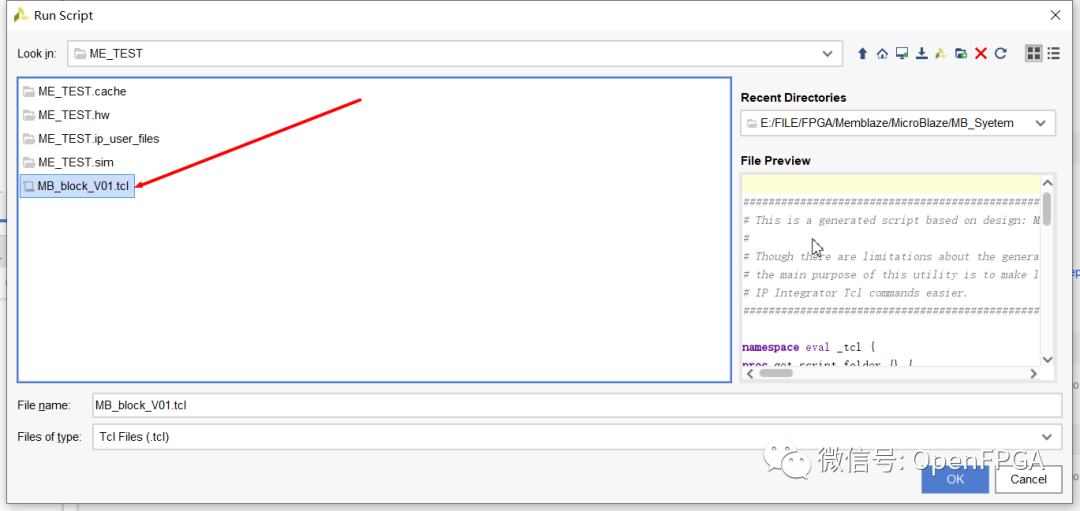

导入上一节生成的最小系统:

选择tcl文件,确定即可

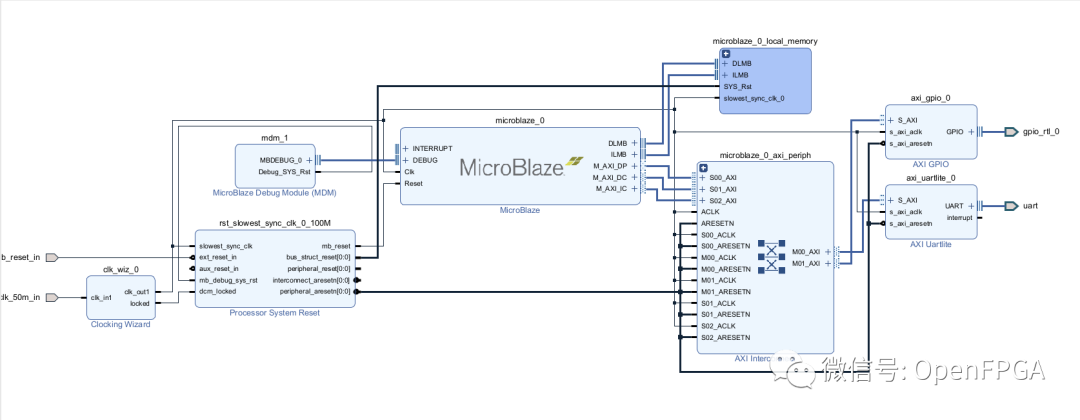

这样就生成了一个最小系统:

第3步

添加Clocking Wiard,按照下图进行设置

第4步

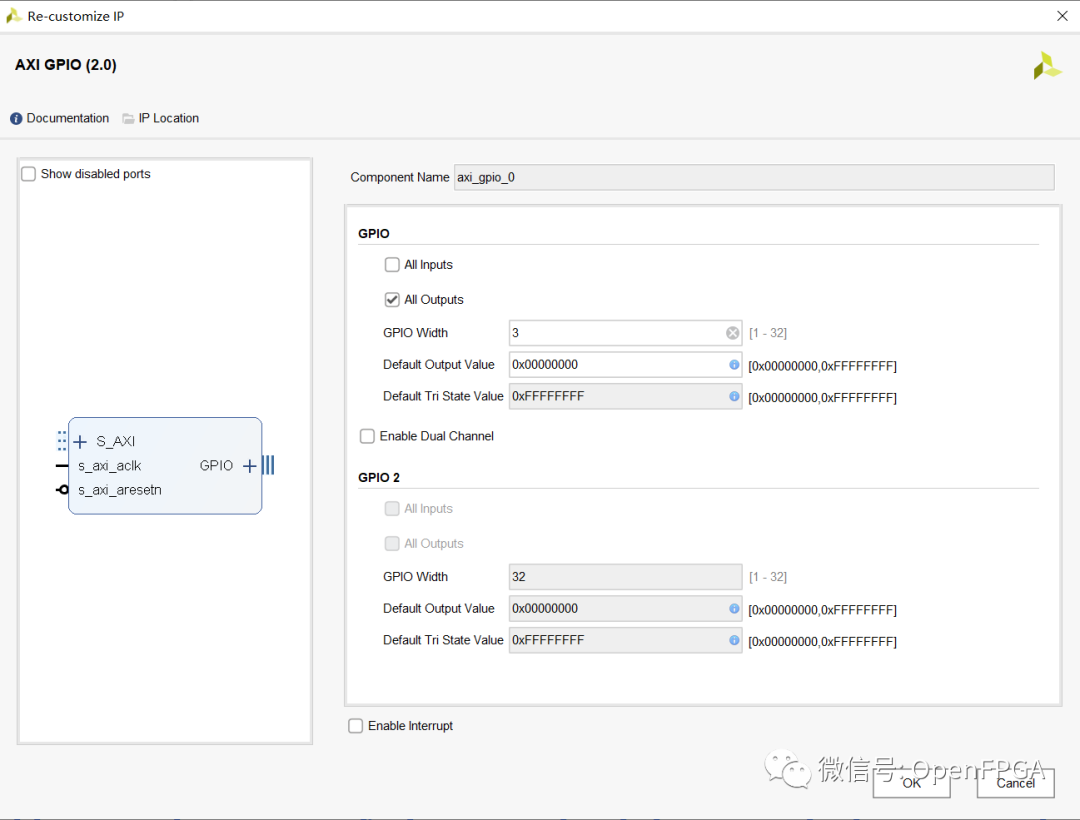

添加一个AXI-GPIO,按照下图设置:

后面控制三个LED等。

第5步

点击 Run connection Automation,再弹出来的窗口中把所有选项勾选上,再点击【OK】 即可。

第6步

导出硬件

将 bd 文件导出为 tcl 脚本之后,继续对工程进行完善。

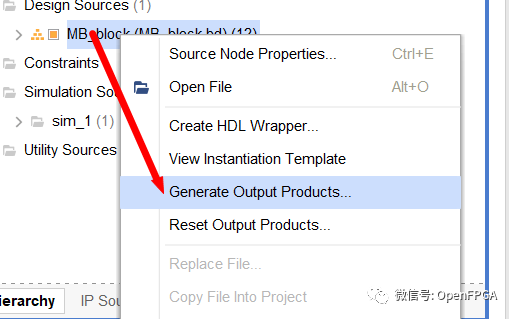

选中 xxx.bd,右单击然后选择 Generate Output Products。

第7步

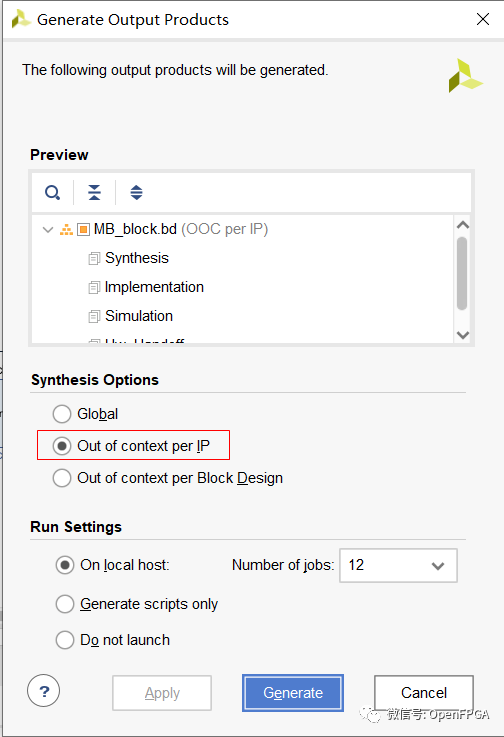

在弹出来的窗口中,如下图所示,然后单击【OK】。

第8步

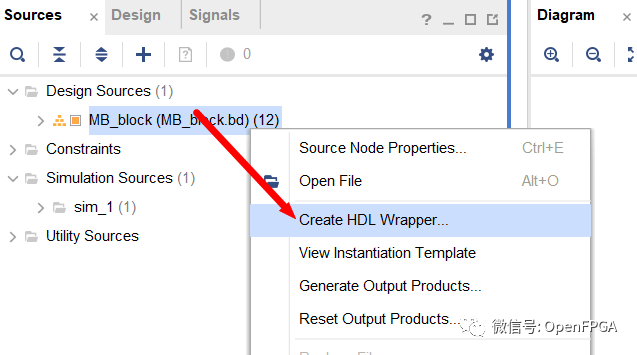

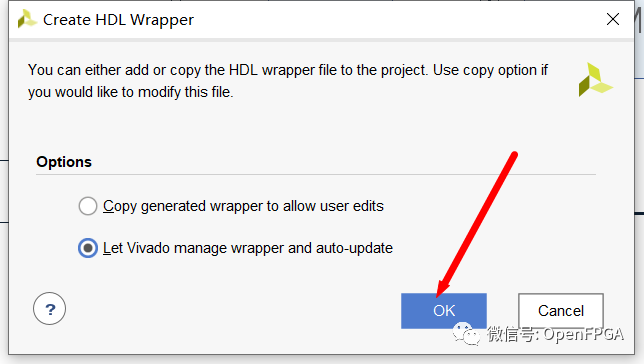

选中 XXX.bd,右单击然后选择 Create HDL Wrapper,在弹出来的窗口中直接点击【OK】。

第9步

添加一个名为 mb_test.xdc 的约束文件,并添加约束(物理约束需要根据自己硬件选择)。

第12步

单击下列图标产生 Bit 文件。

第13步

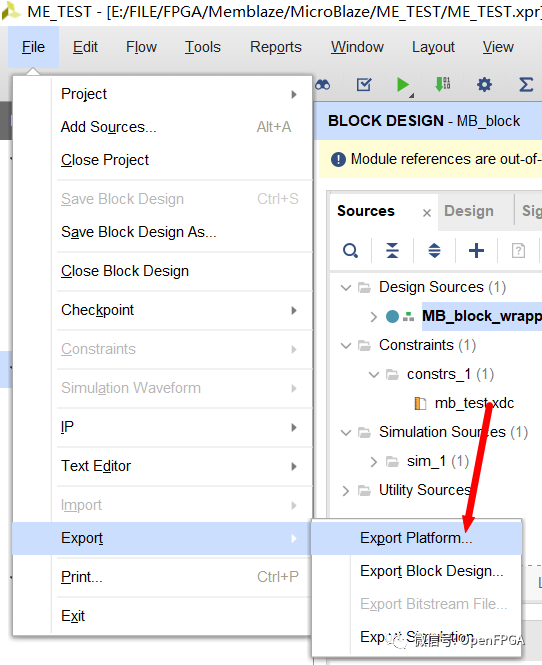

生成 Bit 文件之后,单击 File-Export-Export Platform...

第14步

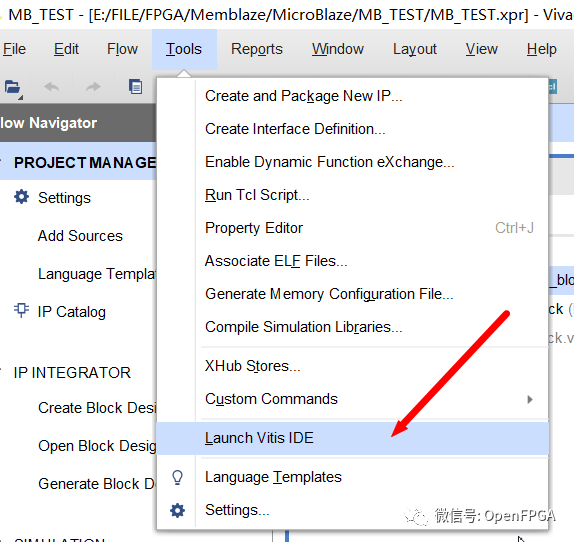

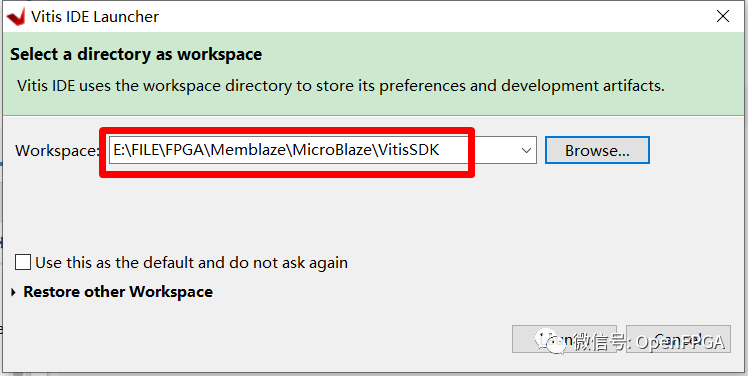

TOOLs-->Launch Vitis IDE

选择工作文件夹。

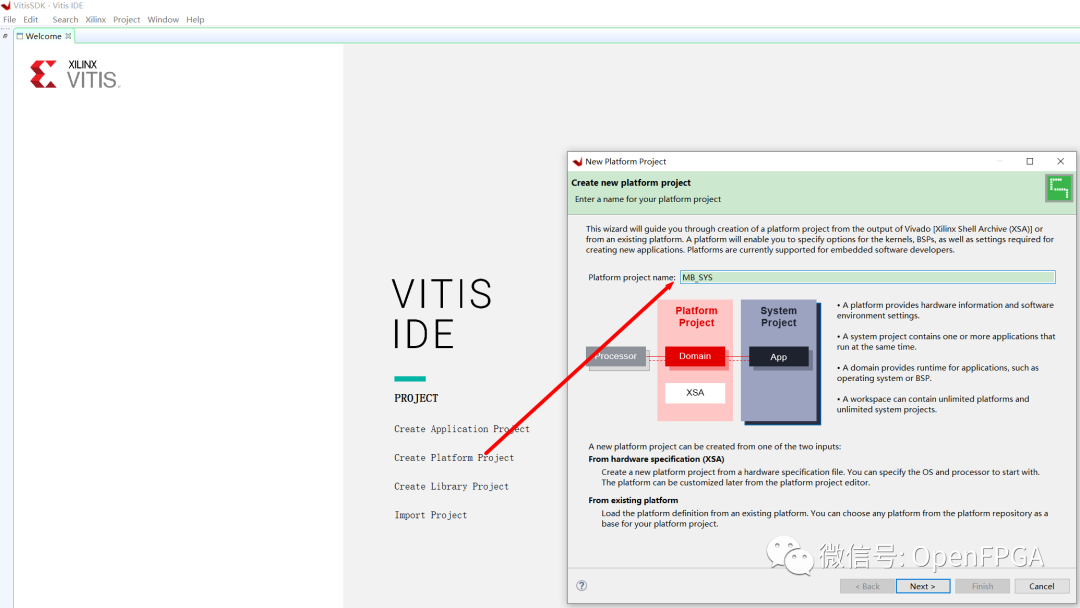

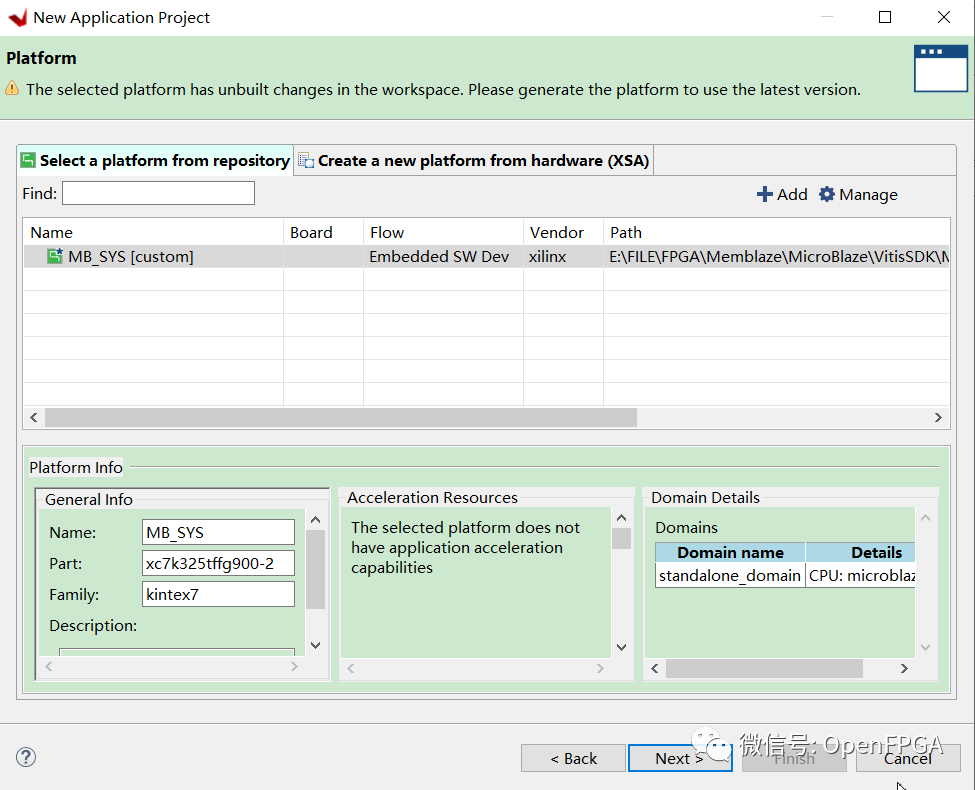

创建Platform

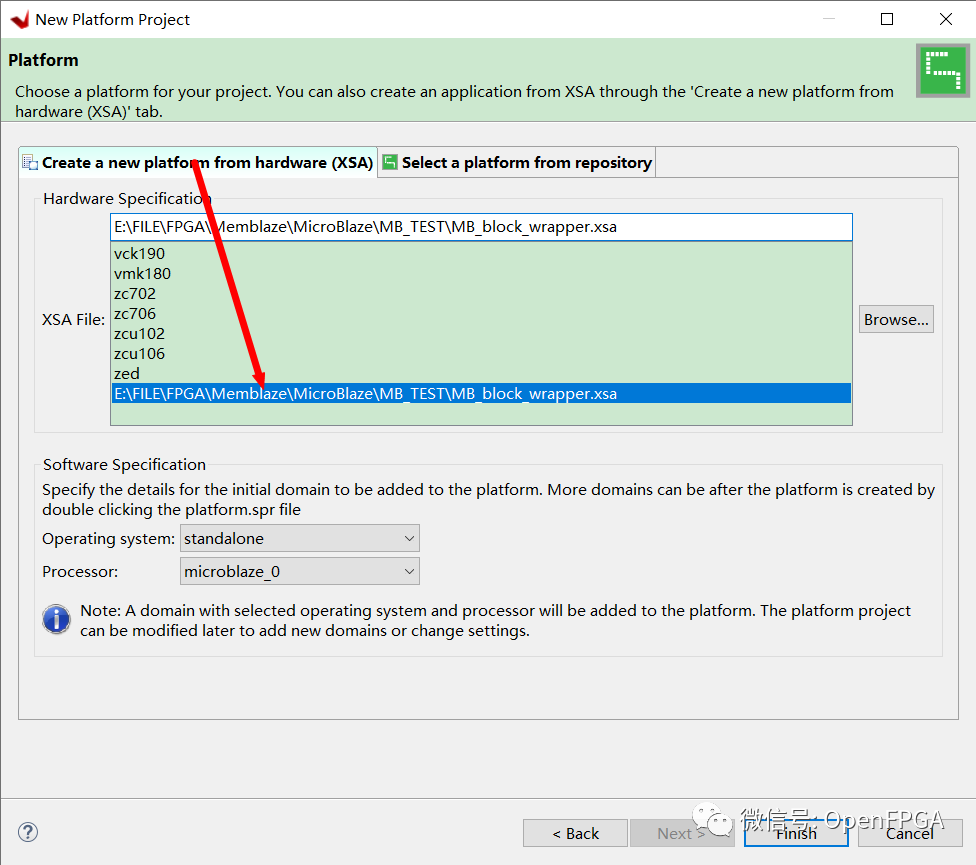

选择上一步生成的Platform(XSA文件)

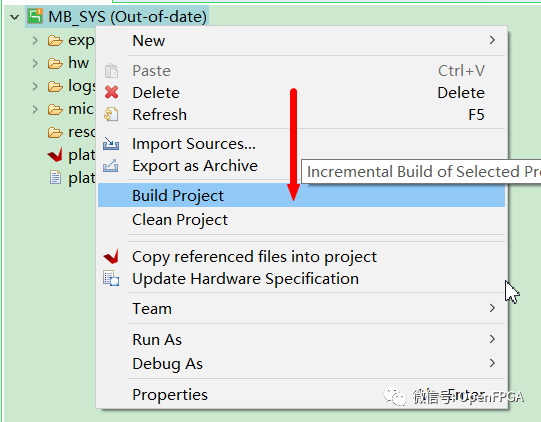

右击,build project

无问题后继续后面步骤。

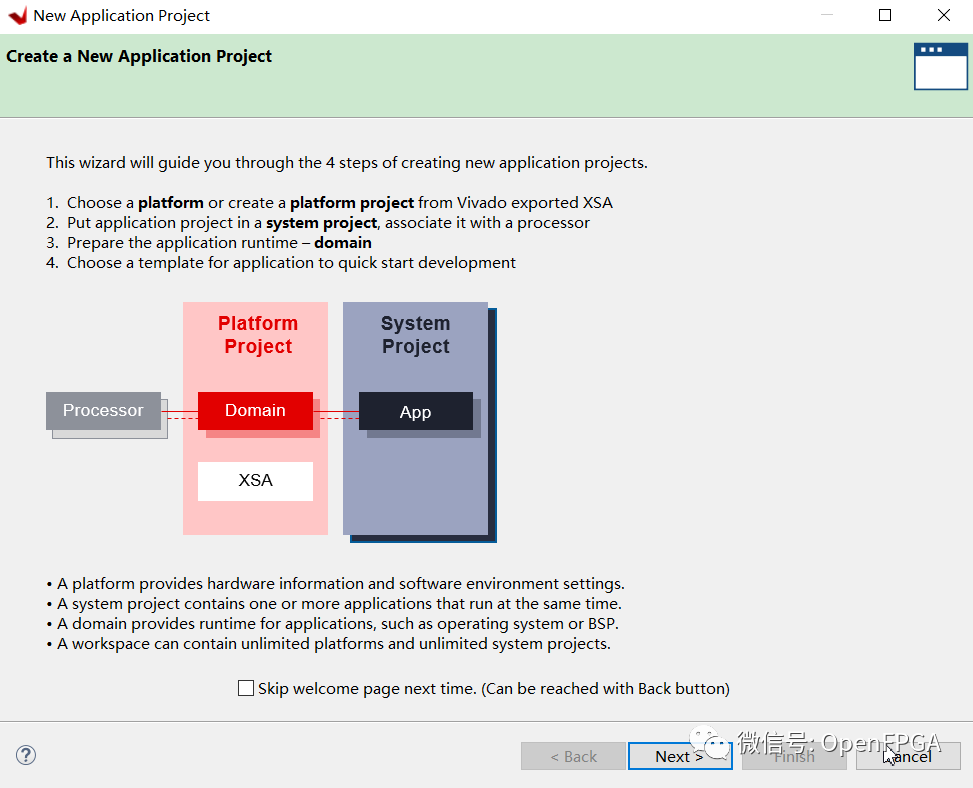

第15步

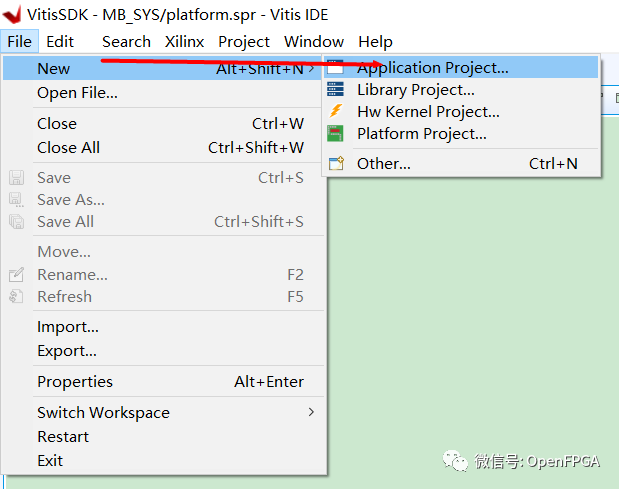

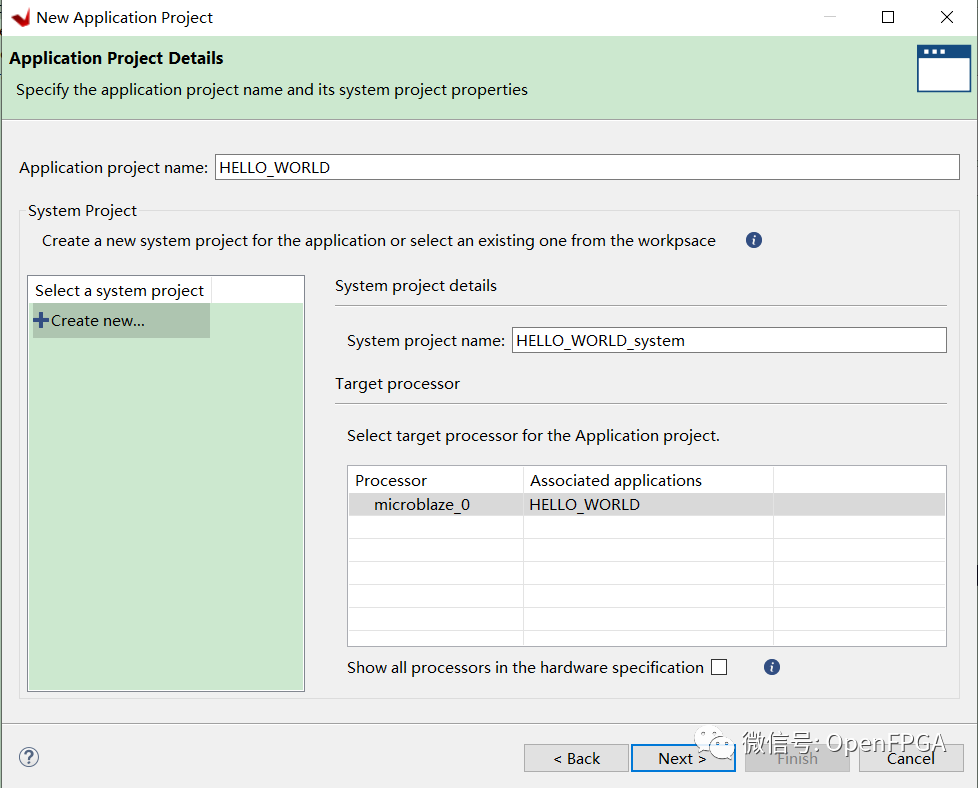

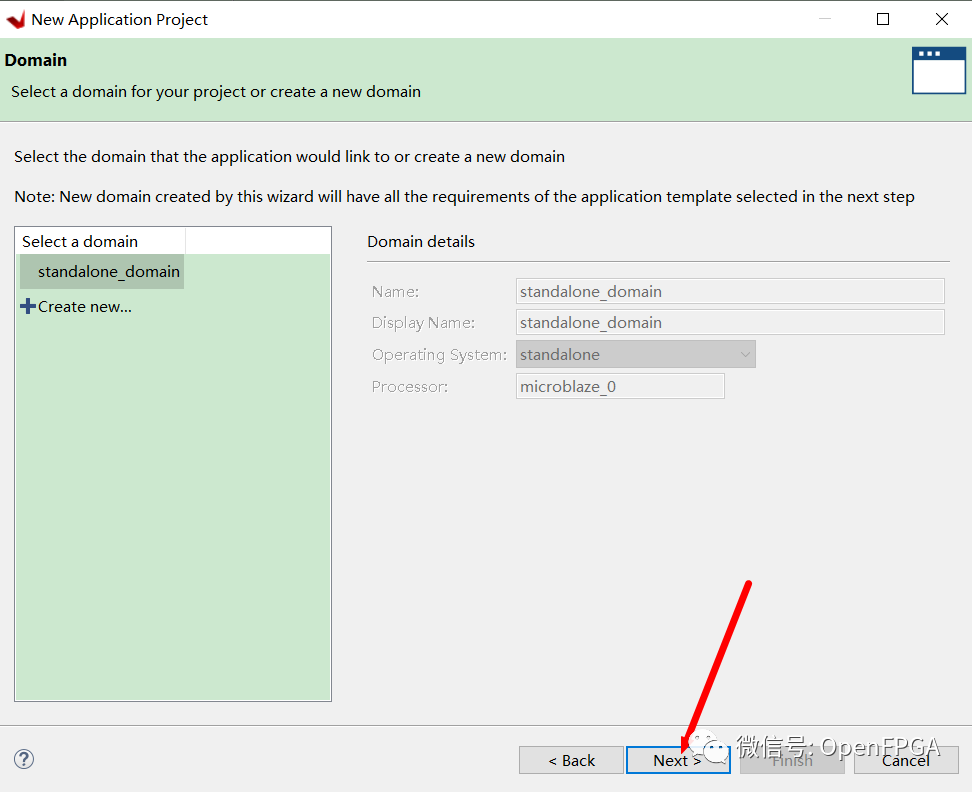

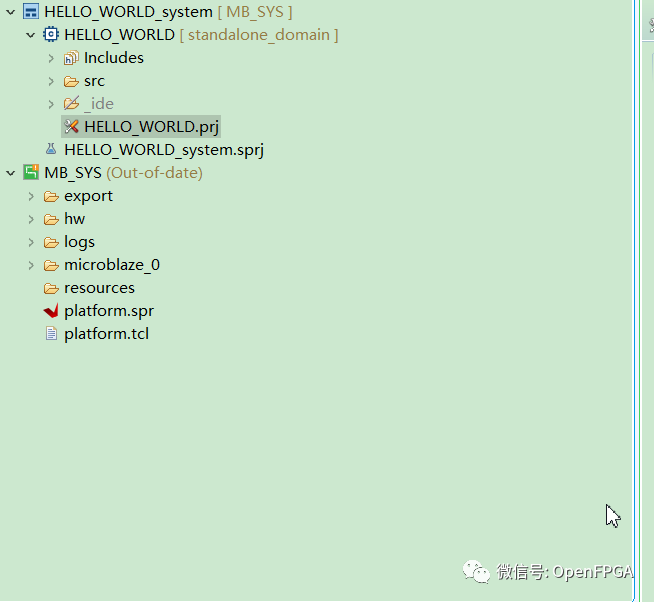

创建App

【NEXT】

【NEXT】

输入App名称:

【NEXT】

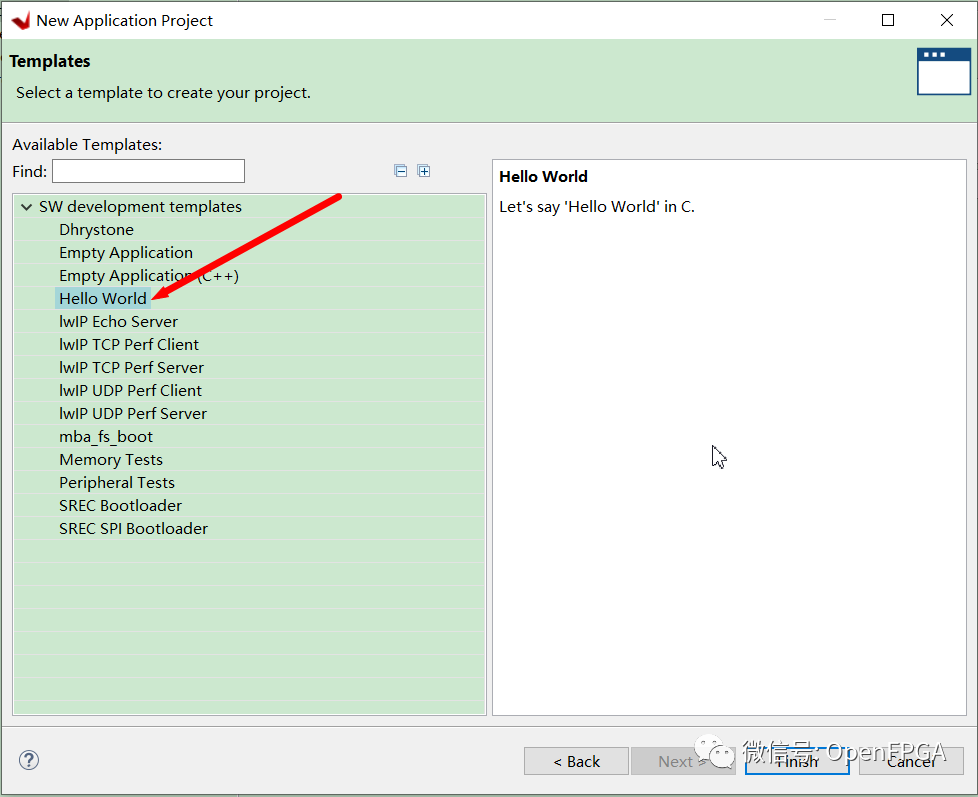

选择Hello World模板。

【FINISH】

第16步

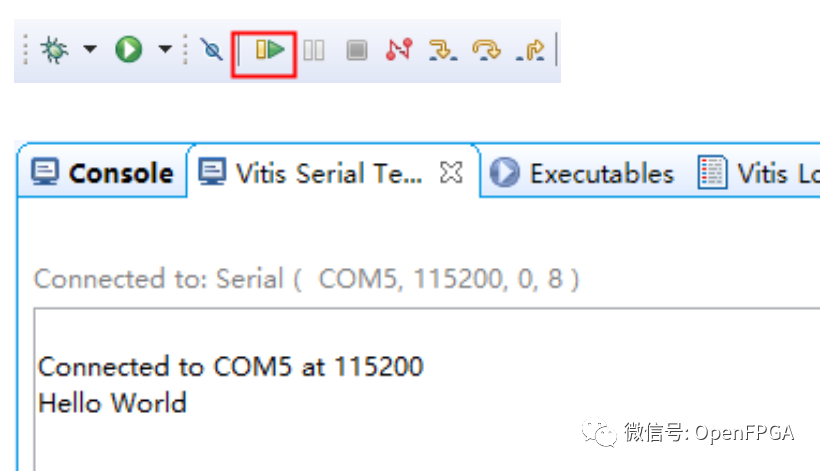

helloworld.c源码我们先不修改。

右击 HelloWorld-->Debug As-->Debug Configurations

设置好参数,使用Vitis自带的串口工具,运行后即可看到打印信息。

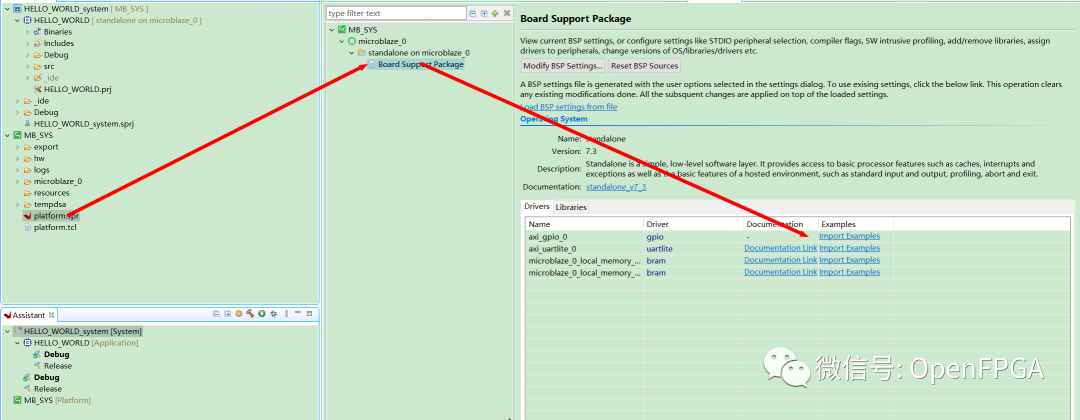

接下来就是添加GPIO驱动,和上面操作一样,这里有个小技巧,在建立完App后,点击下图位置:

导入官方提供的历程就可以了。

同样HelloWorld-->Debug As-->Debug Configurations后进行调试即可。

下面说明固化过程。

第17步

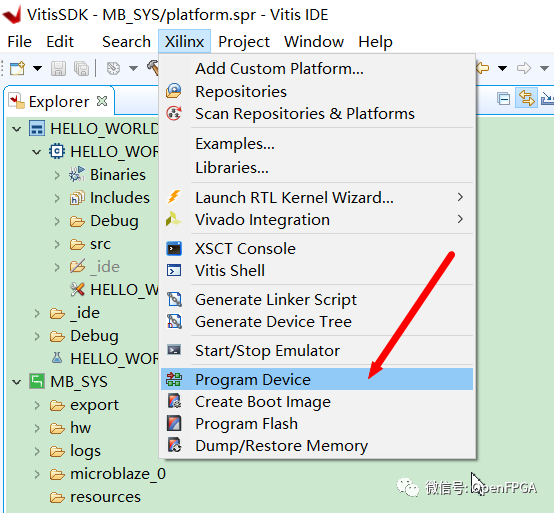

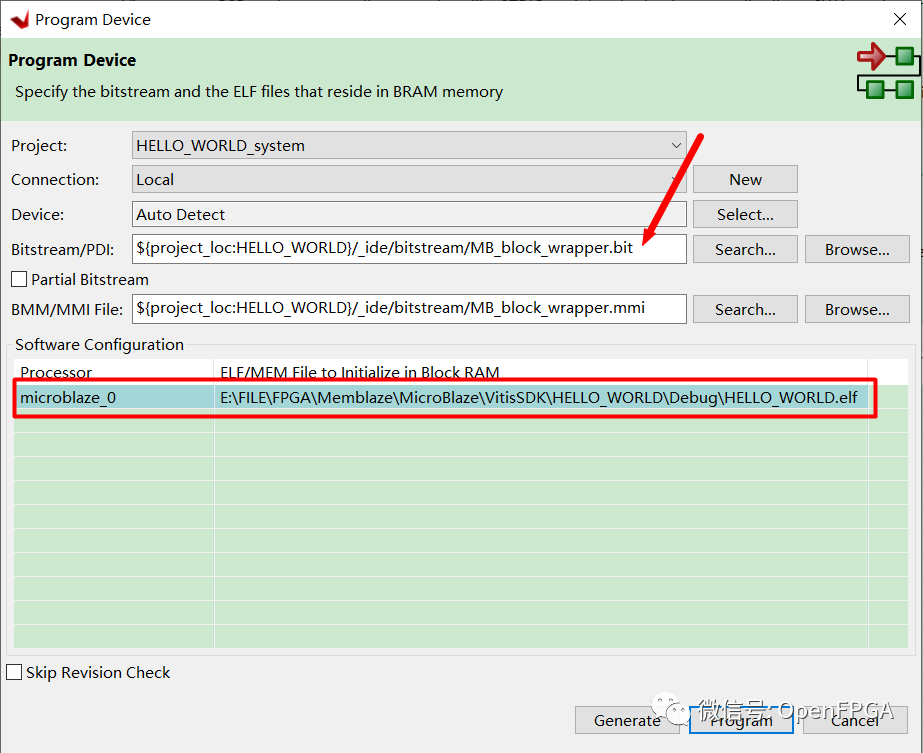

固化第一步,生成bit文件,点击XIlinx-->Program Device

记住箭头部分生成的bit文件,同时选择方框内编译出的elf文件。

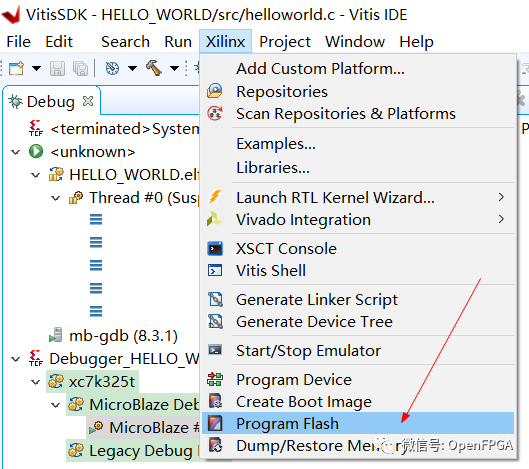

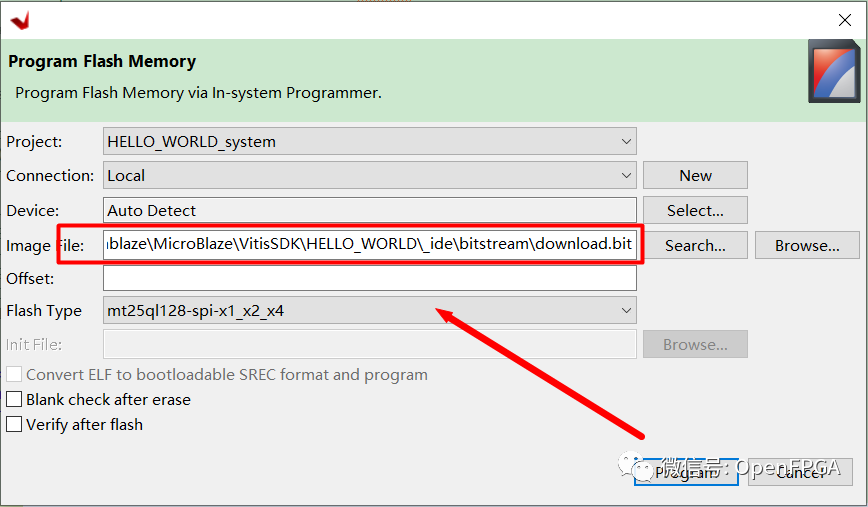

固化第二步,下载固化FLASH,点击XIlinx-->Program Flash

箭头选择板卡上FLASH的FLASH,方框选择上一步生成的bit文件(默认dowload.bit)。

点击【Program】,完成后重新上电即可。

总结

今天简单演示了一个MB小例子。

审核编辑:刘清

-

如何去搭建一种Nios ii最小系统2021-11-25 0

-

如何自制一个单片机最小系统呢2021-11-25 0

-

如何自己动手画一个最小系统板子?2022-02-15 0

-

怎么搭建51最小系统?2022-02-16 0

-

怎样去搭建一种RK3288最小系统威廉希尔官方网站 呢2022-03-03 0

-

51单片机最小系统是什么?51单片机最小系统的威廉希尔官方网站 介绍2019-08-12 9387

-

如何使用AD9画一个51单片机的最小系统2019-06-28 1524

-

如何搭建一个SSH的最小系统2019-05-07 787

-

设计并制作一个单片机最小系统2021-03-25 908

-

STM32最小系统搭建(原理图)2021-11-17 1069

-

Altium Designer绘制stm32最小系统2021-11-17 1574

-

用Altium Designer软件绘制一个stm32最小系统的威廉希尔官方网站 原理图2021-11-17 1331

-

Nios ii最小系统搭建教程2021-11-17 347

-

详解STM32最小系统威廉希尔官方网站2023-05-17 4952

-

基于FPGA搭建Micro Blaze最小系统2023-09-01 2646

全部0条评论

快来发表一下你的评论吧 !