ADS在信号完整性和电源完整性仿真方面的应用

描述

随着数据传输速率的快速增加,从而使得以前微秒(us)量级的边沿或保持时间减少到纳秒(ns)甚至皮秒(ps)。如此高的带宽需求使得传统的设计解决方案已经很难满足系统正常工作的需求。另外,随着集成威廉希尔官方网站 的工艺发展使得集成度越来越高,导致芯片上电流密度急速增加,使信号完整性的问题更加严重。因此非常有必要从整个系统设计开始就考虑信号完整性与电源完整性的问题。这就需要在设计前后把信号完整性和电源完整性仿真引入到设计流程中。

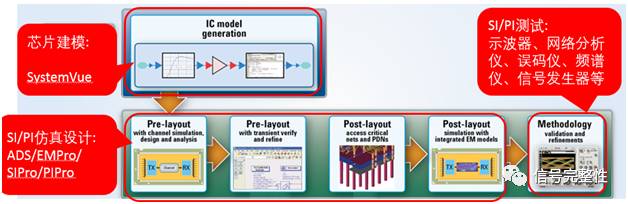

信号完整性和电源完整性产品设计的各个阶段都需要考虑。是德科技在信号完整性和电源完整性领域提供了一套整体的解决方案,包括芯片建模、板级仿真、系统仿真以及产品研发和生产的测试,如下图1所示:

图1是德科技信号完整性和电源完整性流程

芯片的建模和系统级的仿真主要使用SystemVue。在信号完整性和电源完整性方面,主要应用ADS和EMPro。因为ADS中有丰富的模型、操作的灵活性以及对外部的模型也有非常好的兼容性,所以ADS应用于信号完整性和电源完整性前仿真和后仿真中。接下来,给大家介绍下ADS在信号完整性和电源完整性仿真方面的应用。

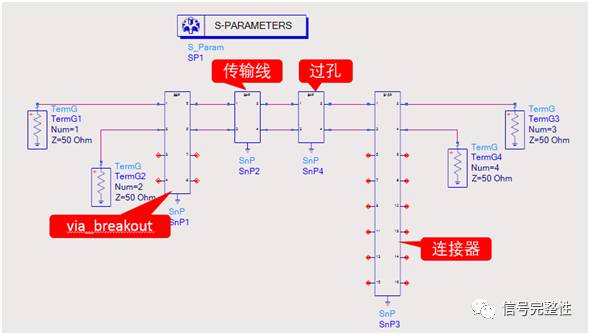

不管是在信号完整性中,还是电源完整性中,对于很多器件,包括芯片的封装、传输线、过孔、连接器、线缆、电容等无源器件都会应用S参数来表征其特性,对于一个完整的通道就需要对很多个S参数进行级联,在ADS中可以非常方便的级联各类S参数,并非常灵活的进行S参数仿真以及数据的处理,如下图2是对多个S参数的级联仿真:(【更新版】如何快速处理S参数的几种方法)

图2 S参数仿真拓扑结构

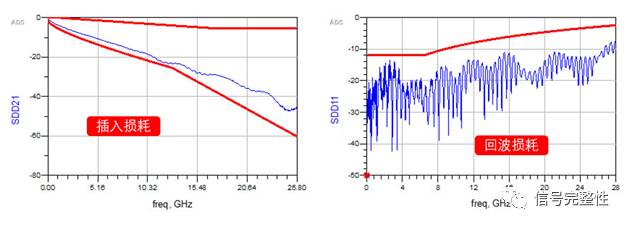

通过S参数仿真之后,在数据显示窗口,可以查看结果曲线,也可以进一步处理数据,加入规范模板等等。图3是仿真完成后处理S参数仿真结果:

图3 S参数仿真结果显示

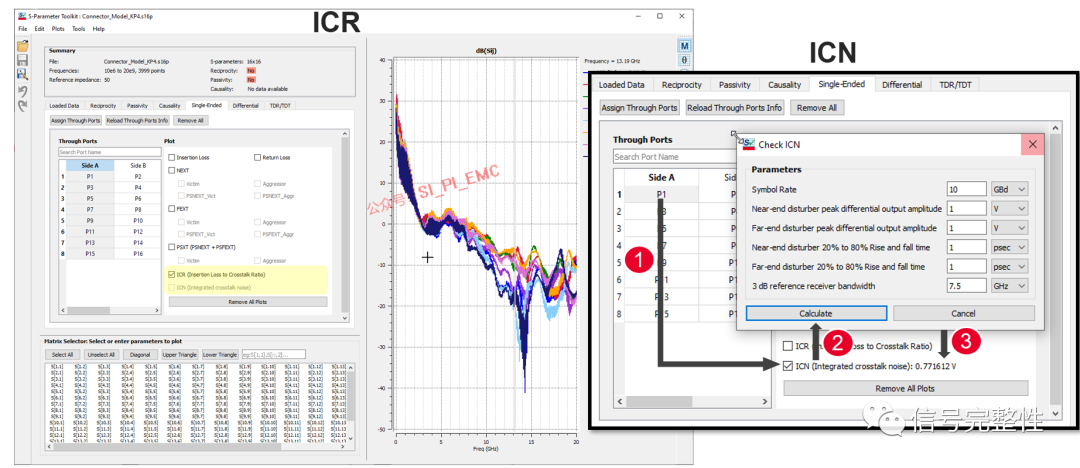

对于单一的S参数,可以在ADS中直接通过S参数查看器,检查S参数的单端和混合模式的结果,如下图4所示,在S参数查看器中,还可以检查S参数的无源性、互易性、因果性、ICNICR,还可以计算阻抗、相位以及Smith圆图。

图4 S参数查看器

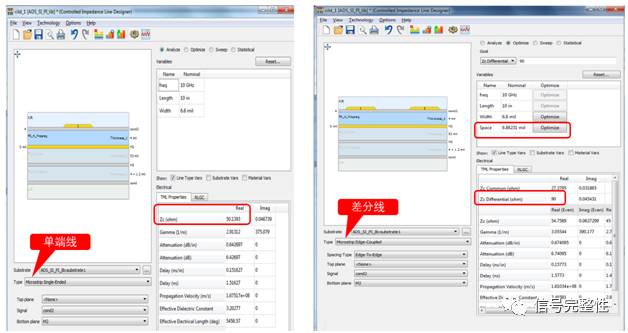

在高速威廉希尔官方网站 中,阻抗匹配非常重要,阻抗不匹配会导致信号的反射、波形非单调、误码率增加等等,所以在进行高速威廉希尔官方网站 设计之初,工程师都会考虑使用微带线、带状线还是共面波导结构,并设计一些特定的阻抗类型的传输线,比如单端50ohm、差分85ohm或者100ohm等等。在ADS中采用CILD(Controlled Impedance Line Designer)可以快速的计算传输线的阻抗,并且可以对层叠结构、传输线参数、材料参数等扫描优化,获得目标参数,如下图5所示,左图为计算50ohm的单端传输线,右图为通过优化差分对的线间距,获得90ohm差分线设计参数。(PCB板加工流程中哪些因素会影响到传输线阻抗)

图5阻抗计算

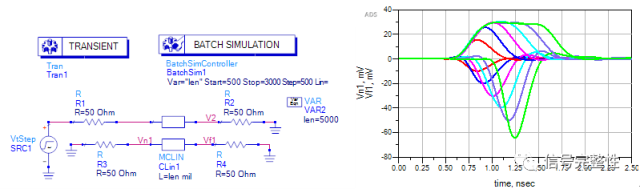

在现代电子产品追求小而精的状况下,串扰是每一位工程师必须面对的问题。如何设计可以使串扰最小且不增加成本,是工程师们的追求。在进行PCB设计之前,都可以通过ADS进行串扰仿真,以获得最优的设计,特别是在设计之初,可以对影响串扰的每一个参数进行扫描仿真,选择最合适的设计值,如下图6所示为对耦合长度进行扫描仿真的原理图和仿真结果:(在威廉希尔官方网站 设计中,什么样的串扰是可以接受的??)

图6串扰仿真

从上图的结果中在500mil~1500mil之间,近端串扰随着耦合长度的增加而增加,在1500mil之后,近端串扰达到饱和值。这只是一个粗略值的仿真,如果需要获得更精确的结果,可以进一步的减小仿真的范围。工程师也可以在ADS SIPro中对完成的PCB进行串扰的仿真,这样可以更进一步的对设计进行评估。

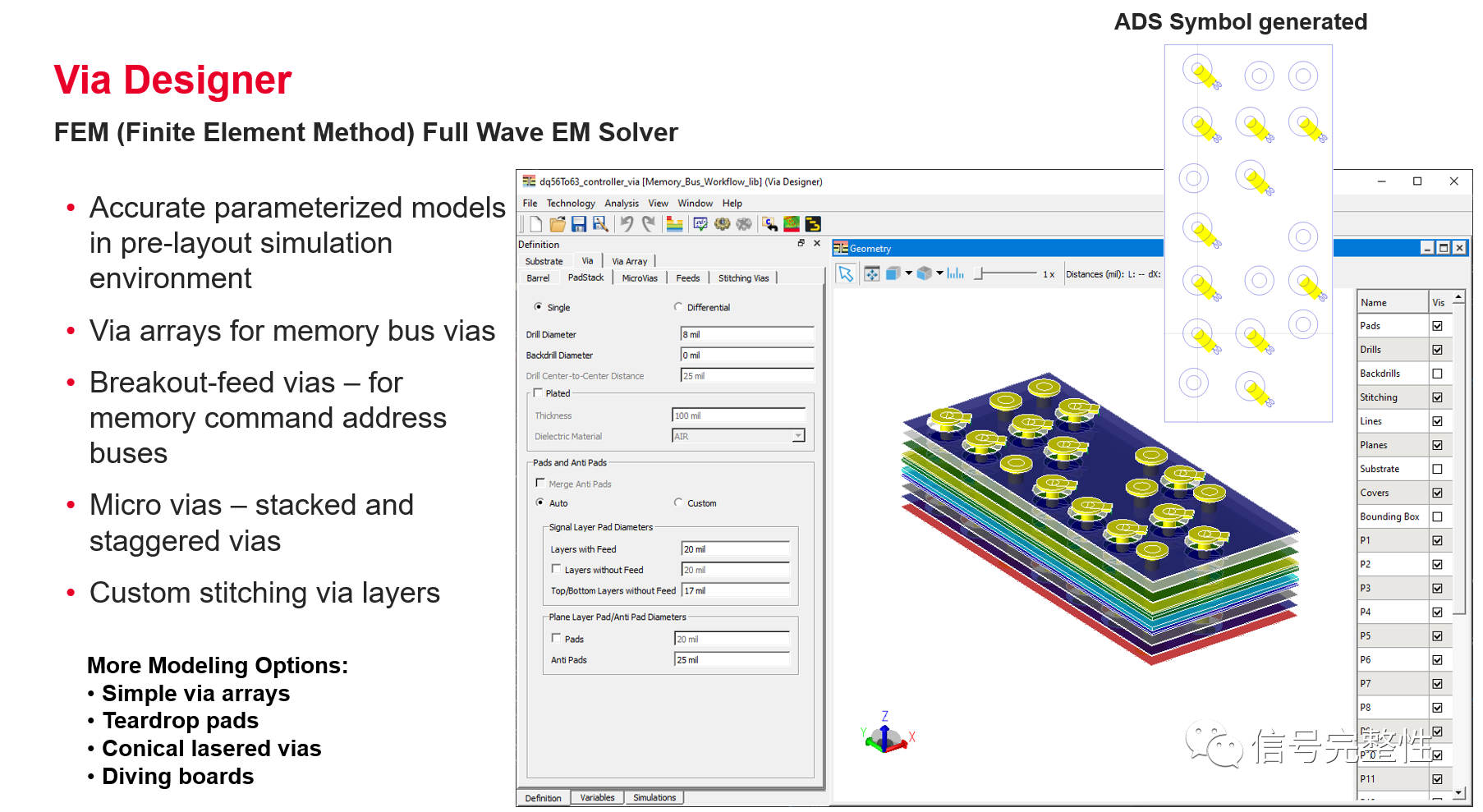

在高速串行信号链路中,基本上都会涉及到过孔的设计。过孔设计是高速串行链路设计的一个关键点,关系到高速串行链路设计的成败。工程师可以通过ADS Via Designer工具对过孔进行优化设计,如下图7所示:(高速PCB过孔仿真的流程)

图7 Via Designer

通过Via Designer仿真之后,可以查看过孔损耗和阻抗的特性,并输出S参数模型以及3D结构模型,这些模型也可以直接应用在传输链路仿真中,如下图8所示:

图8过孔模型应用在串行通道仿真中

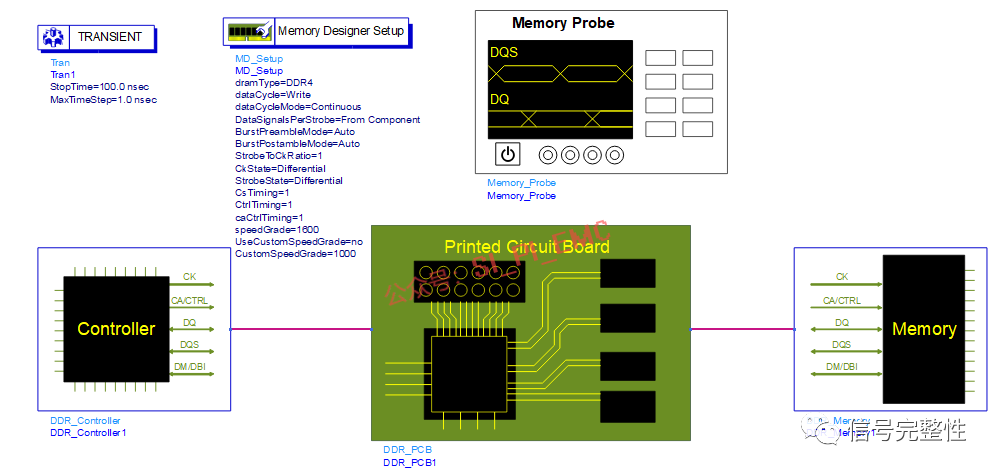

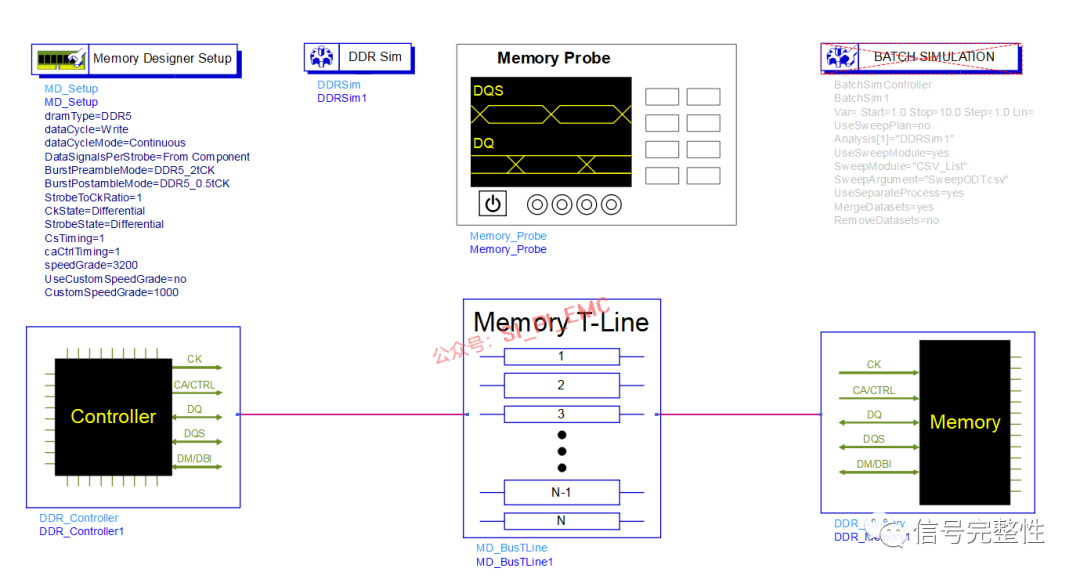

不管是计算机系统还是嵌入式系统,目前都大规模的采用了DDR5/DDR4/DDR3。不论是DDR5还是DDR4或者DDR3,其信号和电源系统的设计都是一个难点,所以不管是前仿真还是后仿真,都需要进行详细的仿真。在ADS中,工程师可以通过MemoryDesigner使用两种方式对DDR5/4/3总线进行仿真,一种是瞬态仿真,如下图9所示;一种是DDR Bus总线仿真,如下图10所示。通过仿真,可以优化、确定DDR总线的布线拓扑结构、端接电阻以及ODT的选择等等。

图9 DDR4--Memory Designer瞬态仿真

图10 DDR4--Memory Designer DDR Sim仿真

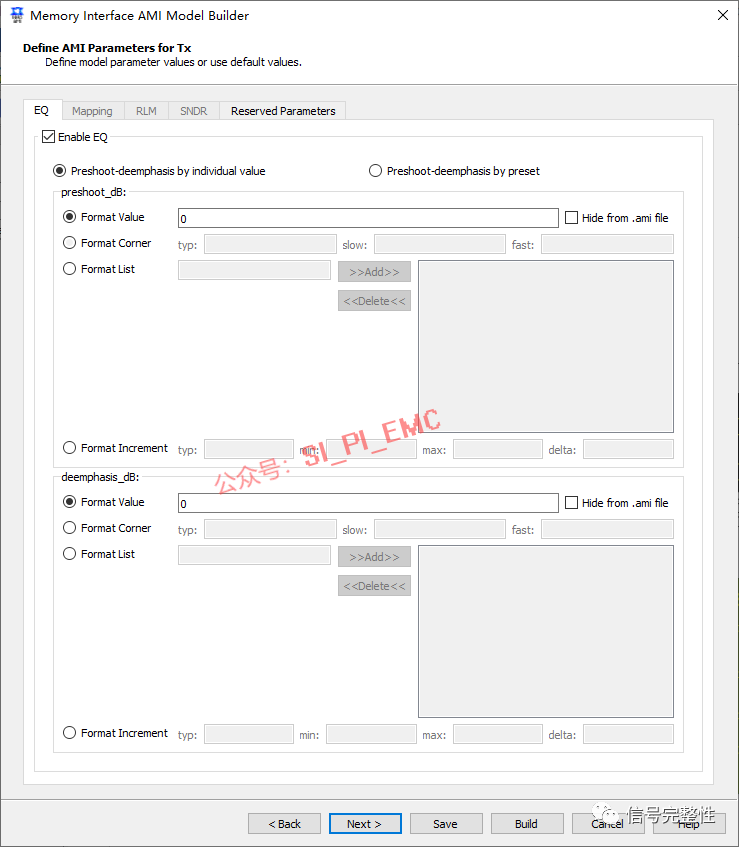

对于DDR5的仿真,有一些系统产品设计工程师无法获得模型,这个也可以在ADS中按照标准或者要求自定义DDR5的单端IBIS-AMI模型,如下图所示:

图11 创建DDR5 IBIS-AMI 模型

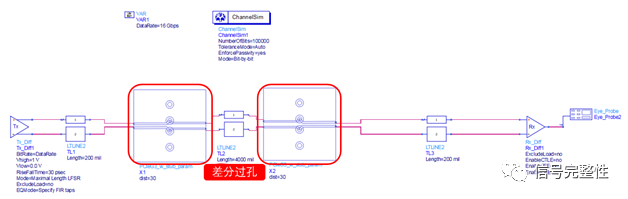

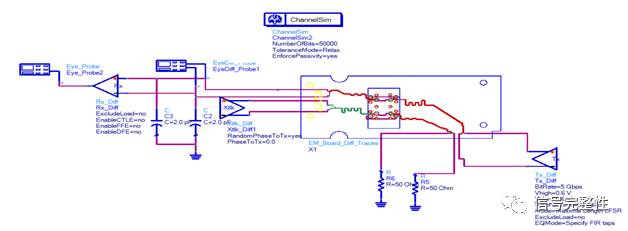

对于高速串行总线,通常对误码率有比较严苛的要求,要求误码率非常低,这才符合总线规范的要求,所以在不管是仿真还是测试,都需要有足够多的采样点数或者特殊的数学算法才能满足分析误码率的要求。另外,随着信号速率的不断提高,单纯依靠芯片简单的驱动能力无法应对信号在传递过程中的衰减,所以在高速串行总线的芯片中就会增加加重和均衡的算法,对于仿真而言,也需要有新的分析方法,这就需要使用ADS中的通道仿真(ChannelSim),如下图12所示为一个通道仿真的拓扑结构,其中包含了发送端和接收端的芯片模型、传输通道上的传输线以及连接器以及串扰通道和串扰源。芯片的模型采用的是IBIS-AMI模型。

图12 通道仿真拓扑结构

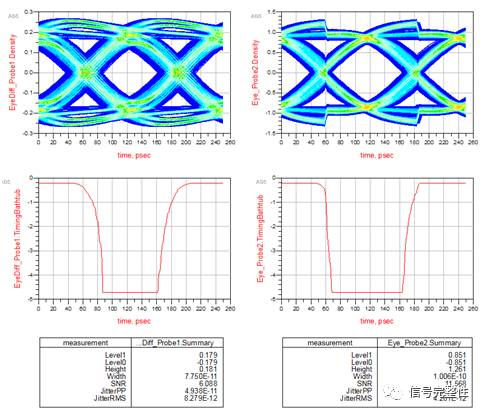

仿真完成之后,在数据显示窗口上查看波形、浴盆曲线、眼图等结果。如下图13所示:

图13 通道仿真结果

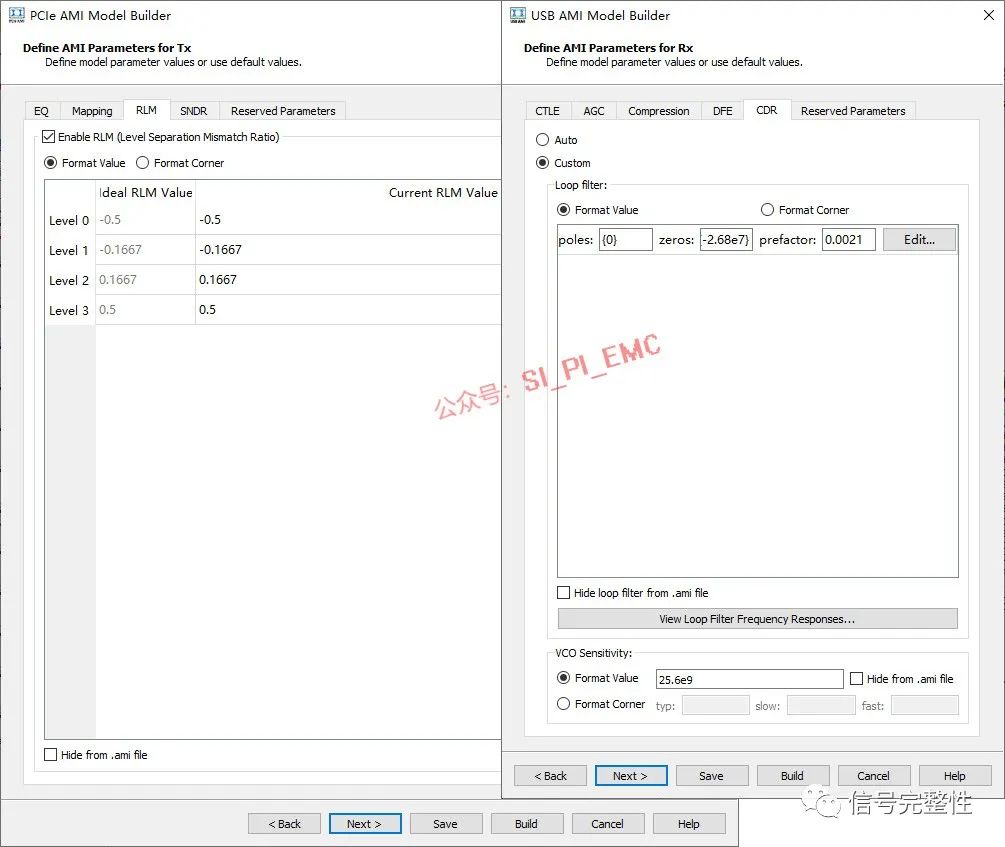

在ADS中不仅仅可以创建DDR5的IBIS-AMI模型,还可以创建PCIE, USB4和Ethernet的IBIS-AMI模型。如下图所示:

图 14 PCIe和USB4 IBIS-AMI模型创建

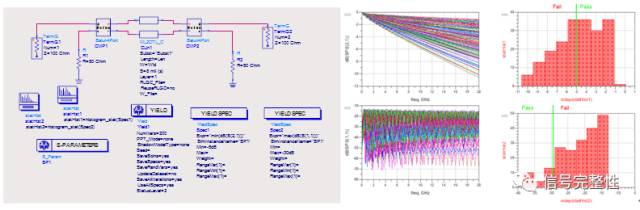

在信号完整性前仿真中,工程师不仅仅可以分析既定的一些情况,还可以针对一些不确定的情况做一些统计分析、良率的分析,比如,分析传输线长度、线宽、介电常数、介质损耗角等参数对通道的插入损耗和回波损耗的影响。图15为良率分析的拓扑结构和分析结果:

图15 良率分析

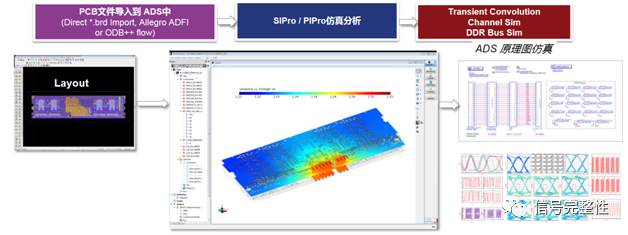

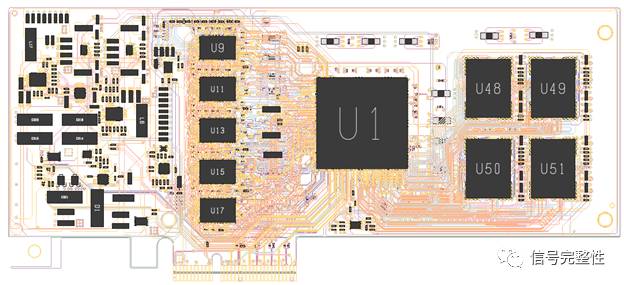

前面介绍了前仿真,主要是针对原理图阶段的仿真,目的是验证原理图设计以及给PCB设计提供约束规则。那么当PCB设计完成之后,还需要进行后仿真,这时需要把设计好的PCB文件导入到ADS中,然后再通过SIPro和PIPro进行信号完整性和电源完整性的后仿真,仿真完之后,获得结果;也可以把仿真的结果或者提取的模型导出到ADS原理图页面,做进一步的仿真。具体流程如下图16所示:(用10分钟介绍:基于ADS的电源完整性仿真流程)

图16 后仿真流程

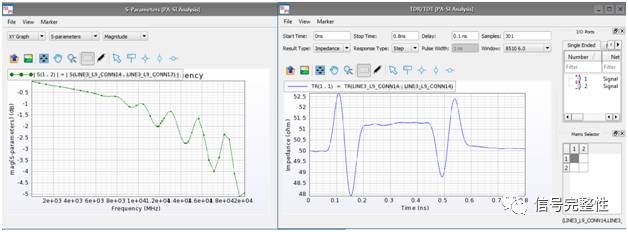

在ADS SIPro中进行信号完整性的后仿真可以获得S参数模型,同时可以查看信号网络的阻抗,并能导出S参数模型,如下图17和图18所示:

图17 SIPro中PCB仿真图

提取PCB的S参数以及分析阻抗如下图所示:

图18 SIPro仿真后的S参数和阻抗曲线

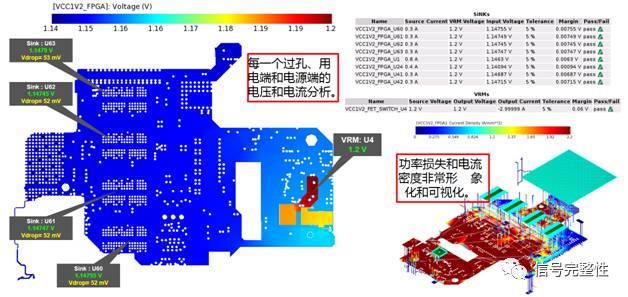

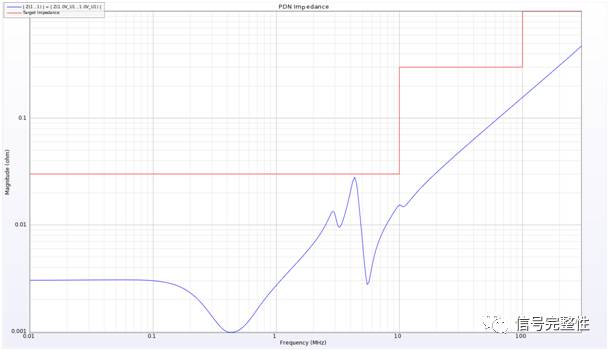

在ADS PIPro中可以进行电源完整性的直流压降仿真(PI DC)、直流电热联合仿真(Electro-Thermal)、热仿真(Thermal)、交流阻抗仿真(PI AC)和平面谐振仿真(Power Plan Resonance)。如下图19为直流压降仿真结果,图20为交流阻抗仿真结果。

图19 直流压降仿真结果

图20 PDN阻抗仿真结果

在PIPro中还可以对不满足PDN阻抗要求的设计进行去耦电容自动优化,通过对不同的电容组合、电容种类进行自动分析,找到一种最合适的设计。也可以把PDN的S参数提取之后导出到ADS原理图中,在原理图中也可以进行优化仿真分析。

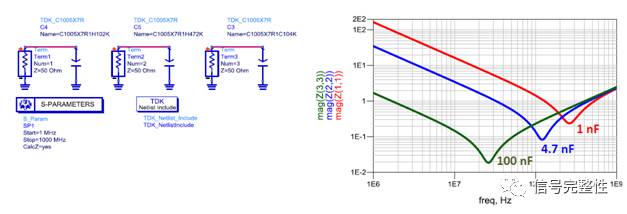

当然,也可以在前仿真中对电源完整性进行仿真,这样可以对电容的组合进行优化。在ADS原理图中建立相应的拓扑结构,如下图21所示:

图21 电容阻抗仿真

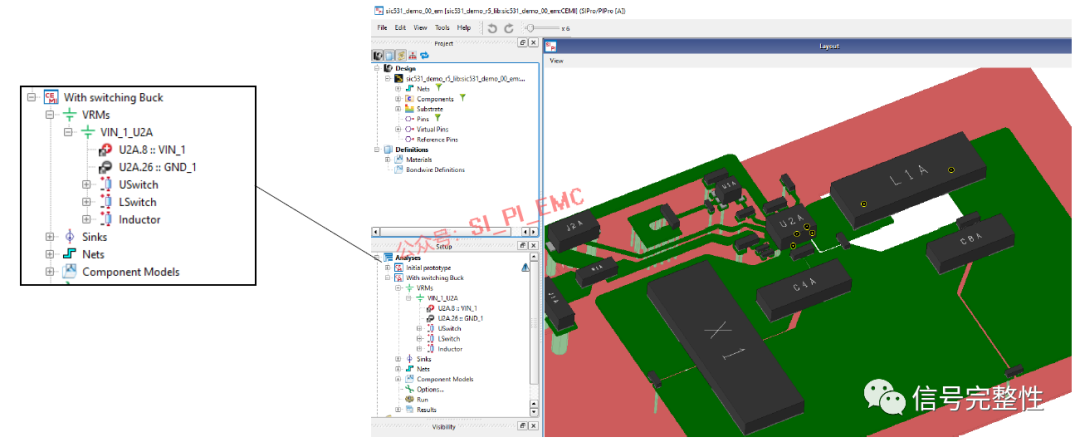

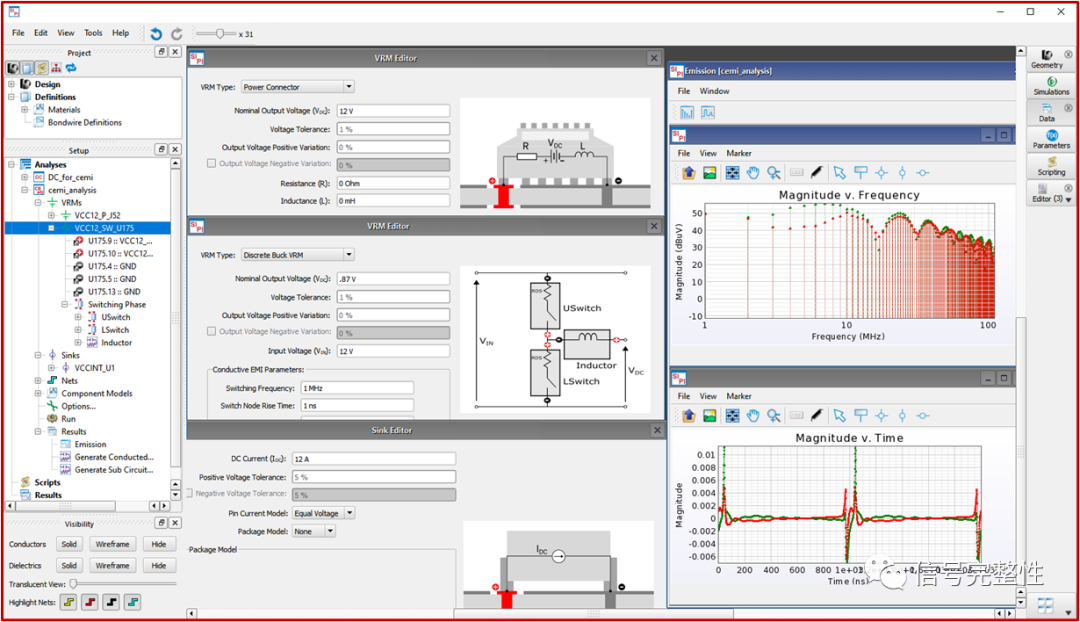

随着电磁环境越来越复杂,在ADS中也增了传导的仿真,在仿真完成PI之后,可以直接把工程复制成CE(PIPro CEMI)的仿真,如下图所示:

图22 ADS CEMI仿真

仿真设置和结果如下图所示:

图 23 ADS 传导仿真设置和仿真结果

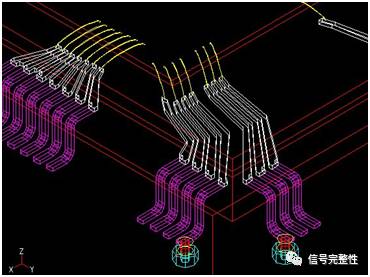

在信号完整性仿真阶段,EMPro也是不可或缺的工具,特别是对于一些比较复杂的结构,比如具有芯片封装、连接器、线缆的互连通道,就需要使用EMPro进行电磁模型的提取。如下图22所示EMPro中进行芯片封装的仿真:

图24 芯片封装仿真

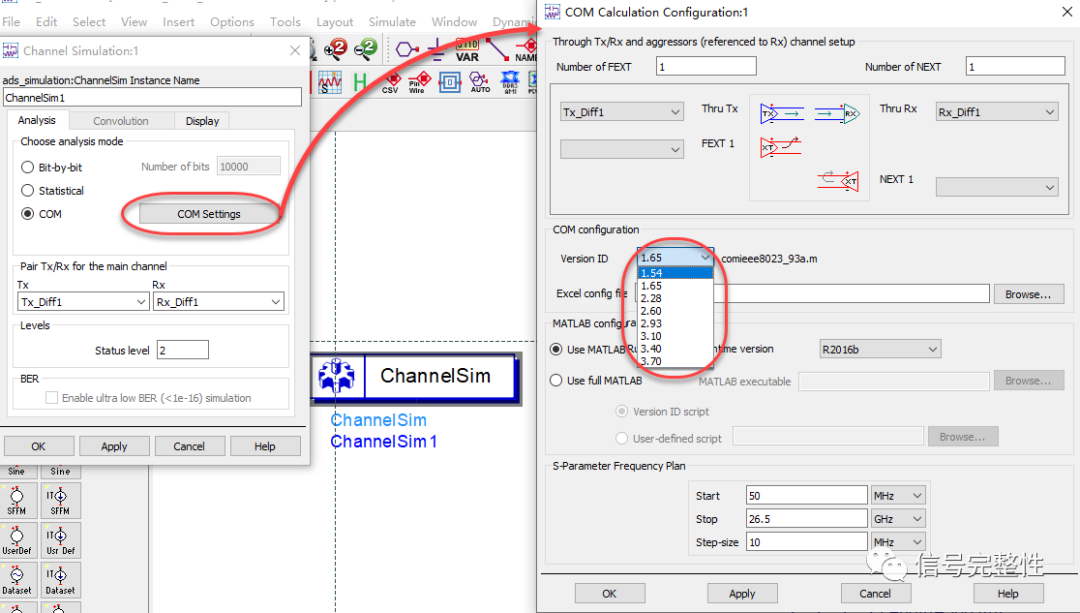

随着技术的发展,信号完整性和电源完整性设计和仿真也变得更加的复杂,这对工具的要求也越来越高。比如计算COM、ERL:

图25 COM 仿真设置

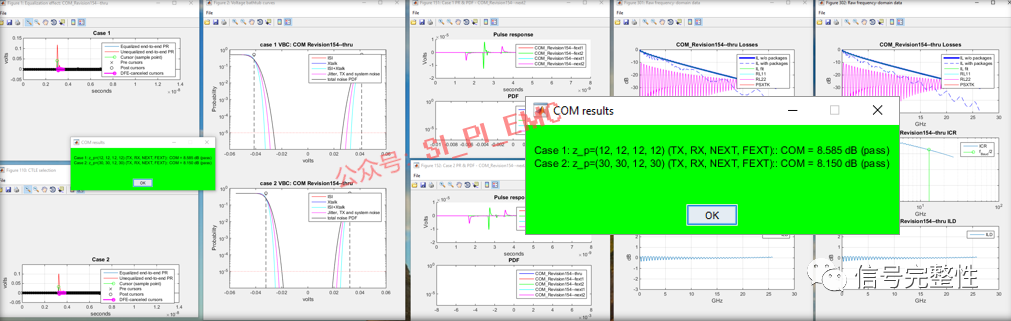

COM仿真结果:

图26 COM仿真结果

总之,不管是信号完整性和电源完整性的前仿真还是后仿真,或者,不管是板级的仿真还是系统的仿真,是德科技都能提供一套非常系统的解决方案(ADS+EMPro+SystemVue)。

审核编辑:汤梓红

-

信号完整性仿真应用2009-11-25 0

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 0

-

信号完整性与电源完整性的相关资料分享2021-11-15 0

-

信号完整性为什么写电源完整性?2021-11-15 0

-

详解信号完整性与电源完整性2021-11-15 0

-

什么是电源和信号完整性?2021-12-30 0

-

信号完整性与电源完整性仿真分析2011-11-30 1823

-

ADS的信号完整性和电源完整性仿真应用方案2017-12-04 32045

-

谈谈电源完整性仿真的必要性2020-12-07 3209

-

信号完整性与电源完整性的仿真2021-09-29 1315

-

大话电源完整性2022-01-07 638

-

高速威廉希尔官方网站 信号完整性分析与设计—信号完整性仿真2022-02-10 1568

-

信号完整性和电源完整性的分析2023-04-10 2406

-

信号完整性与电源完整性-电源完整性分析2024-08-12 974

全部0条评论

快来发表一下你的评论吧 !