评价时钟树质量的方法

电子说

描述

时钟树综合,通常我们也叫做CTS。时钟树综合就是建立一个时钟网络,使时钟信号能够传递到各个时序器件。CTS是布局之后相当重要的一个步骤,如何评价一个时钟树的好坏,这个问题可以每个人心中都有不同的答案。

通常各个公司已经约定俗成了一套评价时钟树的方法,我们也称为clock tree metrics。包括以下几点:时钟的传播延迟(Latency),时钟偏差(Skew),时钟转换时间(transition),时钟不确定性( uncertainty),时钟的级数(level)……

这些metrics保证了时钟的完成性,如何在这些metrics中寻找一个最佳方案,也就保证了时钟树的好坏。

时钟的传播延迟(Latency)

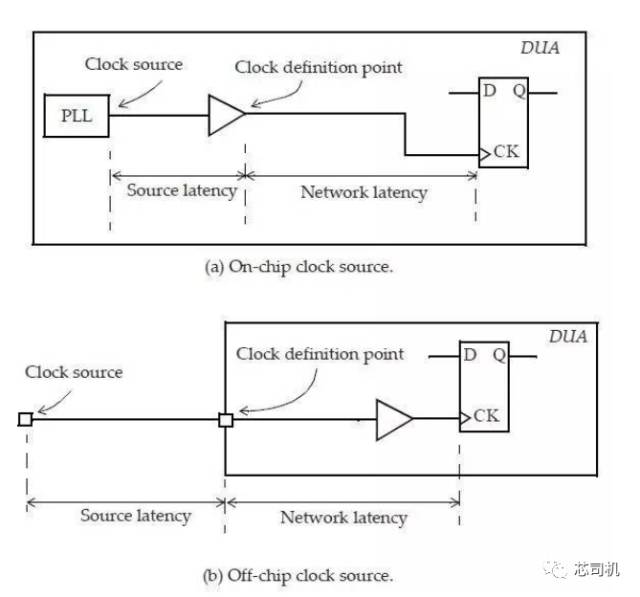

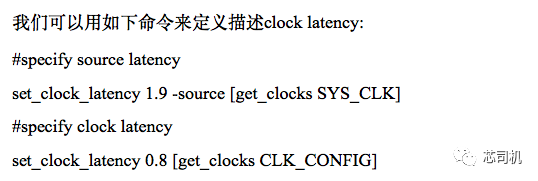

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。主要指从Clock源到时序组件Clock输入端的延迟时间。它可以分为两个部分,时钟源插入延迟(source latency)和时钟网络延迟(network latency)

source latency:主要指从clock source端到clock定义端的延迟,即是时钟源(例如PLL)到当前芯片时钟根节点(clock root pin)之间的延迟。

network latency:主要指从clock定义端到时序器件的clock pin端的延迟。

以下两张图分别定义了片上(on chip)和片外(off chip)中clock latency的描述

那latency值有什么用呢?其实这相当于一个target值,CTS的engine会根据你设置的latency值来插入buffer(当然只是对network latency操作),做出一个接近于你设定的值,可能多一点,也可能少一点。latency值的大小直接影响着clock skew的计算和固定。因为我们的时钟树是以平衡为目的,假设你对一个root和sink设置了1ns的latency值,那么对另外的几个sink来说,就算你没有给定latency值,CTS为了得到较小的skew,也会将另外的几个sink做成1ns的latency。过大的latency值会受到OCV和PVT等因素的影响较大(因为有time derate的存在)。

时钟的偏差(skew)

时钟偏差(skew),这是CTS中相当重要的一个概念。在CTS中,由于时钟到每个寄存器的路径延迟不一样,造成信号到达 clock pin 的时间也不一样,寄存器也不会同时翻转。Skew 的定义就是最长路径延迟减去最短路径延迟的值。一直以来,Skew都是衡量时钟树性能的重要参数,CTS的目的就是为了减小skew。

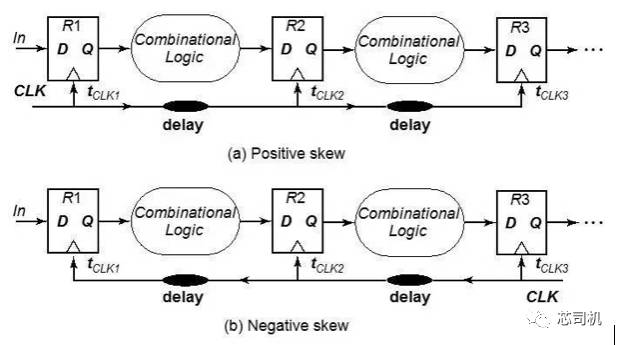

Skew的类型分为很多种,根据clock和datapath的方向,skew可以分为positive skew和negative skew。如下图所示:

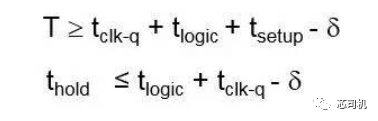

对于positive skew,clock和data path在相同方向上。反之对negative skew来说,clock和data path在相反方向上。那它们对我们的design有什么影响呢?我们来看一下setup和hold的计算公式(这个公司大家应该很熟悉吧):

我们可以得到以下结果

对于positive skew来说,它可以减少T的时间,相当于提升芯片的performace。但是它的hold时间会变得更加难以满足

对于negative skew来说,它的hold时间更加容易满足,取而代之的是,它会降低芯片的性能。

还有另外一种skew的分类方法,是我们更为常见的,根据时钟域以及路径关系, skew 可以分为 global skew , local skew , interclock skew。

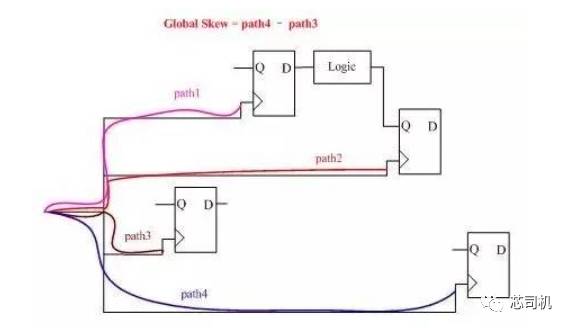

Global skew 是指,同一时钟域,任意两个路径的最大 skew ,如下图所示。CTS时,工具更关注的是global skew, 会尽可能地将global skew做小

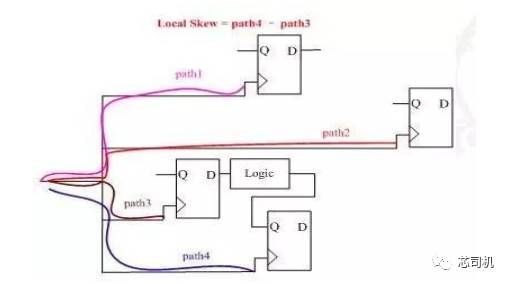

Local skew 是指,同一时钟域,任意两个有逻辑关联关系的路径最大 skew ,如下图所示,我们在分析timing的时候,更多地是关注local skew

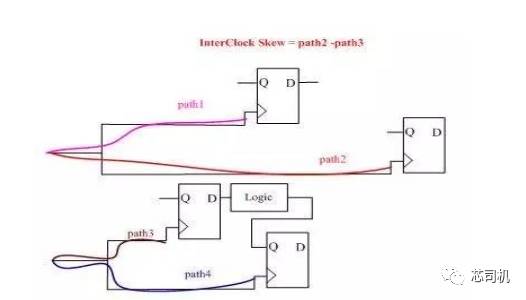

interClock skew 是指,不同时钟域之间路径的最大 skew,如下图所示:

另外还有一种比较特使的skew就是现如今用得较多的useful skew,它也是ccopt这么红火的一个特色。大概说一下useful skew的概念。

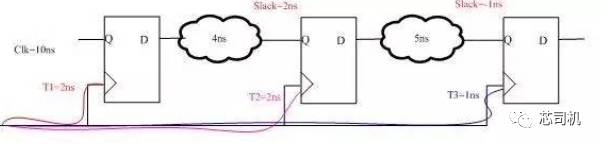

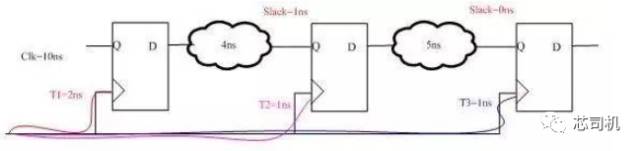

如下图:时钟周期为 10ns ,各时钟路径延迟如下:可以看到有一条路径的 slack 为 -1ns ,说明这条路径违规。可以看到与这条路径相关的 skew 是 T3-T2= -1ns 。

下面我们利用 useful skew 向前面一个 slack 比较充裕的路径(slack=2ns)借点 time ,来修正现在这条路径。如下图:

这就是 useful skew 的作用,可以向前,或者向后借time来修正 violation。

时钟转换时间(transition time)

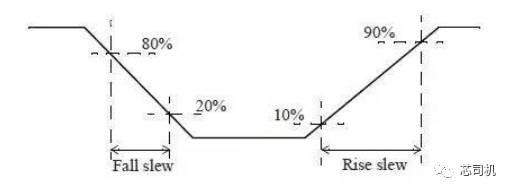

时钟转换时间clock transition time ,也称为clock slew。通常是指电压从10%VDD上升到90%VDD所需要的时间,或者是从90%VDD下降到10%VDD所需要的时间,上升和下降时间过长意味着威廉希尔官方网站 的速度很慢。如下图所示

在sdc中,用以下命令来限制slew大小

set_max_transition 0.1 -clock_path[all_clocks]

对CTS来说,这也是一个target值,当你设定了一个slew target后,CTS engine会通过插入buffer或者upsize等操作,尽可能地去满足整个target值。当然,slew也不是越小越好,过小的slew会导致CTS阶段在clock path上插入过多的buffer,从而影响到skew的balance以及功耗和面积。

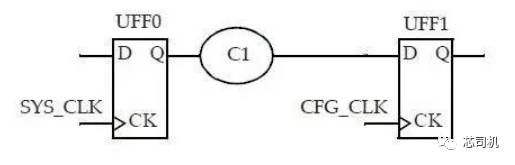

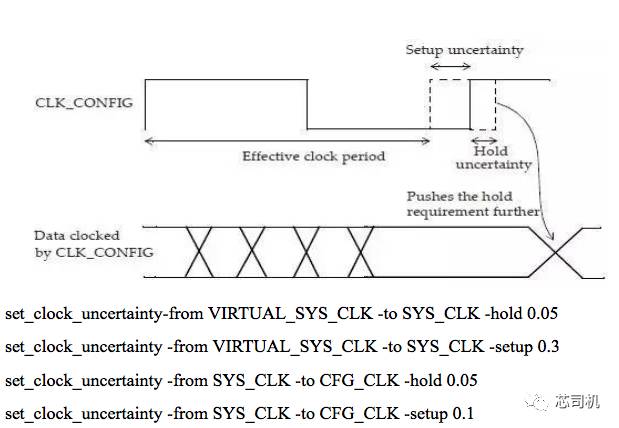

时钟不确定性(clock uncertainty)

定义了Clock信号到时序器件的Clock端可能早到或晚到的时间。主要是用来降低时钟抖动jitter对有效时钟周期的影响。值得注意的是,在setup check中,clock uncertainty是代表着降低了时钟的有效周期;而在hold check中,clock uncertainty是代表着hold check所需要满足的额外margin。

来看下面一条reg2reg path. 对照着如下时钟波形图。可以写出下面的约束。

在pre-CTS的时候,我们将时钟的不确定性设定为target的skew和jitter值之和来模拟真实的时钟;而post-CTS之后,时钟树propagate delay已经确定,skew真实存在,所以uncertainty就是时钟的真实抖动值。因此preCTS的target skew不能设置的太大或者太小,这样会造成preCTS和postCTS的correlation不好。总结一下:

在pre-CTS中,

setup的clock uncertainty = jitter + clock tree skew

hold的clock uncertainty = clock tree skew

在post-CTS中,

setup的clock uncertainty = jitter

hold的clock uncertainty = 0

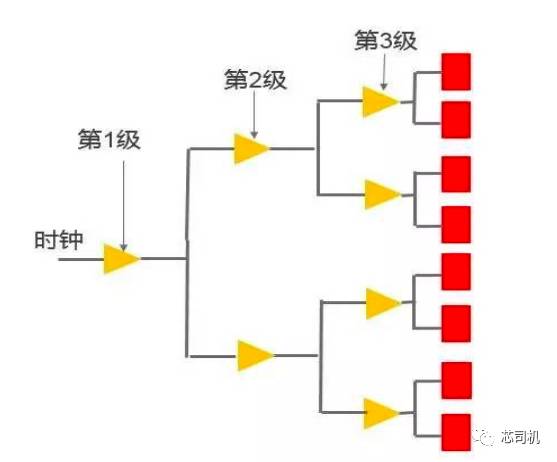

时钟树级数

时钟树其实是由buffer一级一级串行级联下去组成,每一个分结点就化分成一级,如下图所示

通常来说,我们期望时钟树的级数越少越好,因为这样tree上的common path最长,受到OCV和PVT因素的影响也最小,时钟的性能也最好。但是,这样情况下tree很难去生长完成,并且会导致过多的fanout,导致负载过大,延迟变差。因此这也是一个trade off 的过程。

评价时钟树质量,可以看主干分岔点是否过早、关键寄存器的级数是否最少且Size合理、Leaf寄存器分组是否合理,当然skew,area,power也是很重要的啦~

-

STM32F407系统时钟配置时钟树方法2021-08-12 0

-

色彩复原图像的质量评价方法2017-12-18 653

-

音频质量客观评价中同步方法的研究与实现2011-03-12 0

-

前后端协同的时钟树设计方法2009-04-21 827

-

基于视觉感兴趣区的图像质量评价方法2009-08-11 602

-

图像质量评价方法研究进展2010-02-09 476

-

时钟树优化与有用时钟延迟2011-10-26 4426

-

时钟网格与时钟树设计方法对比研究2012-05-07 2045

-

基于灰度特征的虹膜图像质量评价方法_罗晓庆2017-03-16 672

-

基于视差图图像质量评价2017-11-22 860

-

LUCT工具主要特性及不确定性时钟树设计方法和算法的介绍2017-11-29 1536

-

时钟树的使用方法简介2020-03-08 8694

-

基于深度学习的视频质量评价方法及模型研究2021-03-29 793

-

数字IC设计中的分段时钟树综合2023-12-04 2080

-

时钟树是什么?介绍两种时钟树结构2023-12-06 1733

全部0条评论

快来发表一下你的评论吧 !