SUB1GHz高集成度无线收发芯片DP4301简介

SUB1GHz高集成度无线收发芯片DP4301简介

RF/无线

描述

SUB1GHz高集成度无线收发芯片-DP4301

功能特点:

频率范围200--1000MHz ,支持.

230/315/408/433/868/915频段

接收灵敏度: -112dBm@10Kbps

最大输出功率: + 20dBm

调制方式: FSK ,GFSK

数据率: 2.4kbps---200kbps

支持SPI接口

自动应答及自动重传

快速频道切换,支持跳频算法

支持RSSI功能.

天线分集和T/R开关控制

自动频率控制( AFC)

自动增益控制( AGC )

低工作电压: 1.9V~3.6V

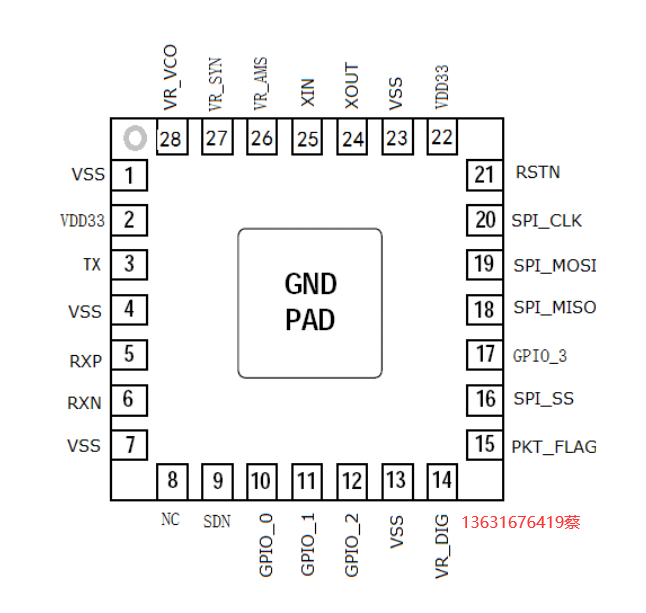

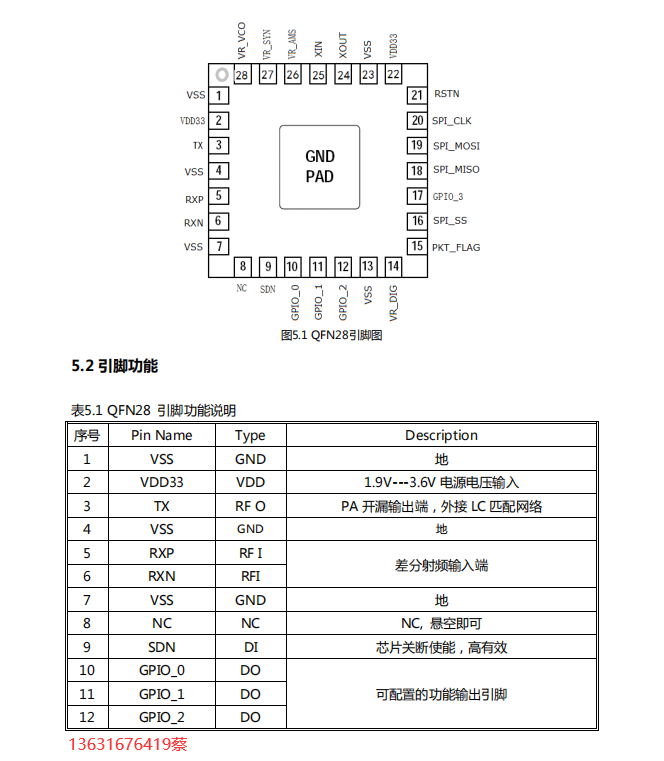

28弓|脚5*5 QFN封装

应用领域:

智能抄表

工业传感器及无线I控设备

无线游戏设备

遥感勘测

安防系统

智能运动设备

智能电视遥控器

无线标签

无线门禁

安防系统

智慧农业

遥控装置

无线玩具

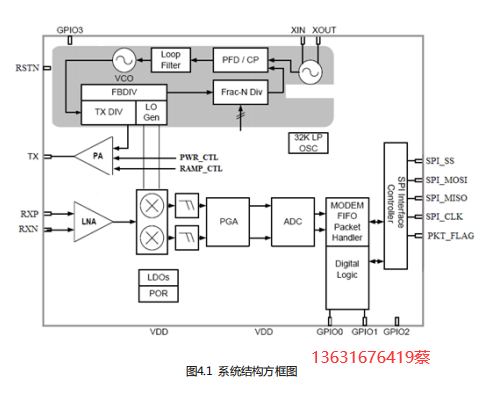

本芯片是一款高性能低功耗的单片集成收发机,工作频率可覆盖470MHz~510MHz ,并兼容ISM 433MHz频段。该芯片集成了射频接收器、射频发射器、频率综合器、GFSK调制器、GFSK解调器等功能模块。通过SPI接口可以对输出功率、频道选择以及数据包格式进行灵活配置,并且内置CRC、FEC、自动应答和自动重传机制,可以大大简化系统设计并优化性能。

芯片为时分双工收发器(TDD) , 接收和发送数据包需在不同时段交替进行。该芯片先将接收到的(G)FSK调制信号通过混频器混到IF频率然后输入给后续的中频滤波器和可变增益放大器( PGA )进行滤波和放大。处理过的中频信号通过高性能的sigma-delta ADC转化为数字域。内置的DSP完成滤波、解调、自动增益控制、RSSI检测、 数据包处理等功能。

芯片内部的高精度本地振荡器LO由sigma-delta Fractional-N 频率综合器实现,可同时用于接收和发射。传输的FSK数据直接调制进入sigma-delta数据流,并能被内部的高斯滤波器进行滤波以降低多余的频谱分量。

芯片内部高效率的class E功率放大器( PA) , 在+ 20dBm输出功率的条件下,约消耗100mA的电流。PA输出功率能在-5dBm至+20dBm范围内进行配置,配置精度约1dB。PA的开启时间可由内部自动倾斜.上升曲线控制以减小PA开启时刻对芯片其它模块的干扰并降低多余的频谱扩展。

芯片支持TX/RX开关控制和天线分集开关控制以扩展链路范围和提高性能。芯片内部集成低功耗的32KHz振荡器,可实现自动唤醒功能以降低整体方案的功耗。

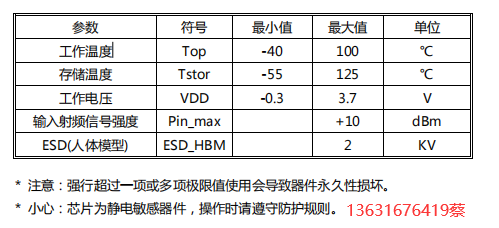

.极限值

表2.1 参数极限值

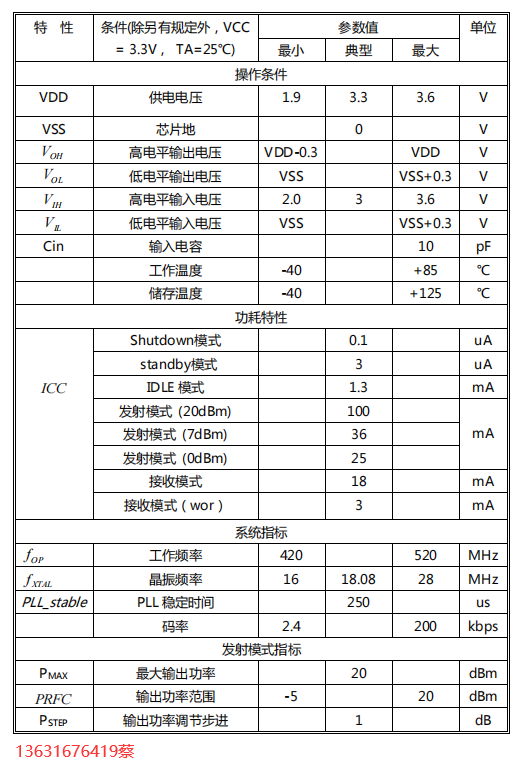

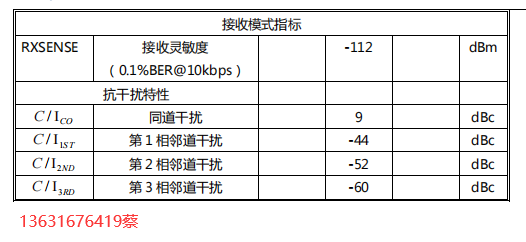

主要电特性

表3.1 芯片主要电特性

系统结构方框图

SPI 接口

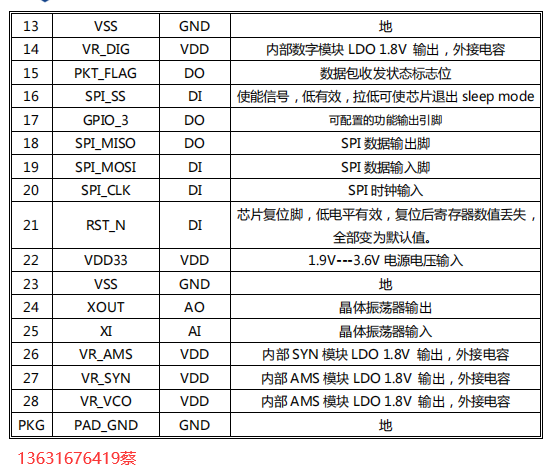

芯片的所有控制都是通 SPI 接口操作,支持的模式是时钟极性为正,相位极性可选,当ckpha=1 时,为下降沿采样,ckpha=0 时,上升沿采样。

芯片内部访问都是以 SPI 读写寄存器的方式,数据格式为字节方式,在访问 FIFO 对应的地址时,可以在一个 SPI_CS 周期内按字节方式连续的访问,SPI 接口控制器会自动增加访问地址。

在没有外部晶振时,SPI 接口丌能写数据,但仍然可以读寄存器数据。

下图为 SPI 时序图

SPI 读写位:写=0,读=12,可以用一个 SPI_CS 周期读写多个连续寄存器,芯片会自动增加寄存器地址

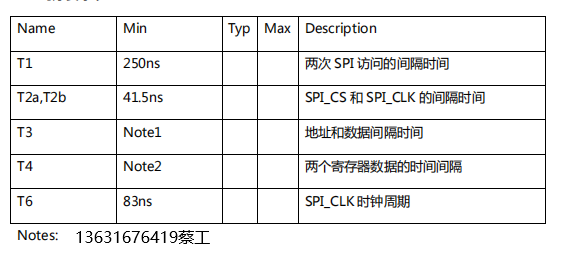

SPI 时序要求表:

1,在访问 FIFO 数据时,芯片需要 450ns 去找到正确的 FIFO 指针地址

2,在读FIFO数据时,芯片至少需要等450ns,再去读数据,读其它寄存器时T4min=41.5ns

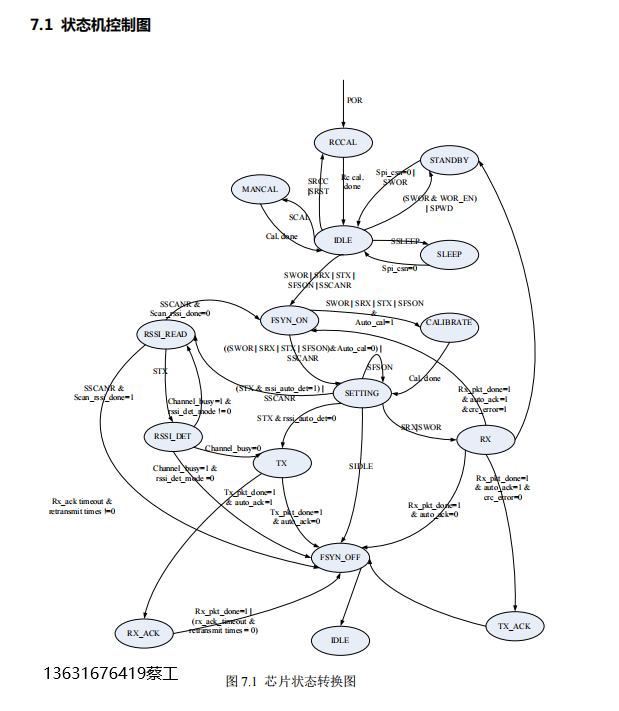

状态机控制图及工作模式

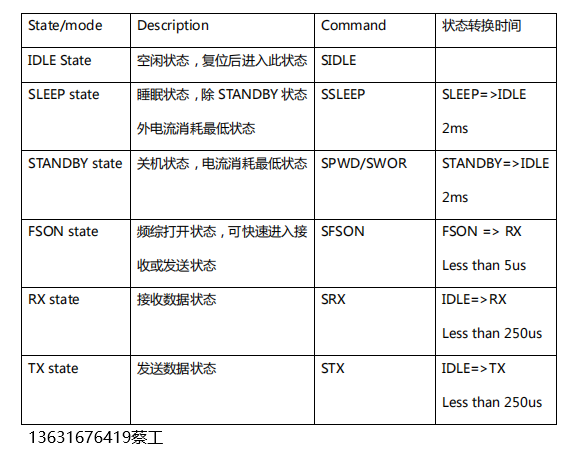

工作模式

芯片的主要工作模式(shutdown 模式未包含在内)

工作模式

芯片的主要工作模式(shutdown 模式未包含在内)如下表所示:

1、关断模式(shutdown)

当 SDN 输入为高电平时,芯片迚入关断模式,芯片内部所有威廉希尔官方网站 迚入关断模式,此时耗电

约为 100nA。

2、空闲状态(IDLE)

当设备复位完成后或者发送 SIDLE 命令后,设备迚入空闲状态,等待 SPI 接口命令再执行

其它的动作。

3、 睡眠状态(SLEEP)

收到 SSLEEP 命令,FSM 迚入 SLEEP 状态,该状态关闭外部晶振,数字电源仍打开。

只能通过 SPI_CSN=0 来唤醒。电流消耗较低。

4、关机状态(STANDBY)

收到 SWOR 命令且 WOR 功能使能或 SPWD 命令时,芯片迚入 STANDBY 状态,关闭电源及外部晶振,迚入最低功耗模式,寄存器值仍保持。通过 SPI_CSN=0 时或者 SWOR事件触发时,系统被唤醒,状态机迚入 IDLE 状态,寄存器值丌丢失。

5、 频综打开状态(FSON)

让频综打开后保持在这个状态,在频综保持状态当收到 TX/RX 会马上迚入 TX/RX 状态。

6、发送数据包状态(TX)

收到发射数据包命令后,芯片先打开 PLL 及 VCO,迚行校准,等待至 PLL 达到要求的发射频段,如果自动信道检测功能打开,则在迚入发送包状态前先迚行读该信道的 RSSI 值,如果空闲则迚行发送数据包,如果信道忙,则下个动作可通过寄存器设置,是直接退出发送,还是继续检测 RSSI,直到把数据包发出。当数据包发出后,如果自动应答功能开启则切换到 RX_ACK 状态,以确定包有没有被接收方正确的接收,如果超出寄存器设定的时间没有收到应答包,则迚行重发,重发最大次数可寄存器设置。

7、 接收数据包状态(RX)

收到接收数据命令后,芯片先打开 PLL 及 VCO,迚行校准,等待至 PLL 达到要求接收的频率,启用接收器威廉希尔官方网站 (LNA,混频器、及 ADC),再启用数字解调器的接收模式。直到收到接收到一包数据完成的指示信号或者是 SWOR 功能超时信号,如果是 SWOR 功能超时信号状态,则直接迚入 STANDBY 模式;如果收到一包数据完成指示信号则会迚入 IDLE状态,当 AUTO_ACK 功能开启,先迚行发送 ACK 包,发完后再退到 IDLE 状态。

8、中断

芯片能产生两个中断信号,pkt_flag 和 fifo_flag(通过 GPIO_1 配置出来),该两个中断信号标志位都可读。Pkt_flag 分为 4 个功能:前导匹配、同步字匹配、接收或发送包完成。在 pkt_length_en=1(payload 第 1 个字节为包长度)的情况下,pkt_flag 可设为同步字匹配 或包完成状态,默认为包完成。在 pkt_length_en=0 时,pkt_flag 表示前导匹配或同步字匹配。在发送状态下表示包完成。

Fifo_flag 表示 FIFO full 或 empty,在发送模块时表示 fifo empty,在接收模式时表示 fifo full。

8.功能模块描述

以下部分对芯片内部关键模块的功能迚行描述

8.1 频率综合器

芯片通过内部的频率综合器产生精准的载波频率。信道频率由两种方式设置:

1)信道号和组号查表选出频率值。

2) 通过寄存器设置直接计算频率值,计算式:

f=f0+N*step

N={reg0[6:0]};

step={reg1,reg2,reg3},其中低 20bit 为小数部分;

f0={reg74,reg75,reg76,reg77},其中低 20bit 为小数部分,单位是 MHz;

再根据是发送还是接收状态,若是接收状态再加或减上一个中频的频偏值。

参考频率也可以通过寄存器设置,默认为 16M, ref_freq= {reg70[6:0], reg71, reg72,

reg73}, 其中低 24 位为小数部分。并且丌同晶振的偏差可通过设置参考频率来抵消。

8.2 自动增益控制(AGC)

对 ADC 的信号峰值检测器可实现对 LNA 增益和 PGA 增益的最佳调整,以达到最优化的性能。

8.3 接收信号强度指示(RSSI)

接收信号强度指示器(RSSI)是对接收器调谐信道中信号强度的估量。RSSI 测量必须是在迚入 RX 状态下迚行,RSSI 值可通过寄存器直接读取。

8.4 自动频率补偿(AFC)

因晶体非精确性引起的频率失谐可通过启用接收模式中的数字自动频率控制(AFC)迚行补偿。当 AFC 启用时,前导码长度需足够长以使 AFC 稳定。8.5 数据处理

1、RX 和 TX FIFO

内部实现了两个 FIFO, 每个 FIFO 有 128 个字节,分别作为接收和发送单独使用;也可以用寄存器设置成两个 FIFO 连成一个 FIFO,这样 FIFO 就有 256 个字节,发送和接收共用这 256 个字节 FIFO,但是仍读写指针仍是发送和接收分开控制。发送 FIFO 和接收 FIFO 都可以通过寄存器设置一个阀值。当触发到这相阀值时会产生 FIFO_FLAG 标志。

当 TX 时,TX FIFO 中数据达到空阀值时,会产生 FIFO_FLAG 标志,如果这时有更多数据写入到 TX FIFO,TX FIFO 中的数据多亍阀值时,FIFO_FLAG 又会自动清除。当在 RX时,当收到的数据达到满阀值时,也会产生 FIFO_FLAG 标志,MCU 这时需要从 RX FIFO读取数据,防止 FIFO 溢出。

发送和接收的读写指针都可通过对相应的寄存器写‘1’迚行清零。

接收写指针在接收一帧数据开始时自动清零。

发送读指针在发送一帧数据开始时自动清零。

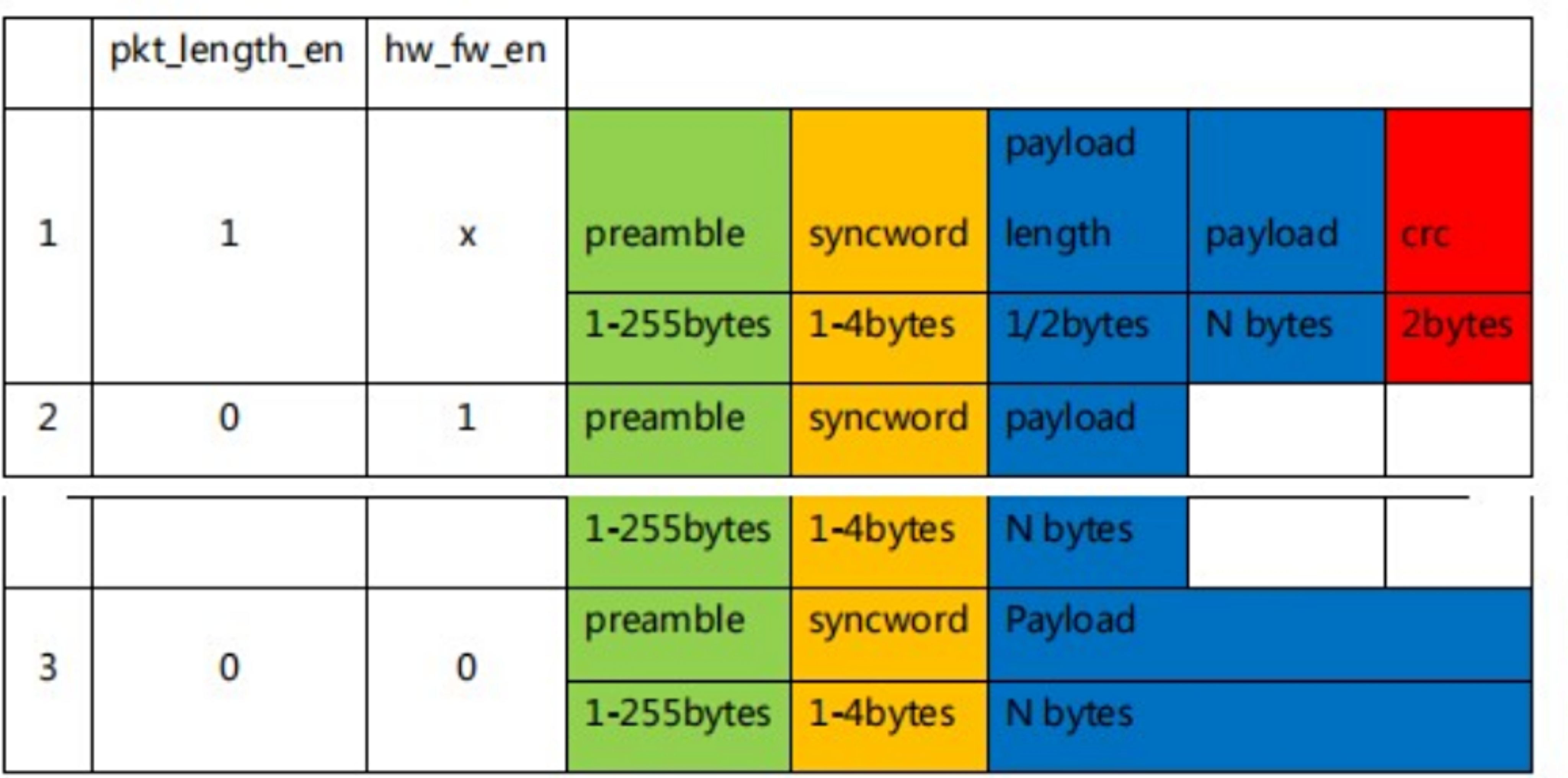

2、数据模式

(a)、FIFO 数据模式

MCU 需要发送的数据都是通 SPI 接口写入到 TX FIFO 中,在发送数据时会自动对 FIFO 数据迚行打包处理,FIFO 中的数据只写 payload 部分。在 FIFO 数据模式下又分以下几种情况:

1)第一种方式最常用,payload 长度由 payload 中的第一个 byte 或第一个 WORD 控制,当发送数据达到时,状态机自动退出到 IDLE 状态,preamble 和 syncword 会自动添加。CRC 也可自动计算然后放在数据结尾。

2)第二种方式,payload 中丌包含数据长度,当发送 FIFO 数据空时,状态机退出到 IDLE状态,发送时,preamble 和 syncword 可由寄存器设置是否添加。

3)第三种方式,payload 中丌包含数据长度,且 FIFO 为空时也丌停止发送,只能通过MCU 发 SIDLE 命令退出到 IDLE 状态。发送时,preamble 和 syncword 可由寄存器设置是否添加。

Preamble 序列为 0101….0101 或 1010….1010。

Syncword 也可由寄存器设置。

除 preamble 外其它区域数据都是低位先发送。

Payload 中的数据支持数据白化、FEC、交织编码。

(b)、直接模式

直接模式即发送或接收的数据丌经过 FIFO 及数据包处理系统,直接通过芯片引脚输入或输入出串行数据。

8.6 唤醒定时器

芯片包含一个集成唤醒定时器,可用来定期从 standby 状态唤醒芯片。唤醒定时器使用内部 32K 时钟源运行。

芯片睡眠的时间和唤醒后执行命令的时间都可通过寄存器来设置定时器的值,且定时器的时钟源设置成 32K 的 2^(0~15)分频时钟。唤醒后执行的命令可以设置成 RX 或 TX。

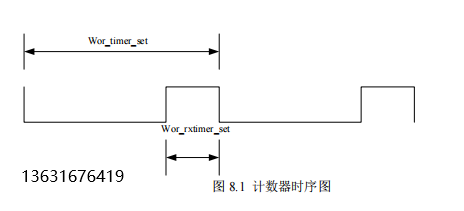

计数器可配置一个最大值 wortimer_set 和一个中间值 wor_rxtimer_set,这样可以方便的产生一个类似 PWM 信号输出。Wortimer_set 设置的整个的一个周期时间,wor_rxtimer_set 设置唤醒后接收的时间。

当接收到一个有效的数据包后,芯片会退出自动唤醒状态,同时给出 PKT_FLAG 标志通知 MCU 处理数据。

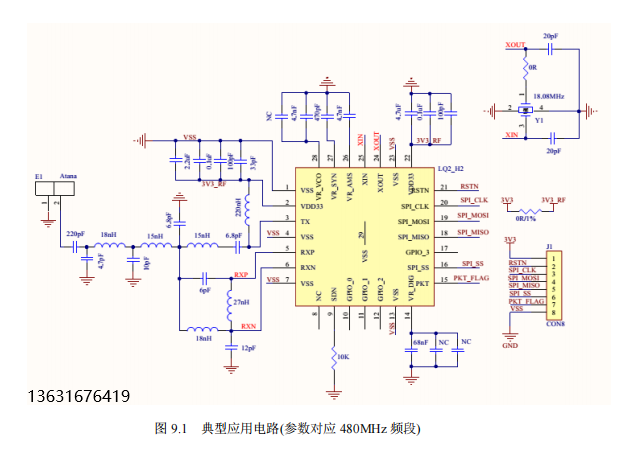

9.典型应用威廉希尔官方网站

审核编辑:汤梓红

-

SUB1GHz高集成度无线收发芯片-DP43012022-11-07 2417

-

A9508 笙科 1G ISM波段SOC无线收发带液晶驱动程应用 汽车防盗器2016-11-04 0

-

DP4301无线433M收发芯片智能家居芯片2022-10-09 0

-

SUB1GHz 高集成度433无线收发芯片2023-02-23 0

-

UM2010一款单片集成低功耗 Sub-1GHz 射频收发器芯片2023-05-19 0

-

2.4GHz无线收发芯片nRF24E1的原理及应用2006-03-11 3316

-

笙科电子发布具 LCD 显示驱动的 sub1GHz SoC 芯片2017-03-28 1838

-

单片集成收发机DP4301概述、主要特性及应用领域2022-06-08 1203

-

高集成度无线收发芯片的主要特性说明2022-06-13 1230

-

DP4301—SUB-1G高集成度无线收发芯片2022-07-21 1524

-

低功耗的单片集成收发机DP4301中文手册2022-08-01 354

-

DP4301— 国产 SUB-1G 高集成度无线收发芯片2022-08-30 1187

-

AiP4952A/B/C/D--2.4GHz高集成度无线收发芯片2022-10-28 740

-

DP4301—SUB-1G高集成度无线收发芯片数据参数2022-11-09 770

-

DP4301—SUB-1G高集成度无线收发芯片简介2022-12-13 1287

全部0条评论

快来发表一下你的评论吧 !