Codasip Studio 9.2.0版本发布 支持宏处理器以简化CodAL开发

电子说

描述

随着Codasip Studio 9.2.0版本的发布,Codasip Studio新版本通过扩展和优化等系列新功能赋能处理器设计自动化。

Codasip Studio 9.2.0 支持的新功能包括:

宏处理器

CodAL数组(array)

uRISC-V 2.0

模块中的流水线定义

模拟器保存状态和恢复状态

支持RHEL8(红帽企业Linux)

支持苹果MacOS

首先让我们来看一下CodAL功能中的宏处理器、uRISC-V 2.0和数组。

支持宏处理器以简化CodAL开发

Codasip Studio 9.2.0版包括一个宏处理器,这是一个强大的文本处理器,通过使用一组结构体来生成代码,简化了CodAL模型的编写。与C/C++预处理器相比,它支持的主要功能包括带参数的可调用宏、loops和复杂表达式等。

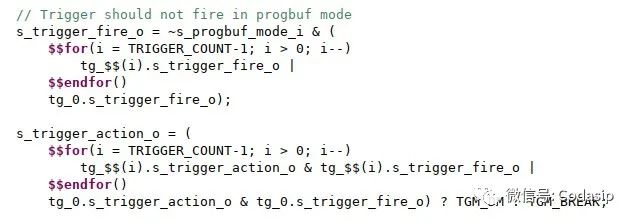

宏处理器简化了开发人员的工作,因为它避免了重复的工作和调用可能产生不必要开销的函数。下面的例子显示了宏处理器的用法之一。

宏处理器的使用实例

同时值得一提的是宏处理器也可以与其它语言和工具一起使用。

在CodAL中应对多线程应用程序的数组支持

Codasip Studio 9.2.0支持多线程内核寄存器和寄存器文件的数组。这些数组以每个线程为单位保存信息。数组大小与线程的数量相匹配,每个线程只包括其各自在数组中的索引,可供使用。

Codasip Studio 9.2.0版本同时也支持信号数组(多维数组除外)。只要数据类型一对一匹配,就可以支持数组到数组的赋值,即使资源类型不同。支持诸如将一个寄存器数组分配给相同数据类型的信号数组。

数组可以动态地进行索引。在loop中语义被扩展,所以它们可以与数组一起使用。

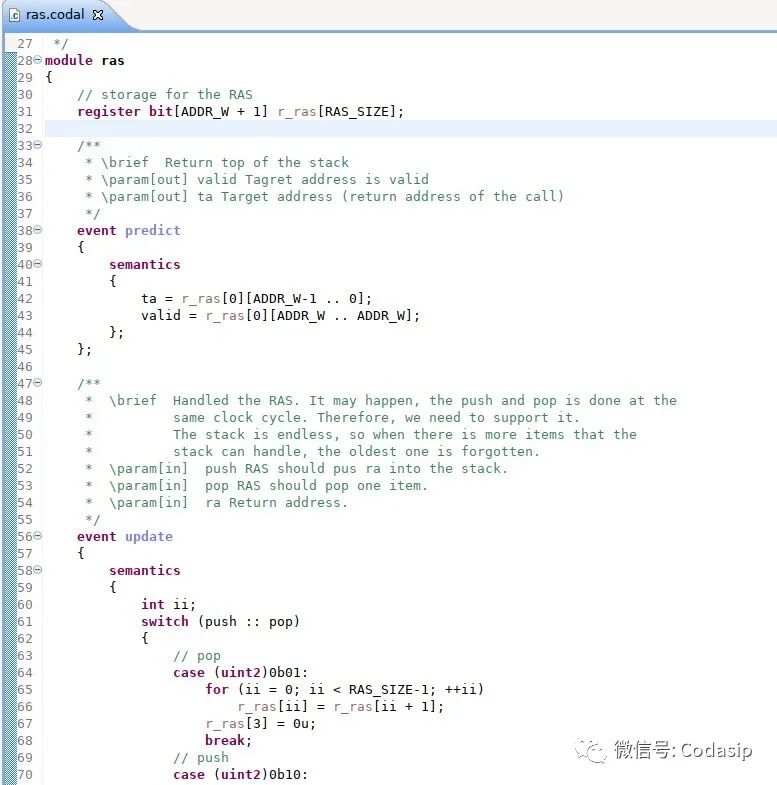

以下示例显示了架构资源的数组语法:

register bit[32] r_foo [32];

register_file bit[32] rf_foo [FOO_SIZE];

register bit[1] s_foo [ONE + TWO];

CodAL中的数组示例

uRISC-V 2.0实验支持

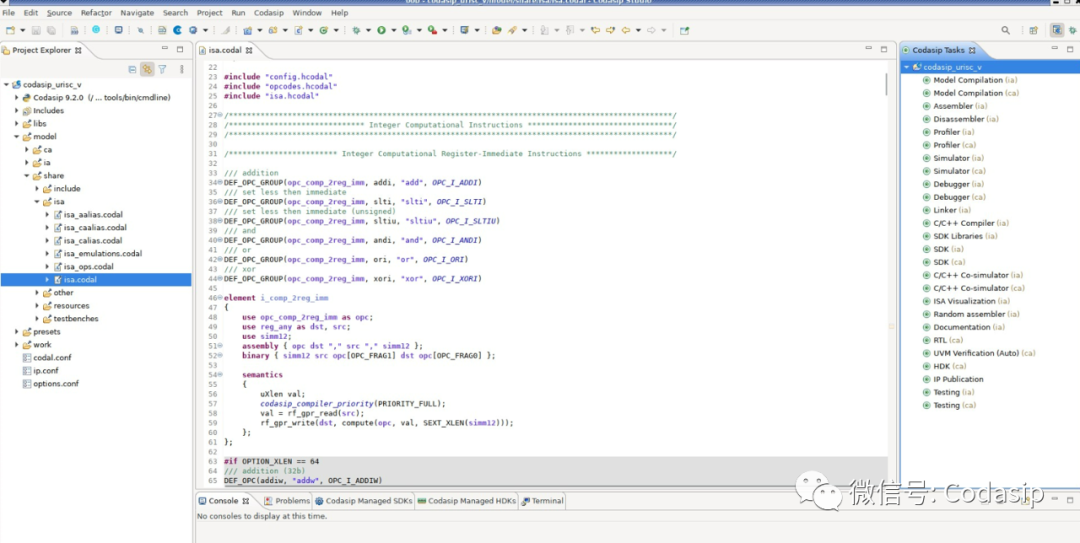

众所周知Codasip Studio 9.0版本首次支持用于5级流水线应用的uRISC-V处理器。uRISC-V是一个教程,允许用户在一个实时RISC-V实现上进行检查和学习。在Codasip Studio 9.2.0中,这个教程变成了uRISC-V 2.0,现在也可用于3级流水线应用。

这个功能扩展了Codasip Studio中用于科研目的或熟悉RISC-V架构的可能性。它包括尝试修改处理器,添加自定义指令扩展,以及在一个模型中优化性能,该模型的设计方法与Codasip RISC-V商业IP核相同。而该实现是一个简单的32位或64位3级流水线处理器,支持RISC-V I(基本整数)、M(整数乘除的标准扩展)、Zicsr(控制和状态寄存器指令)和Zifencei(栅栏指令)扩展,以及基于RISC-V标准的片上调试器。

Codasip Studio 9.2.0中的uRISC-V 2.0(Linux操作系统)

-

DevEco Studio 3.1 Beta1版本发布——新增六大关键特性,开发更高效2023-02-24 0

-

CPU-Z发布最新1.89版本 加入对中国兆芯处理器的支持2019-05-26 1322

-

Arm Development Studio 最新版本2020.0 发布!2020-04-30 5410

-

全新推出的Codasip Studio Mac版本为RISC-V处理器带来更多的差异化设计潜力2022-06-28 1173

-

SiliconArts在其光线追踪GPU中使用Codasip 7系列内核IP和Codasip Studio工具2022-11-03 745

-

基于Codasip的RISC-V处理器IP的光线追踪解决方案2022-11-04 575

-

HUAWEI DevEco Studio 3.1版本发布,配套ArkTS声明式开发全面升级2022-11-16 1211

-

Codasip宣布成立Codasip 实验室,以加速行业前沿技术开发和应用2022-12-09 619

-

Codasip成立Codasip实验室以加速行业前沿技术的开发和应用2022-12-09 3888

-

RISC-V处理器优化,不可依赖于放之四海而皆准的方法2023-05-31 1066

-

Codasip的系列RISC-V处理器助力RISC-V生态建设2023-07-03 739

-

Codasip推出全新高度可配置的RISC-V基准处理器系列2023-10-18 684

-

Codasip发布适用于定制计算的新一代RISC-V处理器系列产品2023-10-24 593

-

芯来集成开发环境Nuclei Studio 2024.06版本发布2024-07-15 723

全部0条评论

快来发表一下你的评论吧 !